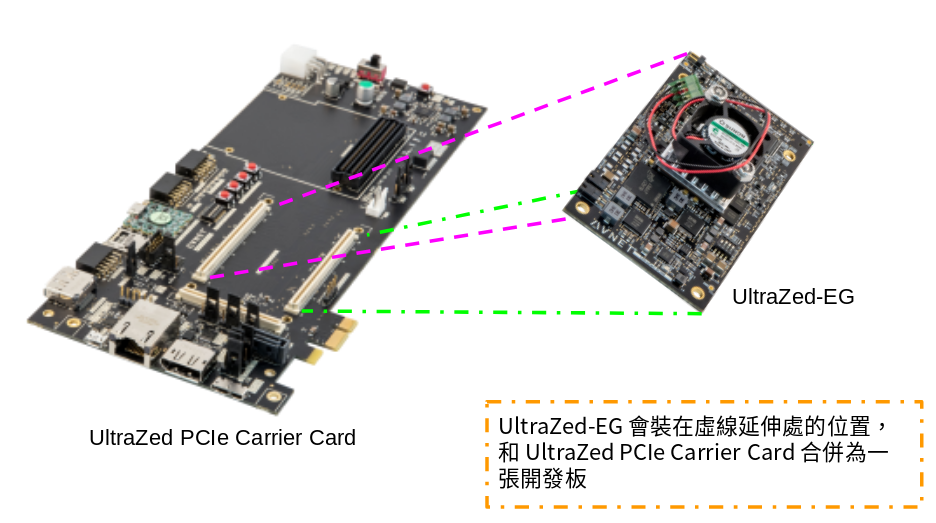

最近入手了 UltraZed-EG PCIe Carrier Card ,这是一款基于 UltraZed-EG 核心板进行延伸的开发板,和 Zybo Board 类似,是一款同时具有 Xilinx FPGA 并且包含了 ARM CPU 的开发平台。

但是不同的是,此开发板主板采用的核心为 Xilinx UltraScale+ MPSoC ,这一款具有 Cortex-A53 以及 Mali-400 的 FPGA 芯片,补足了 Zynq-7000 缺少 GPU 的不足。

为了了解这块开发板,我做了一些整理,让我们一样从硬件以及外围开始吧~

开发板概观

首先,这一整块开发板是 核心板 搭配 扩充板 组合在一起的产品,因此我们应该要先理解核心板的功能,再来看扩充板基于核心板的脚位,做了哪些延伸。

另外,要注意的是,核心板是可以被替换的,在我的文章中我使用的是 UltraZed-EG 。

UltraZed-EG

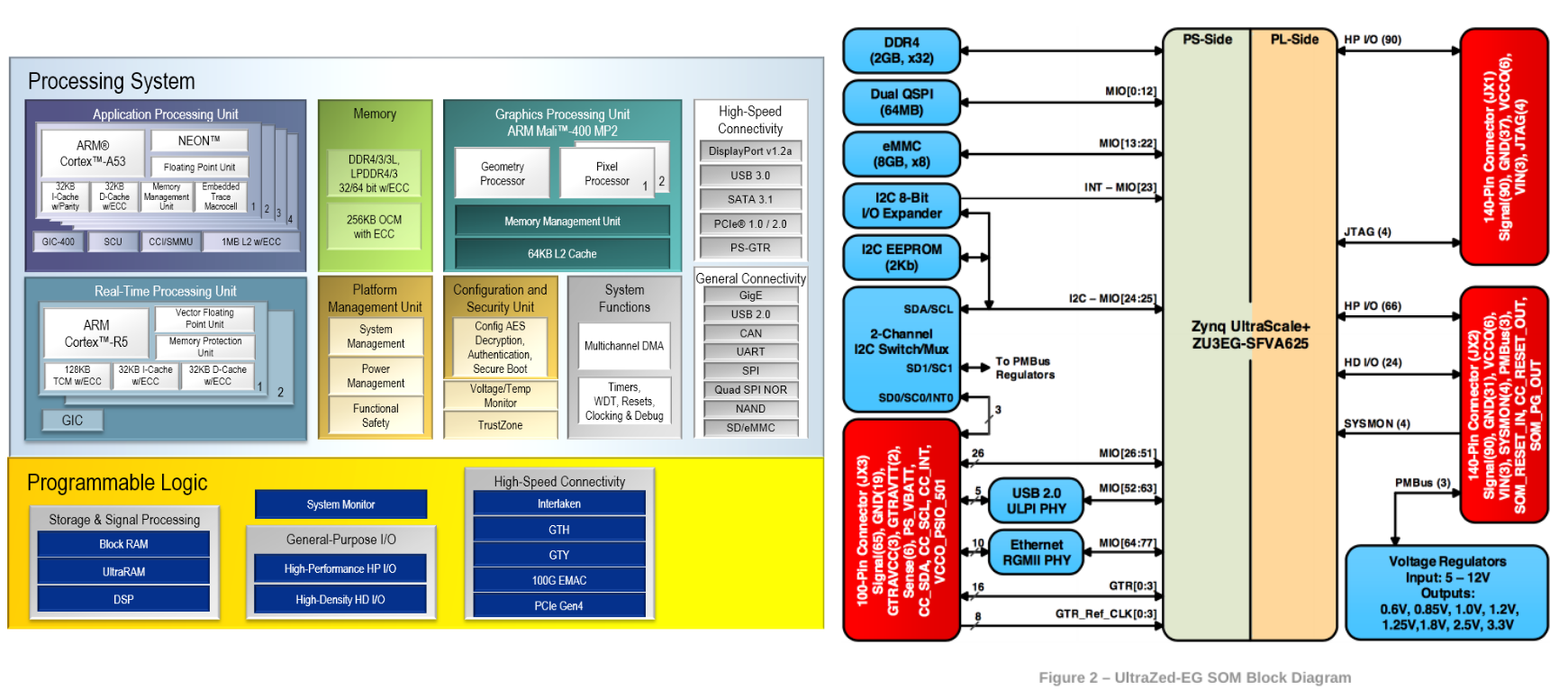

UltraZed-EG 是包含了 Xilinx FGPA 的核心板(System-On-Module, SOM),中间的核心芯片为 Xilinx UltraScale+ MPSoC 系列的 Zynq UltraScale+ EG (XCZU3EG-SFVA625) ,这一系列不同版本的芯片差异如下:

由于我的核心板是 UltraZed-EG,因此让我们直接看这一款的方块图,好来理解其有哪些功能:

我们可以看到 Zynq UltraScale+ EG 除了具有 ARM Cortex-A53 可以用来跑复杂的操作系统 (比如 Linux), 搭配 Mali-400 GPU 同时也可以跑具有 3D 效果的程序。此外,这颗芯片还具有两个 ARM Cortex-R5 可以让你用来处理对反应时间有严格要求(Real-Time) 的工作。

那假设我们使用 Linux 或是 Android 的话,要怎样让 Cortex-A53 的 Linux/Andriod 与 Cortex-R5 的 RTOS 沟通呢?这个时候就可以使用 Xilinx 这几年开源的 OpenAMP 框架来达到跨 CPU/OS 的通讯。

除了 ARM 的 CPU 外,因为这颗芯片同时也是 FPGA 芯片,当我们需要实做比如快速的图像处理、信息侦测的时候,就可以透过采用 FGPA 进行我们的图像处理/分析等功能,再将信息转发给 Linux/Android 去做后续的信息描绘。

简单的来说,这一款具有 SoC 的 FPGA 可以达成非常多的产品需求 (不考虑成本的话啦^^)

由于核心板 (System-On-Module, SOM) 的任务就是把 SoC 的接脚拉出,让开发者自行开发延伸板后将其合并就可以变成一个完整的产品,因此核心板本身有的外围很少,在这边我们只关注我们感兴趣的外围即可~

关于 UltraZed-EG, 可以透过 UltraZed-EG SOM Hardware User Guide 来更加了解其具有的功能。

SW2

首先,这块核心板最重要的就是用来设定开机模式的 SW2 这个指拨开关。整块板子的开机行为都会根据你的不同设定而改变,在后续文章里面,我大部分都会选用 SD1/MMC33 这种透过 MicroSD 卡来进行开机的模式。

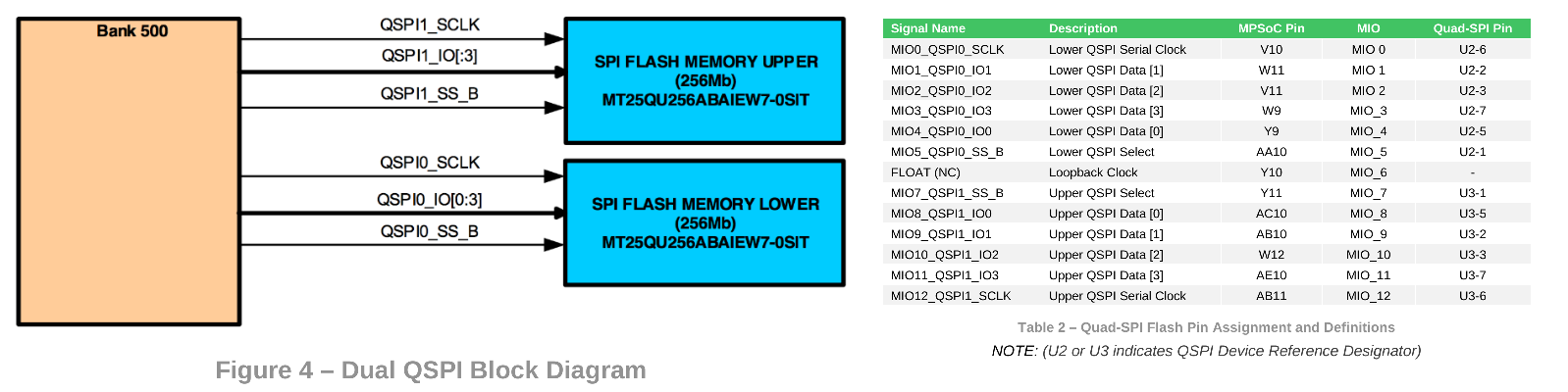

QSPI

核心板上有 2 颗 Micron QPSI MT25QU256ABAIEW7-0SIT NOR Flash, 不过我找不到相关的 datasheet….

我们可以透过 SPI 界面来将数据读写进这两颗 NOR Flash 去。

注意到如果你是要自己外接 SPI Flash 的话,也许最好看看 Micron Memory Support for Xilinx Platforms 的说明,里面会标注可以用于 Xilinx 平台上的 Flash 的型号。

eMMC

核心板有一颗 Micron MTFC8GAKAJCN-4M IT eMMC 芯片,大小为 8GB,在预设的情况下这个 eMMC 会被当作是 SD0 ,而扩充板的 MicroSD 卡则是会被当作 SD1

UltraZed-EG PCIe Carrier Card

本文使用的扩充板为 UltraZed PCIe Carrier Card, 为 AVNET 公司所出品的延伸板。由于 UltraZed-EG 本身只是将该 SoC 最基本的功能组装在一起,实际上需要使用比如 USB、PCIe 等外围的时候,就会需要透过延伸板来增加 I/O 的连接。

要了解这片板子,首先我们需要知道其 I/O 对应以及一些基本的外围,因此最好是先从 UltraZed PCIe Carrier Card Hardware User Guide 来开始看起。

概观

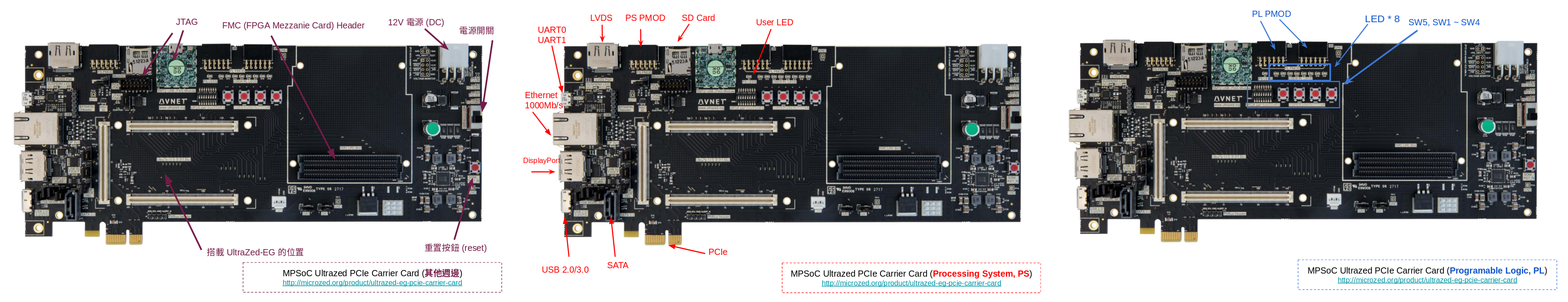

我们先从 UltraZed PCIe Carrier Card 的外观来了解这片板子的大概功能,之后再透过电路等信息来看要如何使用这片板子。

由于这块板子的外围可以区分为给 Cortex-A53 使用的部份 (Processing System, PS) 和给可程序逻辑区 (Programmable Logic, PL) 控制的两个区块,在搭配一些其他的外围,因此我们可以用以下这张图来看外围的使用以及分布。

了解了基本的外围后,就让我们来一个一个看吧~

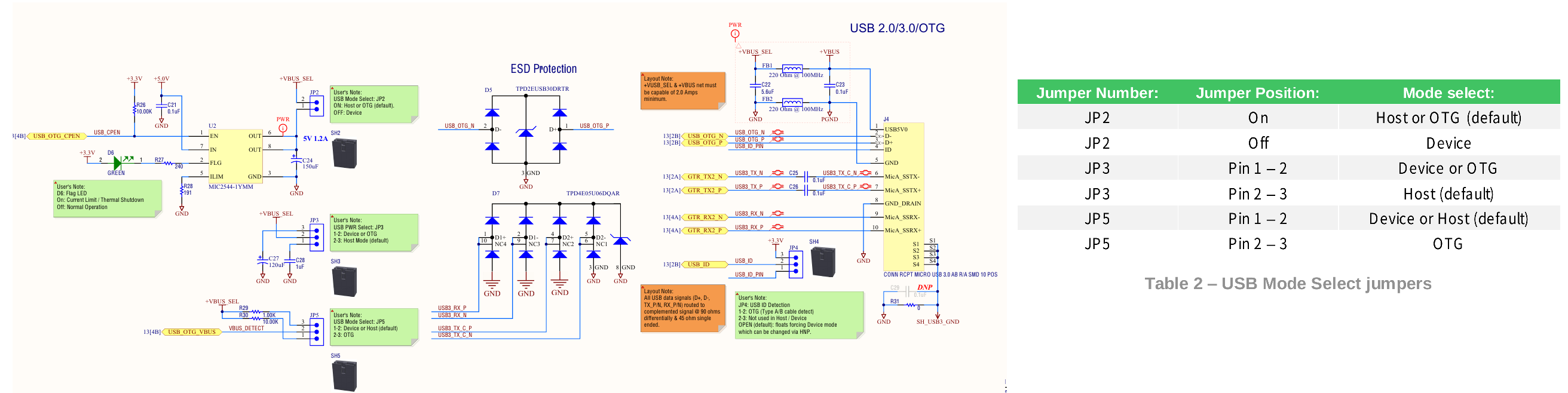

USB 2.0/3.0 (J4)

USB 位于 J4 的位置,为支持 USB 2.0/3.0 Host/Device 以及 OTG 的设备。我们可以透过调整 JP2, JP3 以及 JP5 来设定我们对这块板子上的 USB 的使用需求。

当设定 USB 为 OTG 的形式时,我们则可以透过修改 JP4 来指定 OTG 的运作模式

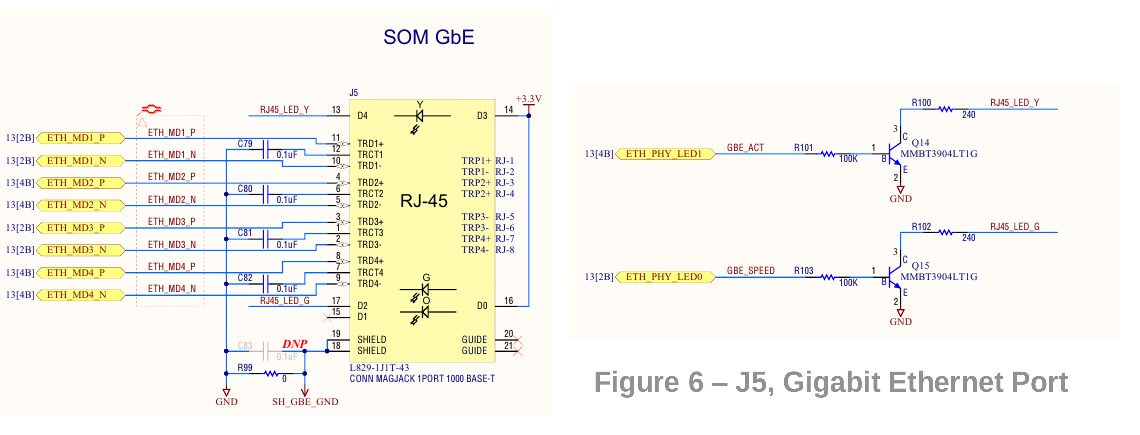

1000Mb/s 网络

由于 UltraZed-EG 已经做好了 MAC 和 PHY (DP83867) 的联机,因此 UltraZed PCIe Carrier Card 上的网络相关电路是直接将核心板的接线拉出,直接联机到 L829-1J1t-43G 这个 RJ45 连接器来用。

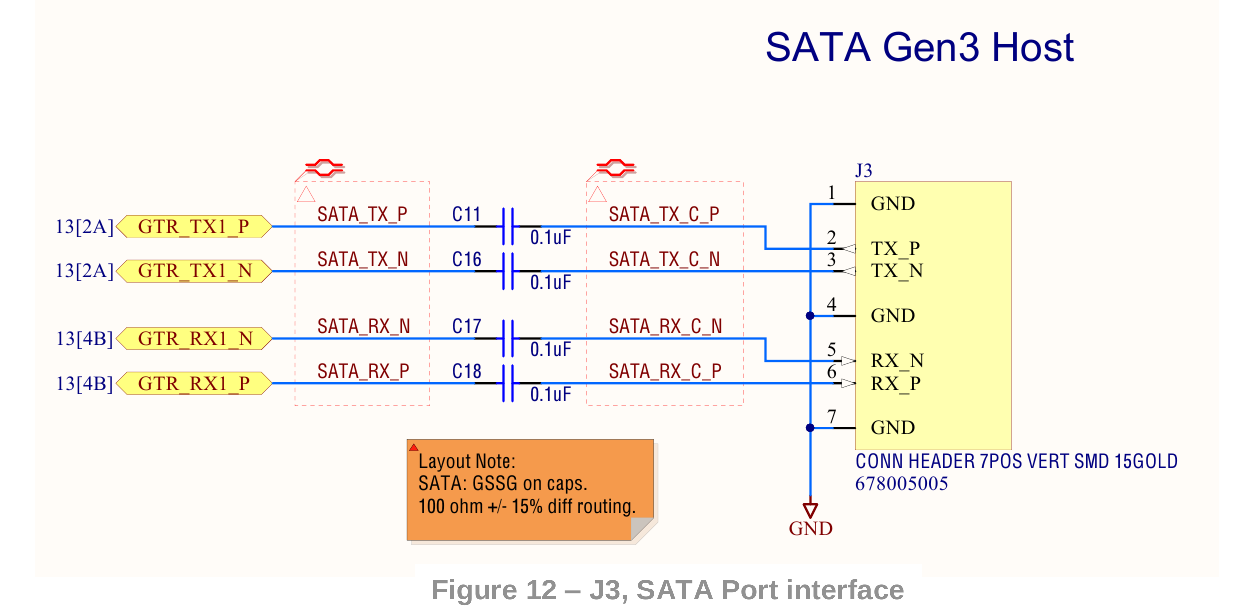

SATA3 Host

在 UltraZed PCIe Carrier Card 上有一个 SATA3 Host 界面连接到处理器系统(Processing Syste, PS),我们可以在这边接上外接硬盘扩充储存空间,该界面传输速度最快可以到达 6 Gb/s。

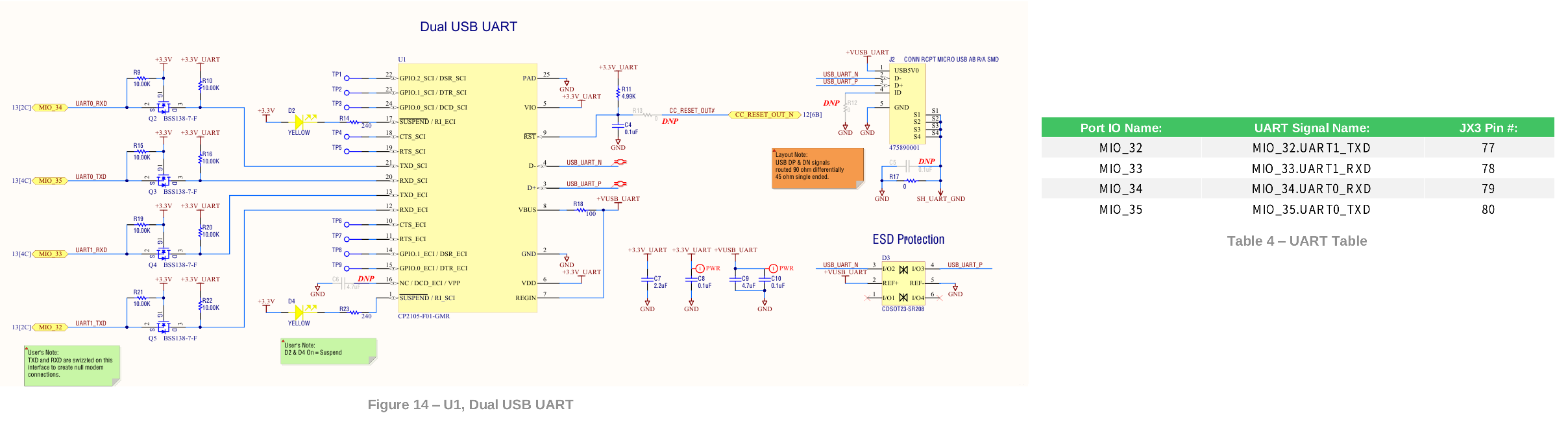

USB 转 UART (J2)

位于 J2 的 micro USB 接头,会经过 USB 转 UART 芯片 CP2105 而变成两个 UART 设备。

接到 Linux 上,会得到 /dev/ttyUSB0 和 /dev/ttyUSB1 两个设备,预设都是从 /dev/ttyUSB1 输出信息。

这两个 UART 对应到的 MIO (Multiplexed Input Output) 如下表所述:

从上图的 MIO 对应表可以发现到,之所以预设从 /dev/ttyUSB1 输出,是因为这块板子把 SoC 上的 ps_uart0 接到了 MIO_34 和 MIO_35 上,也因此实际上的 UART 对应表如下:

|

MPSoC PS |

MIO |

Linux |

|

ps_uart_0 |

MIO_32 (TX), MIO_33 (RX) |

/dev/ttyUSB1 |

|

ps_uart_1 |

MIO_35 (TX), MIO_34 (RX) |

/dev/ttyUSB0 |

总之如果有透过 UART 输出讯息,又奇怪怎样都看不到的话,两个 UART 都接收看看就对了 ^_^

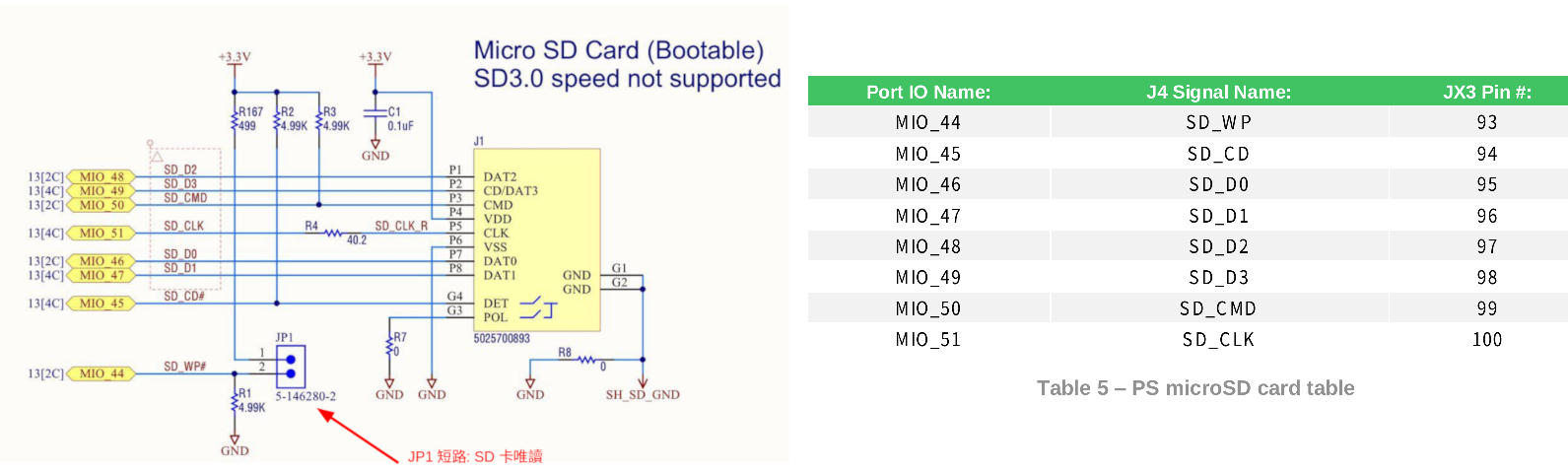

MicroSD 卡座 (J1)

位于 J1 的 MicroSD 卡座提供了让我们透过 SD 卡开机的用途,而附近的 JP1 短路的情况则是打开了 SD 卡的 write proteced 的功能。

注意到:当要透过 SD 卡开机的时候,别忘记修改主板上 SW2 的 DIP Switch

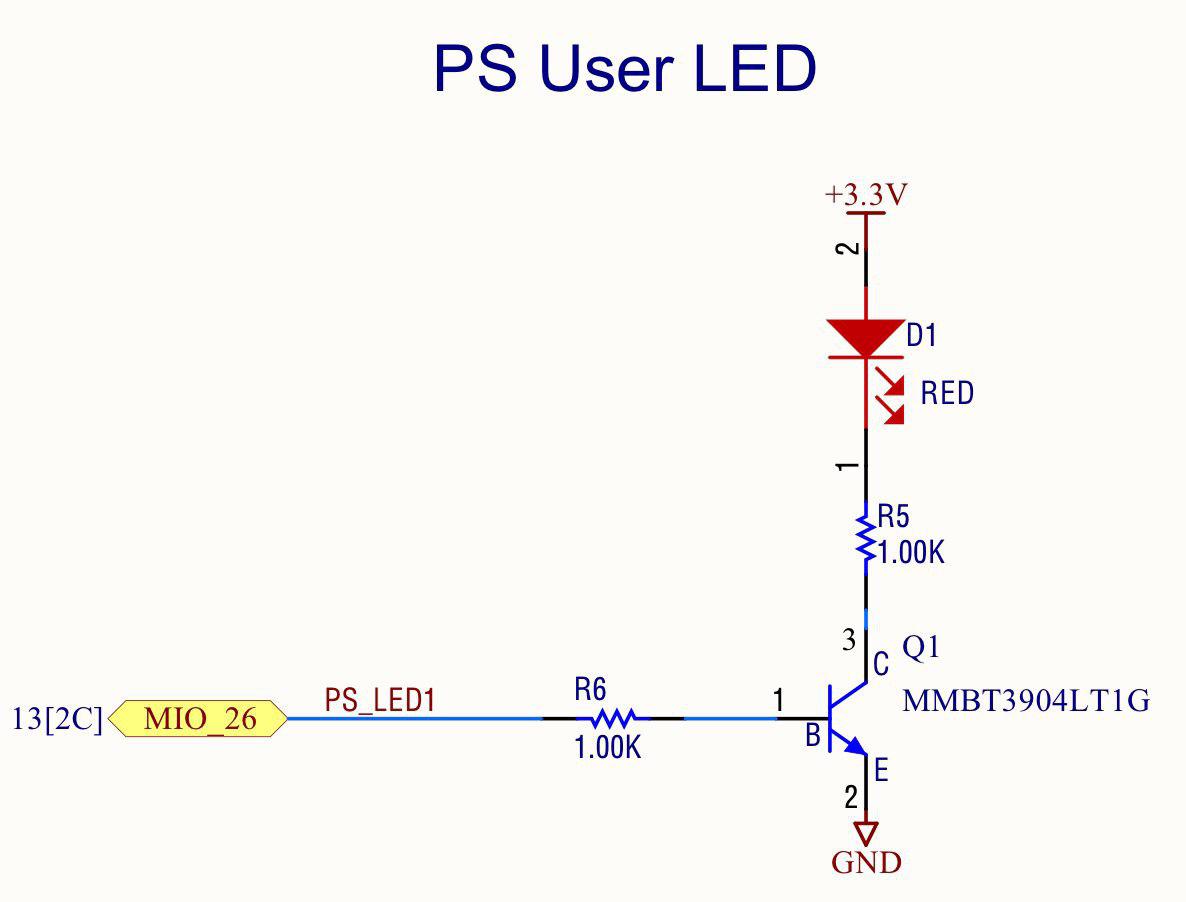

User LED D1

位于 D1 的 LED 是直接接到处理器系统 (Processing System, PS) 的 MIO26 上,这是这块板子唯一一个用户可以透过处理器系统(Processing System, PS)去控制的 LED。

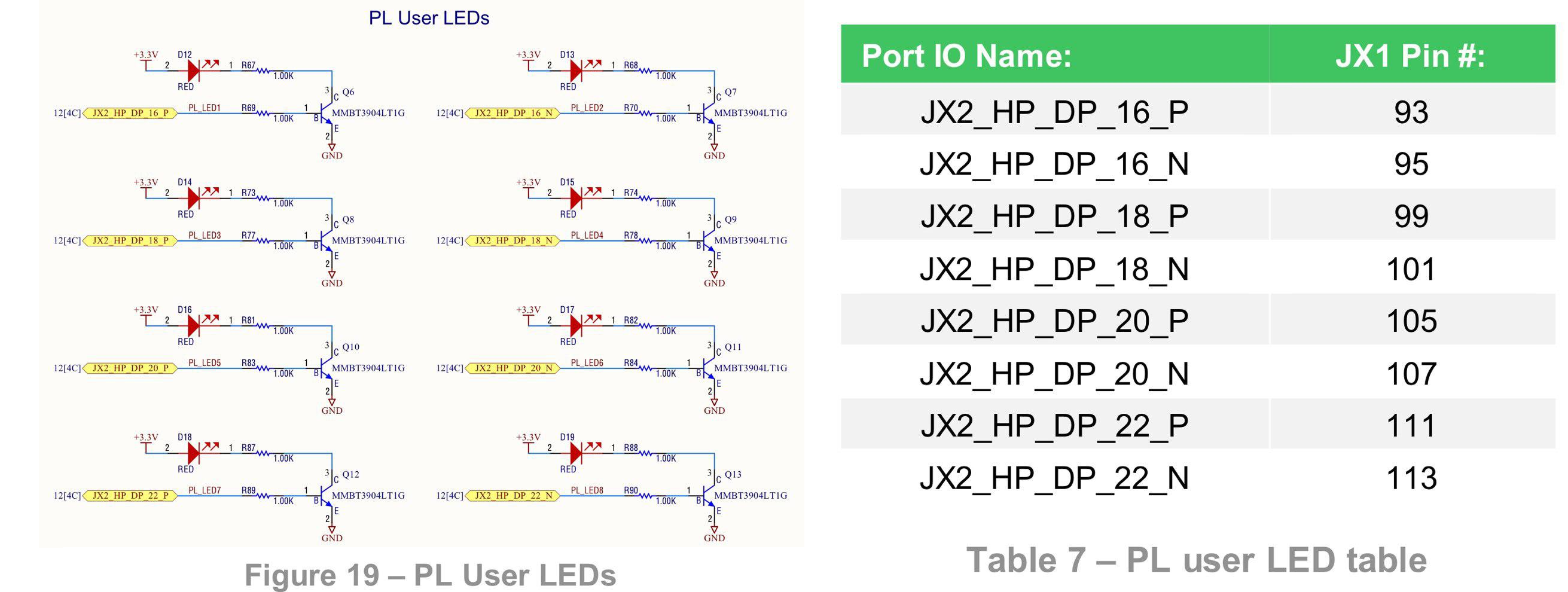

User LED D12 ~ D19

和 LED D1 不同,D12 ~ D19 的 LED 是位于可程序逻辑区(Programming Logic, PL)上,因此我们需要透过 AXI_GPIO 模块让 Cortex-A53 能够对其进行控制。

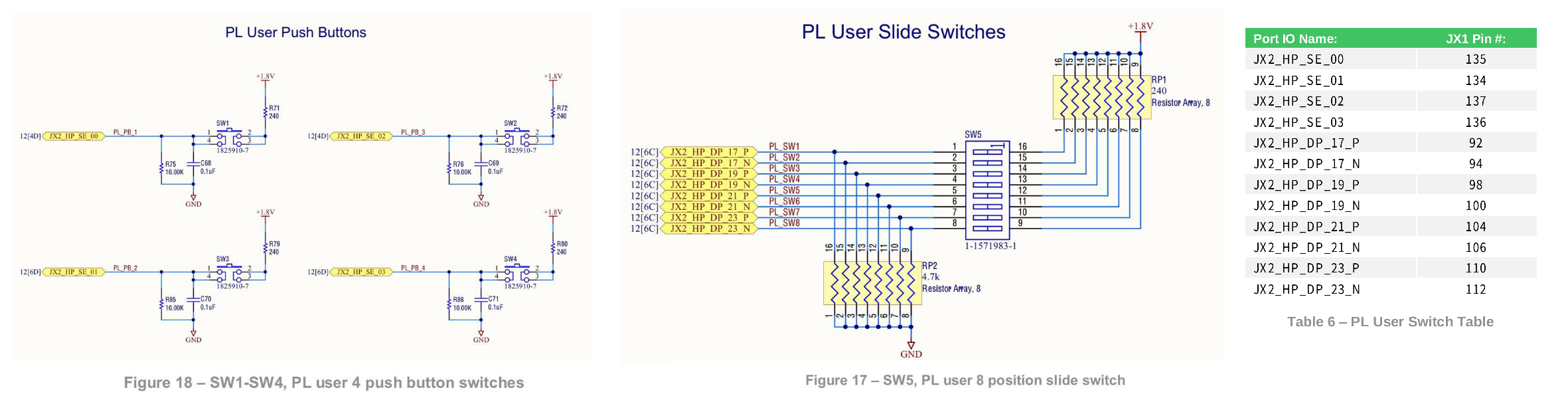

User Switch SW1 ~ SW5

除了 LED 外,这块扩充板内建了 4 个无段按钮 SW1 ~ SW4 以及一个 DIP Switch SW5 提供用户输入讯号使用,这几个输入源皆是接在可程序逻辑区 (Programming Logic, PL) 的位置,一般来说我们会透过 AXI_GPIO 模块让 ARM Cortex-A53 可以使用这些输入源。

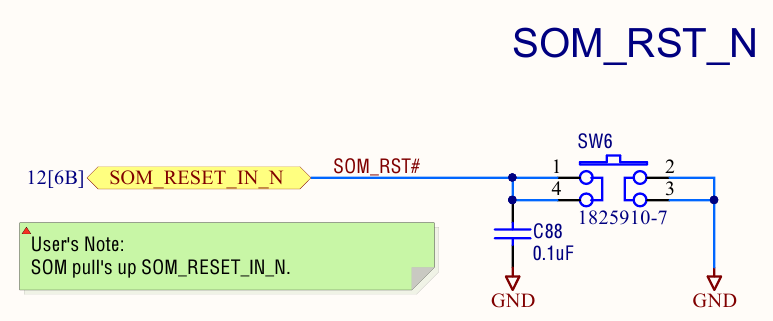

SOM Reset Input (SW6)

SW6 是用来重置 UltraZed-EG 用的无段按钮,和计算机上使用的 Restart 按钮功用一样,都是在不完全断电的情况下对 CPU 进行重置的动做。

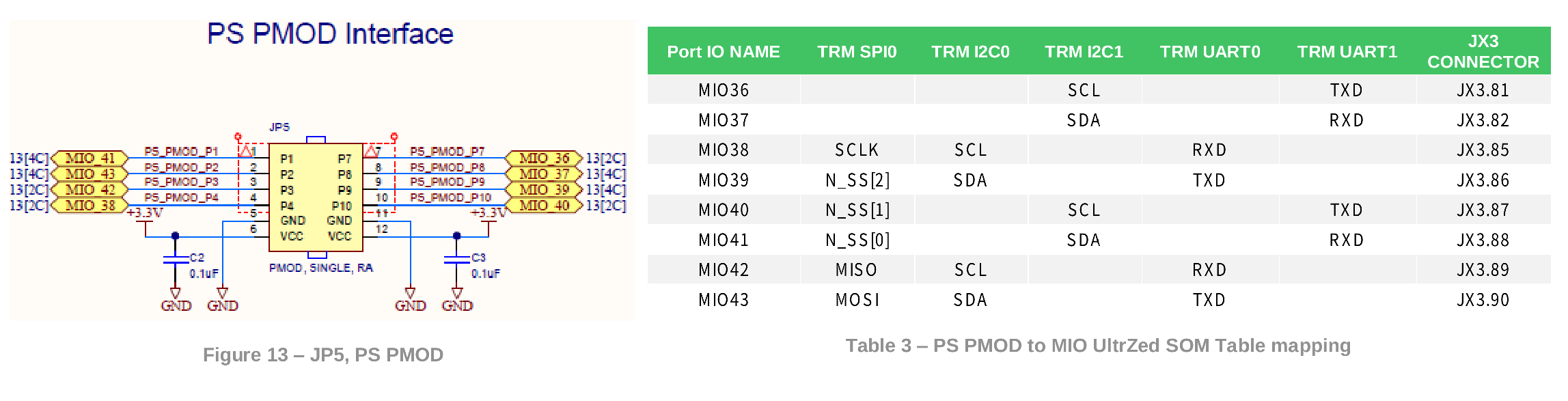

PS PMOD (JP5)

位于 JP5 位置的 PMOD 脚位是直接连接到 ZynqMP 的 MIO (Multiplexed Input Output) 脚位上的,因此这个 PMOD 是交由处理器系统 (Processing System, PS) 来进行控制。

由于 MIO (Multiplexed Input Output) 具有可切换的功能,因此这几只 MIO 可以根据用途变成 SPI、I2C、UART 等不同的接脚,详细信息请参考 ug1085 - Zynq UntraScale+ Device Technical Reference Manual 的 Chapter 28 对于 Multiplexed I/O 的说明。

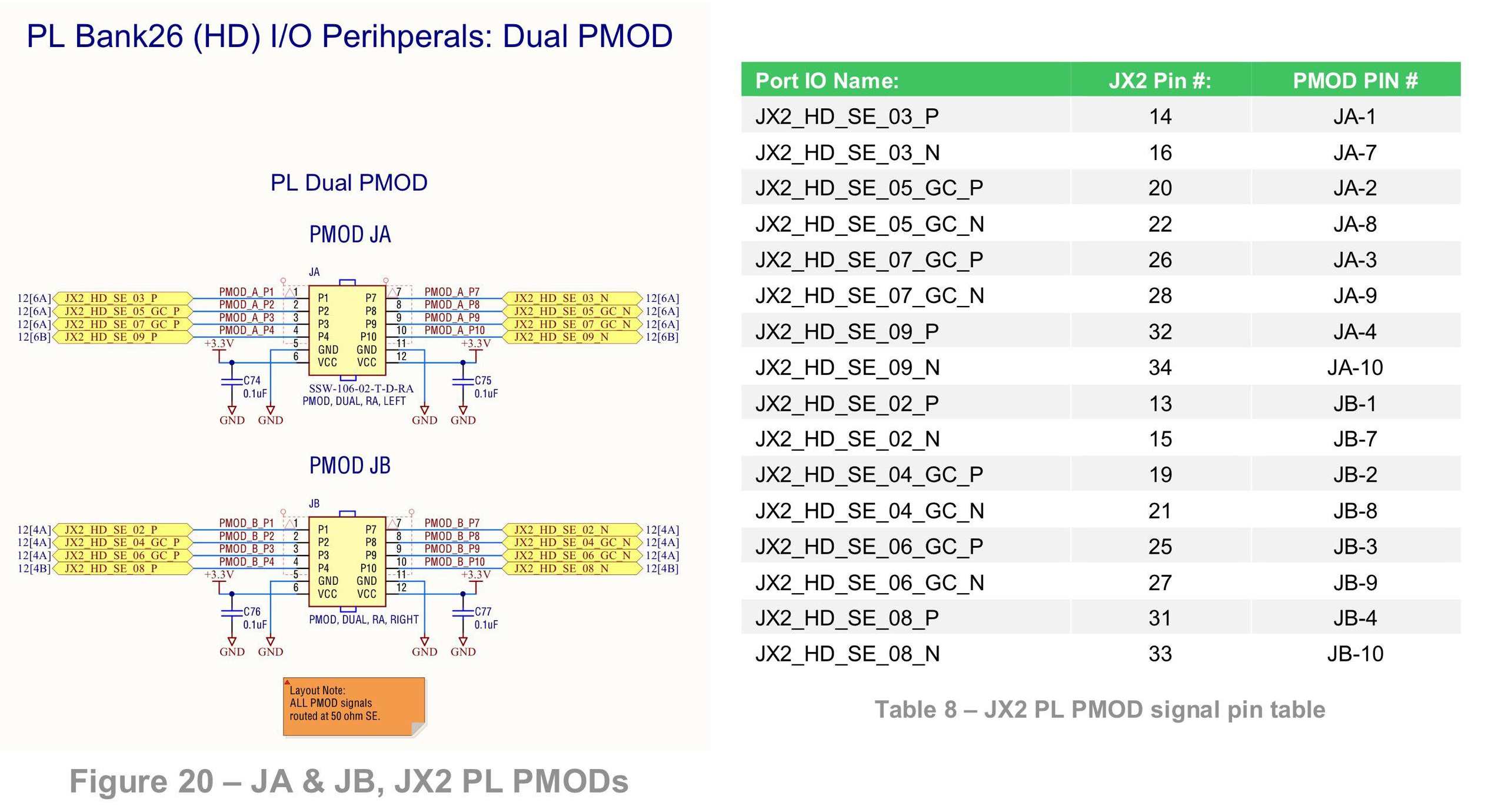

PL PMOD (JA, JB)

如果想要更有弹性一点的 I/O 的话,我们则可以透过 PMOD JA 和 JB 来对我们的输入/出进行控制。

PMOD JA 和 JB 是连接在可程序逻辑区 (Programming Logic, PL) 上的,也意味着我们可以透过 Verilog 等硬件描述语言自定义我们自己的模块,然后在透过遮些 PMOD 的脚位进行输出 (ex: 撰写 UART 模块并将 TX/RX 从 PMOD 导出)

注意到这边 I/O 的电压准位为 3.3V ,如果要连接更低/高电压的设备的话则需要做些保护才行。

FMC Header JX1, 2 CON1A-E

这块板子上有一个 FMC (FPGA Mezzanine Card) 界面,这是一种高速 I/O 界面,我们可以使用不同具有 FMC 界面的扩充板继续扩充这块板子的功能。

(有点类似 Altera DE2-115 上的 High Speed Mezzannie Card, HSMC 接口)

由于我并未有任何 FMC 界面的扩充板,因此这边就不对其做多余的介绍,只需要知道这个界面可以把一些 UltraZed-EG 并未用于这块扩充板的脚位拉出,因此我们可以再接上别的扩充板继续扩充。

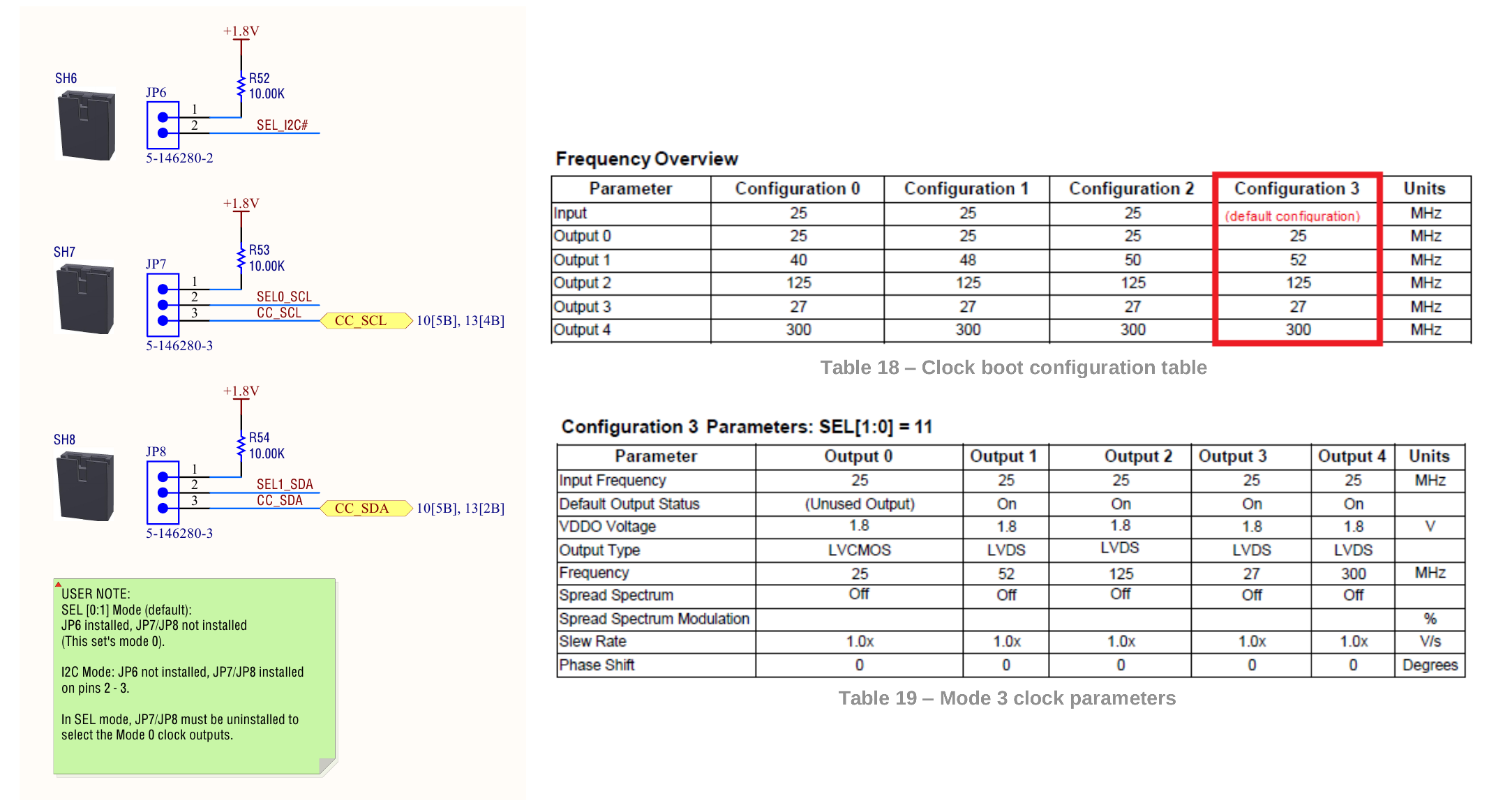

Clock Generator (U5)

位于 U5 的 IC 为 IDT 5P49V5935B521LTGI ,是一个频率产生器。该芯片透过 I2C 界面连接到处理器系统 (Processing System, PS),其中 I2C 地址为 0xD4 。

在这块板子上,此芯片主要用途是产生 LVDS (Low-voltage differential signaling) 界面所需要的频率,由于我没有 LVDS 面板可以用,因此这边也就只好先略过。

如果需要调整输出的频率,则可以透过 JP6, JP7 和 JP8 进行调整,具体请见 UltraZed PCIe Carrier Card Hardware User Guide.pdf

EEPROM (U6)

位于 U6 的 IC 则是 Microchip 24AA025E48T-I/OTCT-ND ,这是一颗具有 2kbit (256 bytes) 大小的 EEPROM,一样是透过 I2C 界面和处理器系统(Processing System, PS) 连接,其 I2C 地址为 0xA2 。

这颗 EEPROM 预设的设定是用来存取网络需要使用到的 MAC Address, 但是由于空间足够,因此我们也可以将一些设定放置到这个 EEPROM 去。

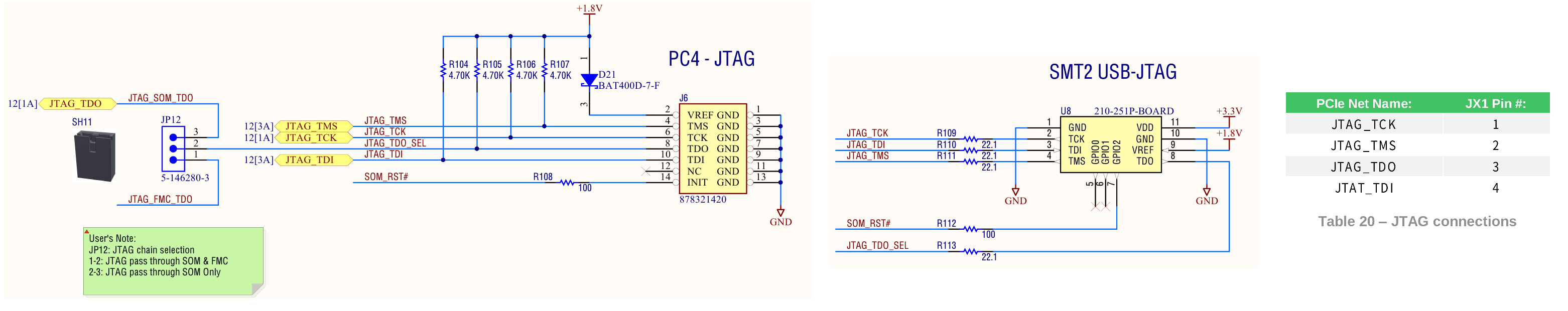

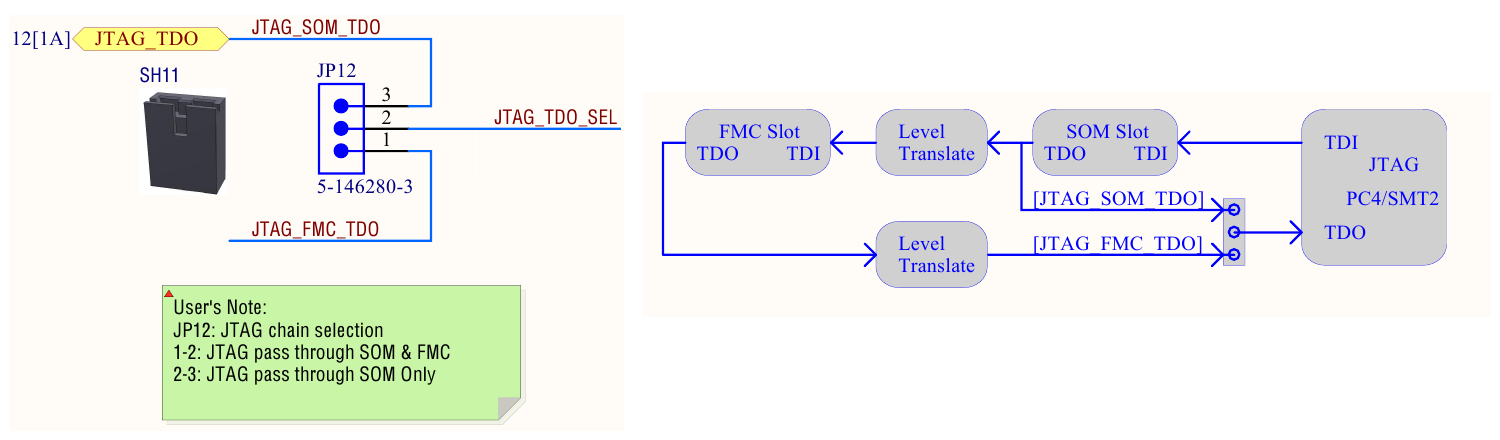

JTAG Debug Interfaces

这块板子具有两个 JTAG 界面,一个是透过 USB,另外一个则是传统的 JTAG 接脚 (14p 牛头母座)

我们可以透过 JP12 来选择当前的 JTAG 刻录模式,看是要对 SOM (UltraZed-EG 核心板) 使用,还是对 SOM 以及 FMC 界面使用。

预设为 JP12 的脚位 2-3 短路,这种情况下 JTAG 只会针对 SOM 进行运作。

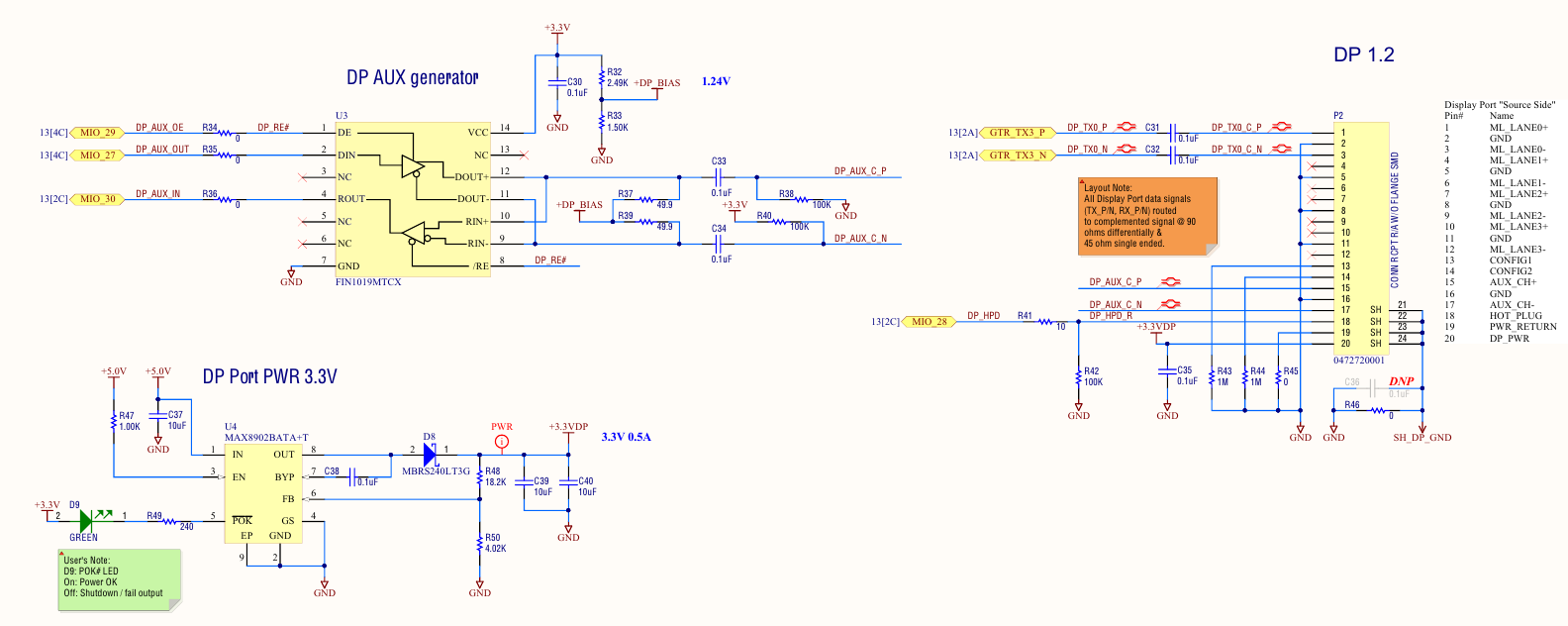

Display Port (P2)

UltraZed PCIe Carrier Card 虽然没有 HDMI 或是 VGA 可以输出画面,作为替代的则是加入了 DisplayPort 来作为图形显示的输出,我们可以将其接到支持 DisplayPort 输入的屏幕上来进行画面的显示,或是购买 DP 转 VGA的线材来透过 VGA 将影像输出。

注意到如果使用 DP 转 HDMI 的线材可能会因为 AR# 67462 的关系,无法透过 HDMI 将画面顺利显示出来,因此建议还是购买 DP 转 VGA 的线材比较好。

(我在这块板子测试 DP 转 HDMI 没有画面显示 Orz…)

PCIe Edge Connector (P1)

位于 P1 的 PCIe 接脚就是这块板子为何会冠以 PCIe 之名的理由。这个 PCIe 界面连接到了处理器系统 (Processing System, PS) 上的 GTR transceiver,这是一个可以支持速度高达 6.0Gb/s 的高速传输界面,并可以支持 PCIe, SATA, USB 3.0, SGMII 和 DisplayPort 等讯号传输。

在这边我们使用到的是 GTR[0] ,并将其定义成 PCIe Gen2 的界面, 因此速度会调整成 5.0Gb/s。

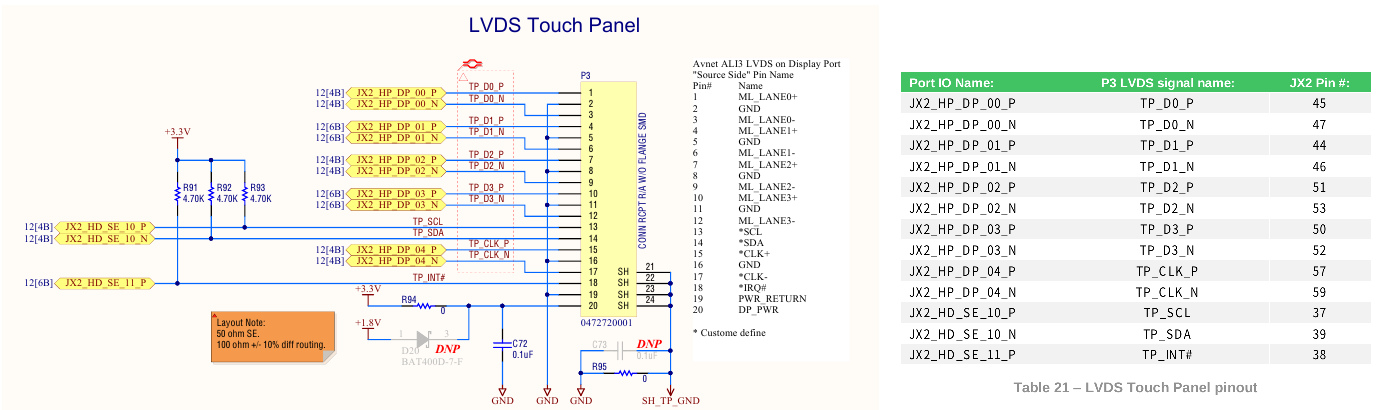

LVDS Touch Panel Interface (P3)

如果你有购买 AVNET 公司的 10-inch Touch Display Kit 的话,则可以将其接到 P3 这个位置上。

(不过我没有,所以这边一样不多做涉及)

延伸阅读

- DS890: UltraScale Architecture and Product Data Sheet: Overview.pdf

- Avnet UltraZed-EG SOM Designer's Guide.pdf

- Xilinx ZYNQ UltraSCALE+ MPSoC

- Working with the UltraZed SoM & PCIe Carrier Card

- UltraZed-EG SOM Hardware User Guide.pdf

- UltraZed PCIe Carrier Card Hardware User Guide.pdf

- ug1085: Zynq UntraScale+ Device Technical Reference Manual.pdf

- AR# 65463: Zynq UltraScale+ MPSoC - What devices are supported for configuration?

- FPGAとその周辺の电源についての动画でのサポート

文章来源:coldnew's blog