该目录包含各种硬件覆盖,用于加速不同平台上的神经网络。

背景

FPGA(现场可编程门阵列)是半导体器件,通过设计实现具有可编程互连的逻辑块阵列。与“硬化”设备(即CPU / GPU)不同,FPGA可以编程为实现用户所需的特定硬件设计。在设计硬件系统之后,必须使用二进制文件对FPGA进行编程。此过程通常称为配置。此外,在具有固定功能和动态功能的用例中,可以部分地重新配置FPGA。在数据中心环境中,FPGA通过PCIe连接到CPU,或者连接到外部片外存储器。鉴于上述假设,FPGA二进制文件可以划分为静态shell(Xilinx使用术语DSA)和动态overlay(Xilinx使用术语xclbin)。必须在加载任何overlay之前加载静态shell。 Xilinx的云合作伙伴已经加载了shell。如果这个解释看起来有点令人困惑,请不要过于担心。您需要知道的是,您需要选择最能满足您应用需求的overlay。它将由Python API加载。

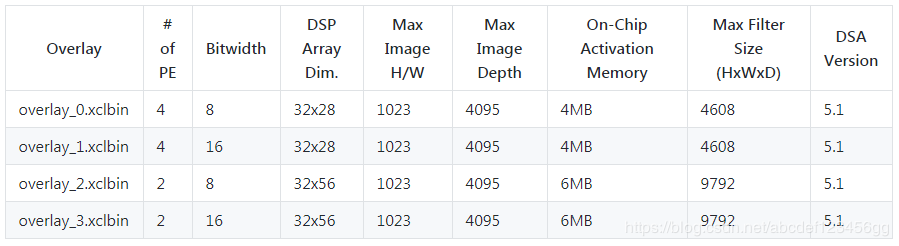

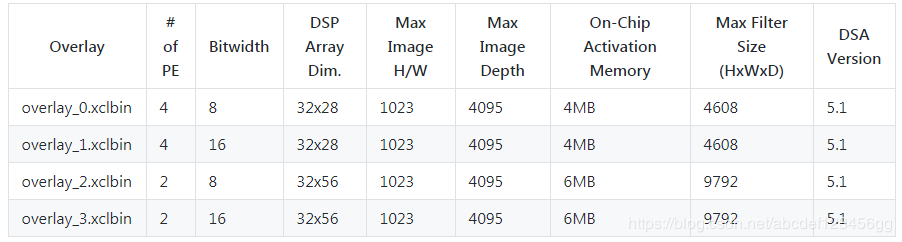

AWS 硬件 Overlays(XCLBIN)

NIMBIX 硬件 Overlays(XCLBIN)

VCU1525 硬件 Overlays (XCLBINs)

注意:目前,只有overlay_2和overlay_3可用。 你可能会遇到一个已知问题,速度降级。 这将很快更新(xilinx官方表示)。

overlay_0.xclbin:

这种overlay最适合best for高吞吐量应用。

它可以并行处理8个图像,它不支持具有非常大的滤波器的网络,例如YOLOv2

overlay_1.xclbin:

这种overlay非常适合great for高吞吐量应用。

它可以并行处理4个图像,并且它将保持精确度几乎等同于float32模型

overlay_2.xclbin:

这种overlay最适合best for高吞吐量应用。

它可以以2倍速并行处理2个图像,而32x28替代,较大的DSP计算阵列提供最小延迟,并且支持的较大滤波器尺寸可容纳大型网络,如YOLOv2

overlay_3.xclbin:

这种overlay有利于good for高吞吐量应用。

它可以以2倍速度一次处理1个图像,而32x28替代,较大的DSP计算阵列提供最小延迟,并且支持的较大滤波器尺寸可容纳大型网络,如YOLOv2,并且它将保持精度几乎相当于float32型号

本文参考: https://github.com/Xilinx/ml-suite/blob/master/overlaybins/README.md

---------------------

作者:战斗机上的飞行员

来源:CSDN

原文:https://blog.csdn.net/abcdef123456gg/article/details/83861239