FPGA开发过程中是免不了要用到移位寄存器的,传统的移位寄存器是通过寄存器(或者叫触发器)实现的,占用的是FPGA内部的逻辑资源,当要移位的次数过多时,自然会耗费更多资源。但是如果用LUT(look up table)查找表实现的话就很轻松了,LUT是通过提前存储下一张真值表来实现逻辑运算的,所以非常节省逻辑资源。常用的移位寄存器SRL种类很多,这里以16bit的SRL16E为例,说一说怎么使用它。

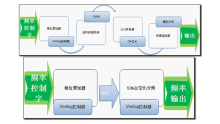

SRL16E的例化原语如下,输入是时钟CLK,使能CE,D,和四位输出位选择控制地址A3A2A1A0,输出是Q。首先要给出一个16bit的初始值,后面的移位就是按照时钟节拍对初始进行操作的,以代码为例,输入是D(0),意味着这16个周期内每个周期给序列最右边增加一个0,相应的每个周期对应的序列最左边的值也会被挤走。第0次移位得到0000000000001111,第二位是1,输出Q就是1,第一次移位得到0000000000011110,第二位是1,输出Q就是1,第二次移位得到0000000000111100,第二位是0,输出Q就是0,以此类推,输出依次是1,1,0,0,0,0,0,0,0,0,0,0,0,0,0,0,输出第几位由A3A2A1A0做地址控制(第二位输出对应0001),modelsim仿真示意图如下:

module srl(

input clk,

output rst

);

SRL16E #(

.INIT(16'h000F) // Initial Value of Shift Register

) SRL16E_inst (

.Q(rst), // SRL data output输出16'h000F第[a3:a0]位的值,总共输出16次(使用的是SRL16E),D(0)从右(最低位)进,16'h000F的第2位输出

.A0(1'b1), // Select[0] input

.A1(1'b0), // Select[1] input

.A2(1'b0), // Select[2] input

.A3(1'b0), // Select[3] input

.CE(1'b1), // Clock enable input

.CLK(clk), // Clock input

.D(0) // SRL data input

);

endmodule

---------------------

作者:YisongLee

来源:CSDN

原文:https://blog.csdn.net/Lee412726/article/details/80614657