时序约束向导

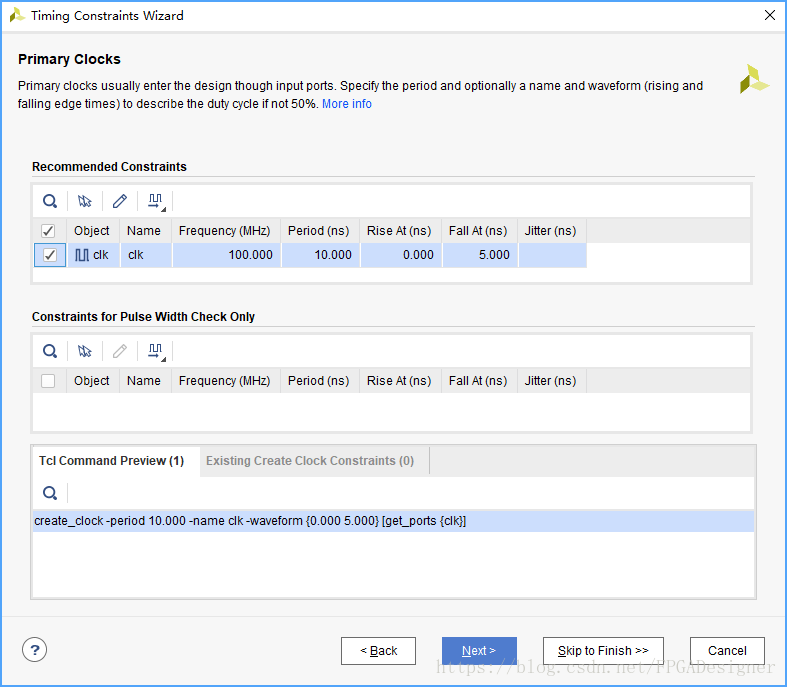

打开综合设计或实现设计后,在Flow Navigator中点击Open Synthesized/Implemented Design目录下的Constraints Wizard可以打开时序约束向导(会要求选择一个target约束文件)。弹出如下窗口:

利用该向导可以快速地完成时序约束。时序约束向导会分析网表、时钟网络的连接和已存在的时序约束,给出一些缺少的时序约束的建议。时序约束向导的前11页按照3个目录给出不同种类的时序约束,下表给出一个大致介绍:

上面的每一步都可以根据约束向导的建议进行约束,如果执意不想约束该对象,取消勾选对象前的复选框即可。如果取消勾选了某条建议,则后续步骤中的一些缺少的时序约束不会被检测出来。比如跳过了创建主时钟的步骤,约束向导便不会识别出与此时钟相关的时序约束。

最后是一个Summary界面,给出了前面创建的所有约束,可以点击查看约束的详细信息,退出约束向导后在时序约束窗口中也可以看到新约束。点击Finish结束约束向导时,还可以勾选如下选项创建相应报告:

时序约束向导不会推荐会引进不安全的时序分析的约束,也不会修复当前将设计导入内存时已经存在的不恰当约束。因此如果使用向导之后,运行时序检查或DRC检查时仍然存在一些时序问题,通常都是由源XDC文件中已经存在的约束问题引起的,设计者需要自己解决这些问题,而不是试图依靠约束向导来解决问题。

在向导中编辑约束

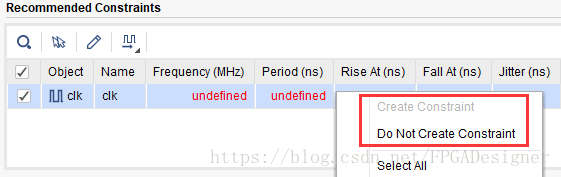

上文已经提到过,可以通过对象前的复选框来选择是否创建该约束,该功能也可以通过选择对象->右键->Create Constraint或Do Not Create Constraint实现。如下图所示:

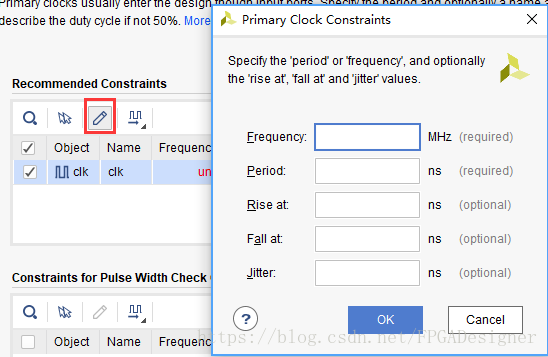

缺少的值显示为红色的undefined,如上图中的Frequency和Period,双击可以设置值。如果希望同时编辑多个约束,则选中所有约束相同的行,点击Edit Selected Rows按钮,在弹出的窗口中同时编辑所有对象的约束值:

使用Back和Next可以在不同的约束界面之间进行切换,但是如果没有处理当前界面的所有缺少的值,便无法切换到下一个约束界面。再次强调一遍,时钟约束向导无法编辑已经存在的时序约束,只会创建新的约束。

时序约束窗口

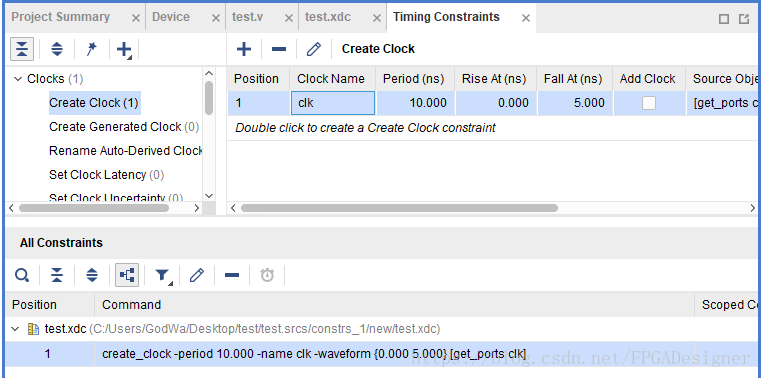

如果想要编辑已经存在的约束,在Elaborated设计阶段,只能通过修改XDC文件实现;而在综合设计或实现设计阶段,还可以通过时序约束窗口来实现。在Flow Navigator中点击Open Synthesized/Implemented Design目录下的Edit Timing Constraints可以打开时序约束窗口:

时序约束窗口下方的All Constraints按照XDC文件和Tcl脚本中的顺序,或者在Tcl控制台中输入约束的顺序显示时序约束。如果某些约束不能在该窗口中编辑,则会标记为Nodit,前面有一个 的图标。

的图标。

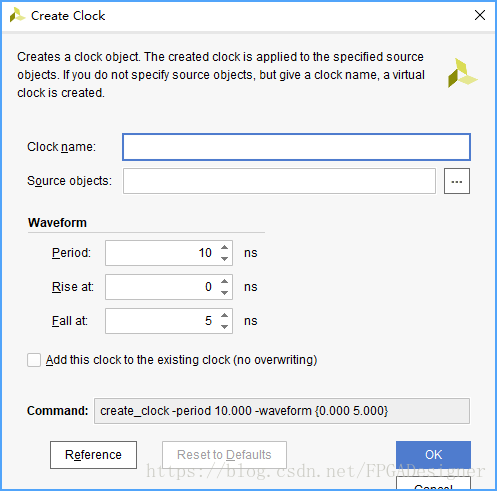

时序约束窗口中显示了所有存在约束的详细信息,并且可以直接编辑。左边以目录的形式列出了各种约束类型。右边双击最后一行可以创建当前所选类型的一个新约束,弹出窗口中完善约束信息。点击OK即可将约束在内存中应用,但是只有点击Save Constraints后才会保存到XDC文件中。如创建一个新的时钟约束,弹出窗口如下:

另外IP核约束是无法编辑或删除的,如果非要这样做,可以禁用IP核发布的约束文件,将其中的内容复制粘贴到用户XDC中,即可进行编辑操作。