本文档系列是我在实践将简单的神经网络LeNet-5实现到Xilinx 的zynq-7z035的FPGA上遇到的问题和解决方法。

本文档重点探讨vivado软件的使用。

完成此过程可以参阅的文档有

UG892: Design Flows Overview 设计流程概览

UG895:System-Level Design Entry 系统级设计入门

UG895:Using the Vivado IDE 运用vivado集成设计环境,可能后两个更加着重探讨软件的使用。

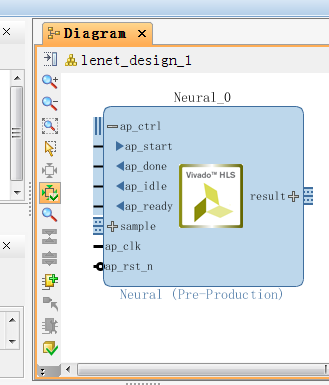

背景:我们用vivado HLS对相关软件生成了相应的IP core,现在需要对IP core进行系统集成,形成完整的设计。

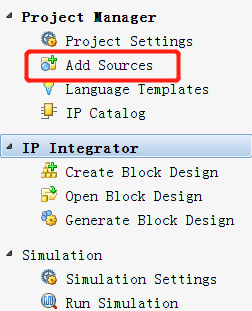

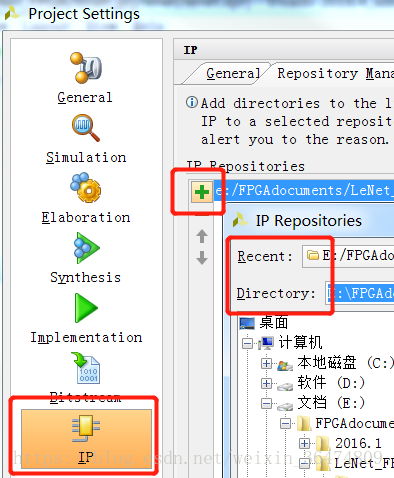

一、添加之前生成的IP core

之前一直以为是在add sources中加入IP core,后来发现加入之后IP core在相应的IP catalog中找不到。可能add source有其他的意思。IP core是在project setting中加入的。

在block design中加入

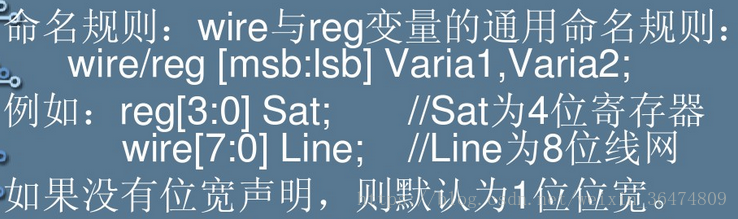

经常在图中看到变量[31:0]这样的东西,这个描述是什么意思呢?

二、搭建系统

1.DMA基础知识

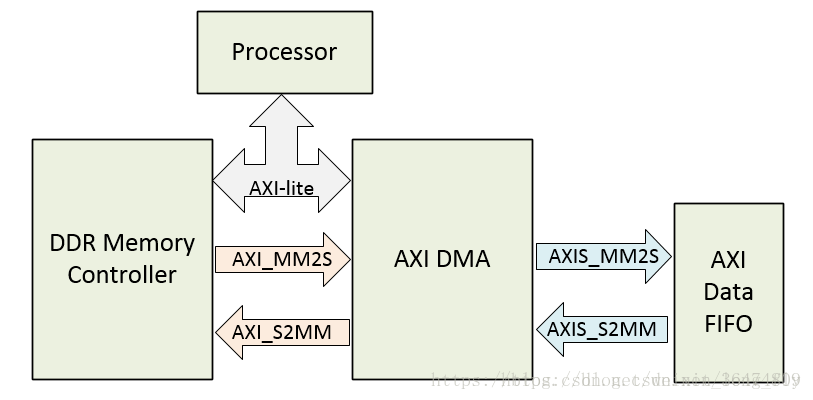

搭建系统中有一个重要的因素是DMA:(Direct Memory Access),即直接存储器存取,是一种快速传送数据的机制。数据传递可以从适配卡到内存,从内存到适配卡或从一段内存到另一段内存。

为了实现相应的系统,我们该把什么样的IP core加入block?加入block之后线如何连接?

下面几个可能为重要的IP core

可能有用的文档有UG895:System-Level Design Entry 系统级设计入门

UG895:Using the Vivado IDE 运用vivado集成设计环境

2.创建HDL wrapper

我们只创建了一个PS,并且没有用到相应的fabric,但是zynq PS已经与Gigabit Ethernet PHY, the USB PHY, the SD card, the UART port and the GPIO相连接,所以我们仍然有许多工作可以做,比如在这个PS上运行linux,或者运行裸程序。

三、连接相应的IP

DMA (Direct Memory Access)让系统将数据从一个部分传到另一个部分,可以将任何一个data producer传输到memory,也可以从任何一个memory传输到data consumer。

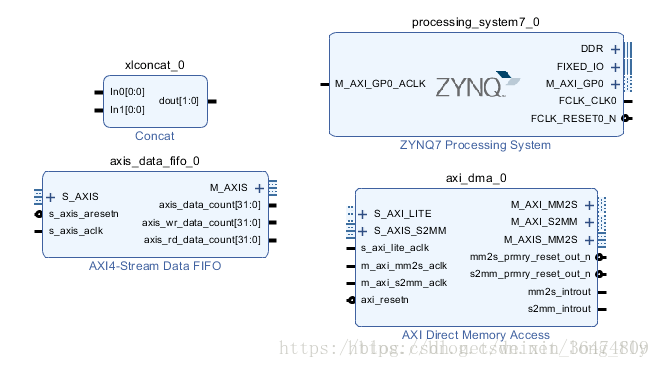

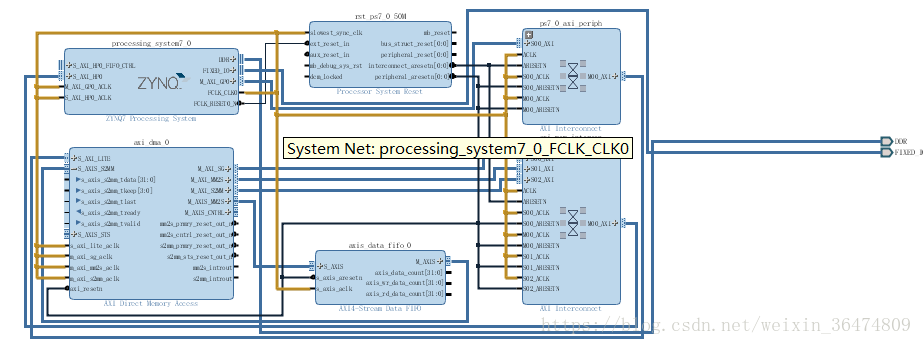

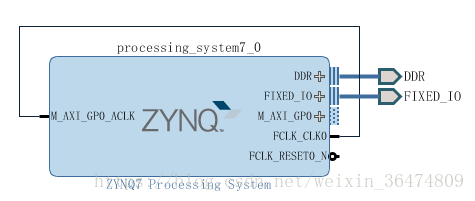

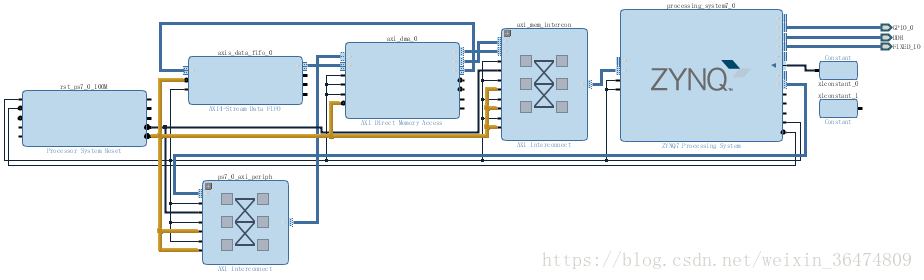

1.点击create block,先点添加IP,把AXI derect memory access和zynq processing system加入,然后点击相应的block automation和connection automation,系统会自动添加相应的IP块进行相应初步的IP连接。

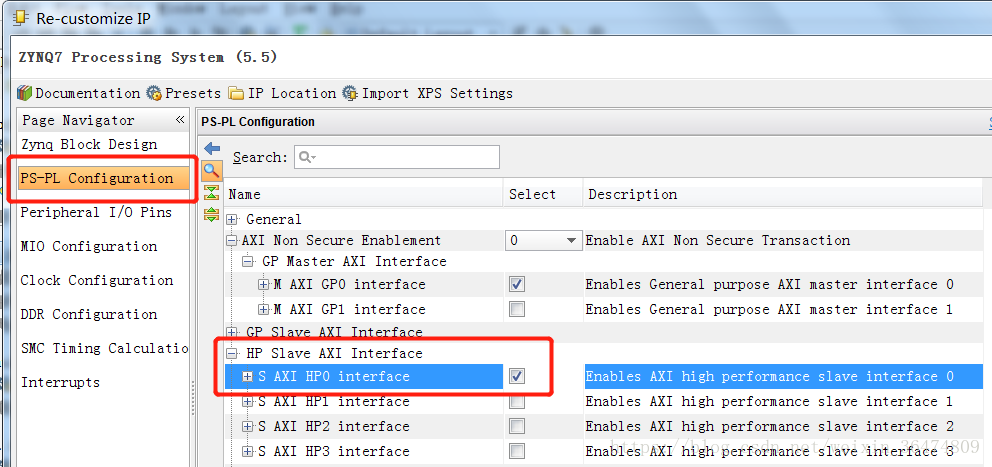

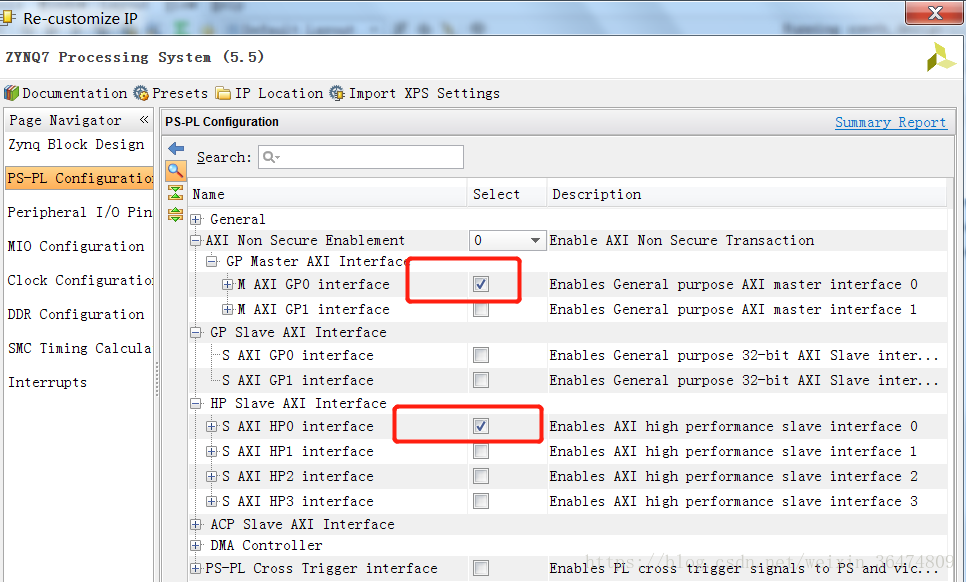

2. 下面需要在PS上使能一个高性能的AXI slave interface,我们需要在ZYNQ processing system双击IP core使这个管脚出来。双击ZYNQ processing system,然后点击PS-PL configuration,然后点击HP slave Interface,勾选第一个S_AXI_HP0_interface,以使能这个管脚。(HP的意思就是Hign-performance,意思是高性能线。PS的意思是processing system,PL为FPGA板子,即为FPGA)

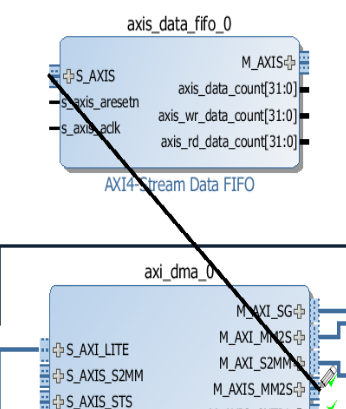

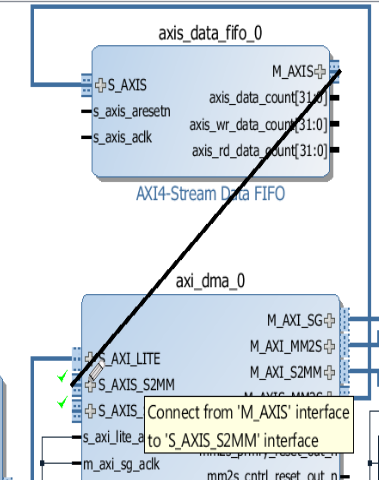

3.加入FIFO,然后把FIFO与DMA进行连接

fifo的入连DMA的MM2S

fifo的出连DMA的S2MM

进行了下面两个连接之后,把areset连接到大家的reset上,把clock连在clock上。连完之后就是下面这种结构。(FIFO只是一个常见的IP core,它有相应IPcore的输入输出,但是没有运算,算是最简单的IPcore,所以用FIFO来代表IP core)

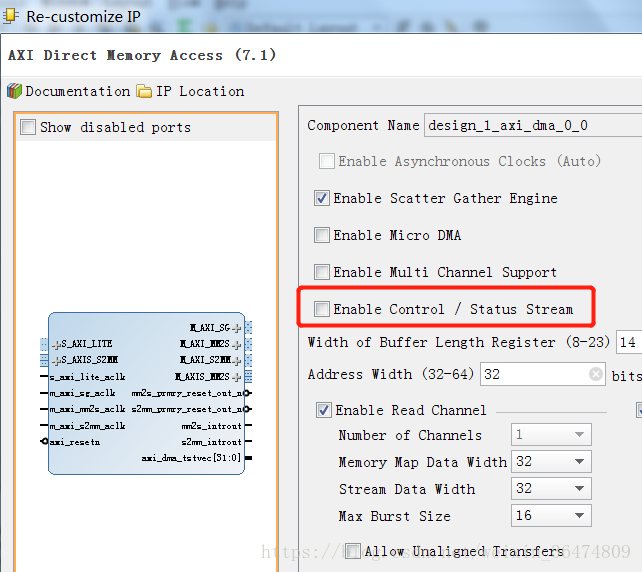

4.移除AXI stream statu管脚和DMA的control ports管脚

在设计中这两个管脚是不需要的,所以我们可以移除他们。双击DMA块,然后取消勾选enable control,我们能看到对应于图上的control管脚们都没有了。

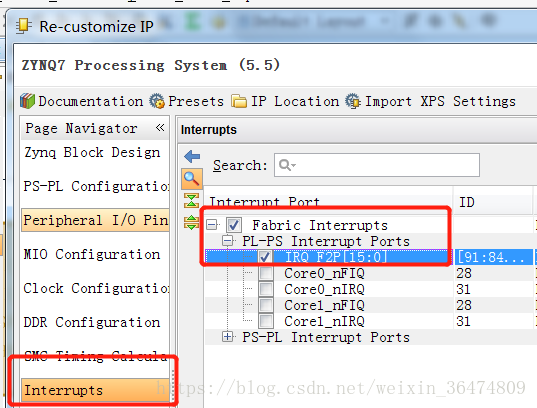

5.连接DMA interrupt与PS

首先双击点进去processing system的块,然后在interrupt选项里面勾选fabric interrupts中IRQ F2P选项。

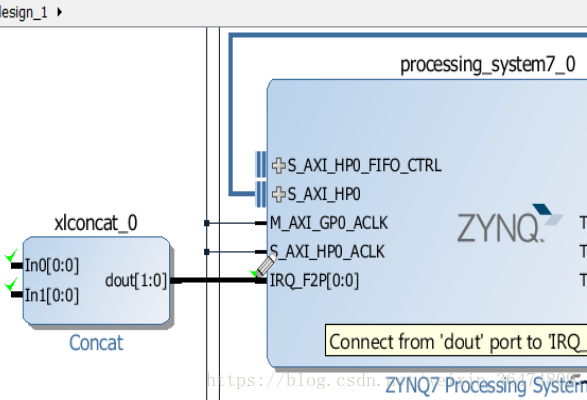

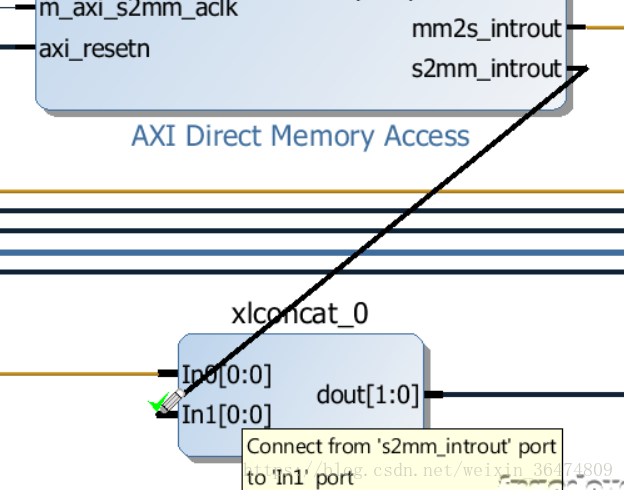

加入叫concat的IP块,然后按下图连管脚

四、validate与export

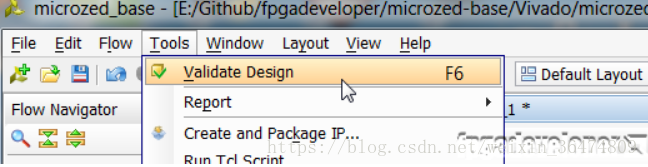

1.点击validate,运行完之后会显示success,no error等信息,

2.可以点击regenerate layout icon来进行重新布局

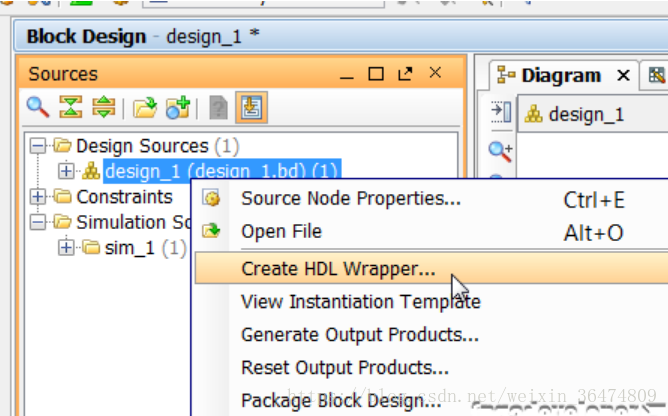

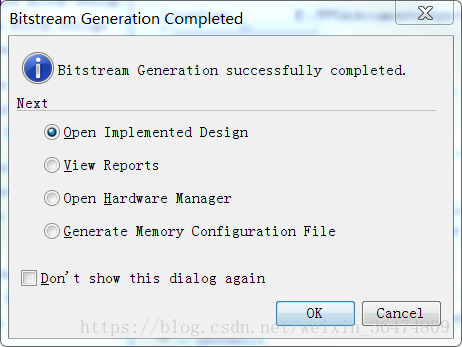

3.点击generate bitstream,生成相应的比特流(生成比特流之前应当生成HDL wrapper)

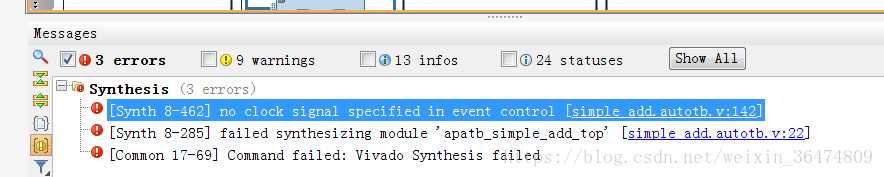

失败了,

教训1:项目的用的板子的名字任何地方都要一致。

教训2:要设置相应的clock。

出现这个错误是由于对clock用的不熟并且不知道每一个连接的意思。因此我们重复进行上面的步骤试一下,重复几次之后还是不能进行相应的系统设计。

为了解决连线等等问题,我们需要能看懂连线,所以我们查阅相应的文档PG082 Processing System 7来看解决这个问题。

在又运行了两次失败之后,我们不得不进行最简单的操作。设置最简单的系统以走完整个流程。

点击generate bitstream,运行成功后给出了整个板子的占用情况。

经过此次操作,我们虽然不能成功运用调用DMA,但是我们成功的搭建了整一个最简单的系统,下一步,我们就要搭建实际的系统。

五、重新搭建FIFO系统

1.了解了整个流程之后,我们就开始搭建实际的系统。

解压此文件夹,然后用vivado打开对应的xpr系统文件。

解压此文件夹,然后用vivado打开对应的xpr系统文件。

因为版本有可能不同,所以我们需要自动更新相应的IP。

2.在更新了IP之后,我们点开processing system,使能相应的GP与HP管脚用于DMA

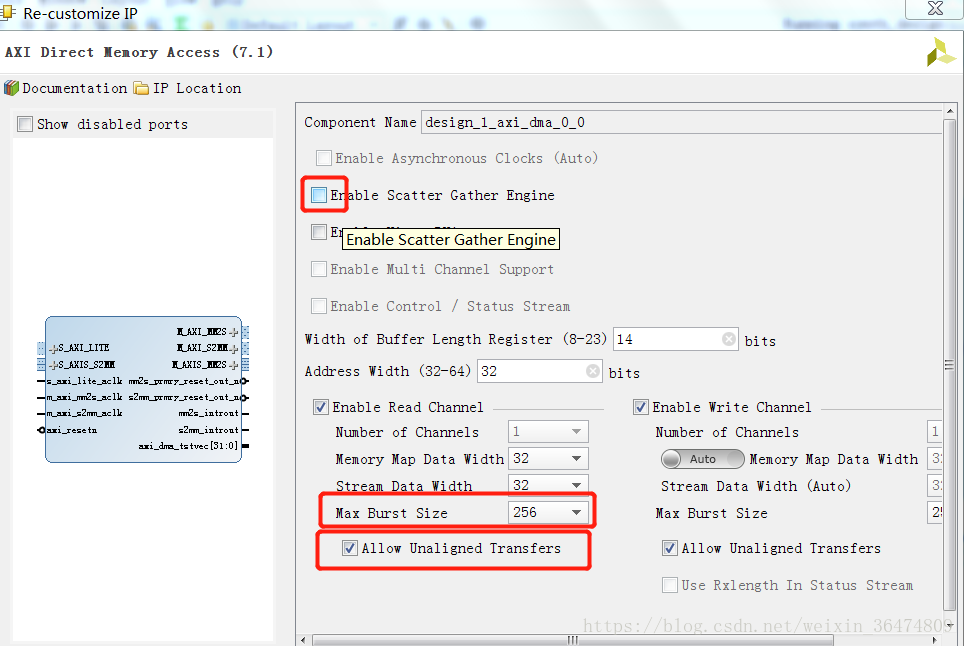

3.对应的DMA取消勾选scatter gather engine,并且改变相应的最大并发速率。(unaligned transfer可以不勾选)

4.点击块自动连接和线自动连接,让系统自动连线。

5.将FIFO的时钟和reset连接到系统的时钟和reset上,输入与输出连接到DMA上,连法参见上面。

6.在source里面点击create HDL wrapper

7.generate bit stream

8.在硬件上验证相应的项目,具体操作见

相关内容:

FPGA实践教程(四)片上ARM运行程序

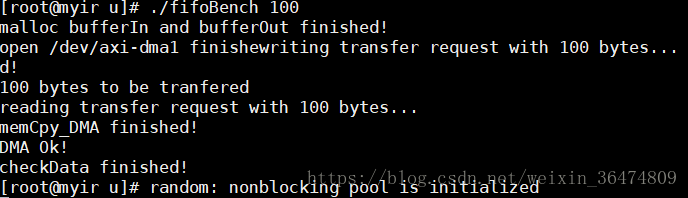

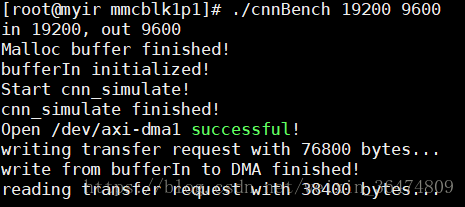

验证了我们设计的正确性。走完了整个流程,FIFO设计生成的系统是OK的。

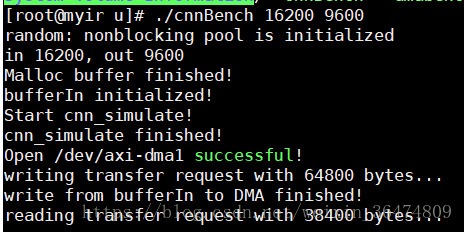

六、实现基本的卷积

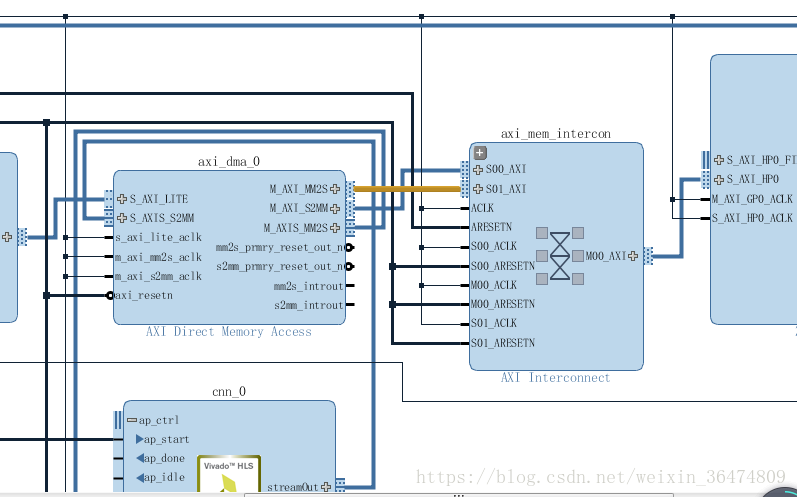

把相应的FIFO的IP core替换为CNN的IP core,从而生成比特流。重复进行上面的工作。

依然运行程序失败。

事后发现,问题原因在于系统搭建的问题。每次换IPcore都需要把原IPcore去掉,并且把所有连线删掉,然后重新布线,不然只删IPcore会有连线错误。

AXI interconnect上有一定的管脚冗余,把连线删掉,然后再连。

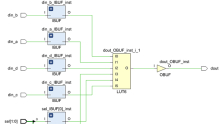

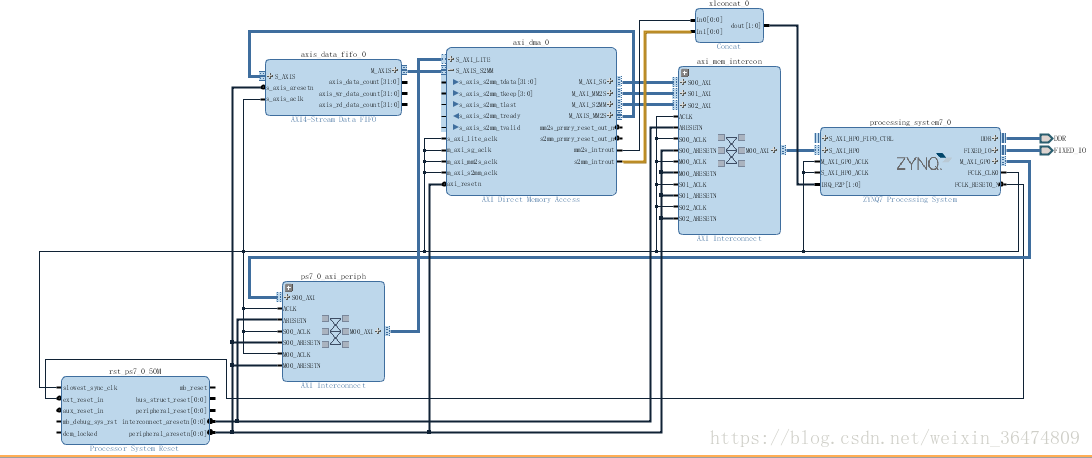

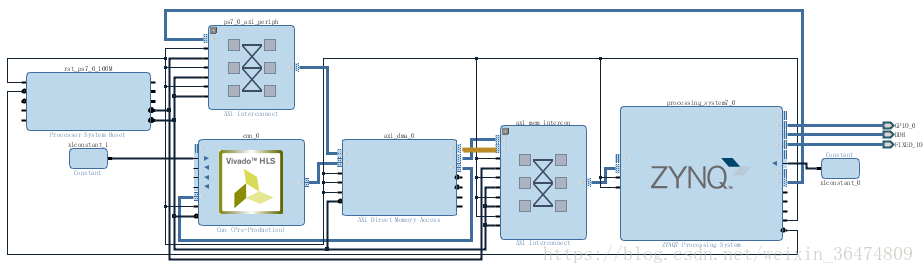

最终的layout如图:

运行失败。相应错误原因查找和最终成型的系统搭建方式见:

---------------------

作者:邢翔瑞

来源:CSDN

原文:https://blog.csdn.net/weixin_36474809/article/details/80690368