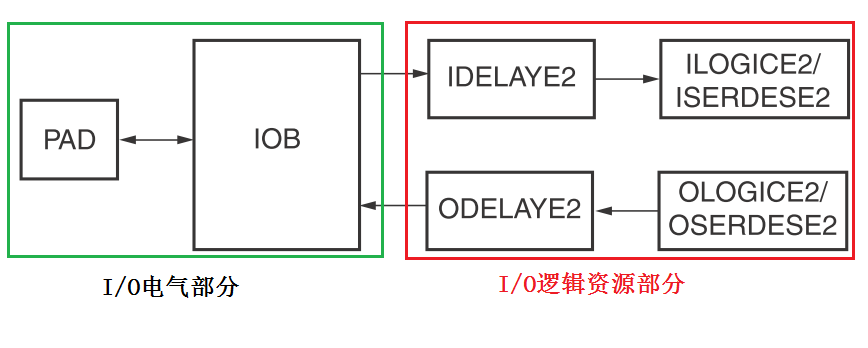

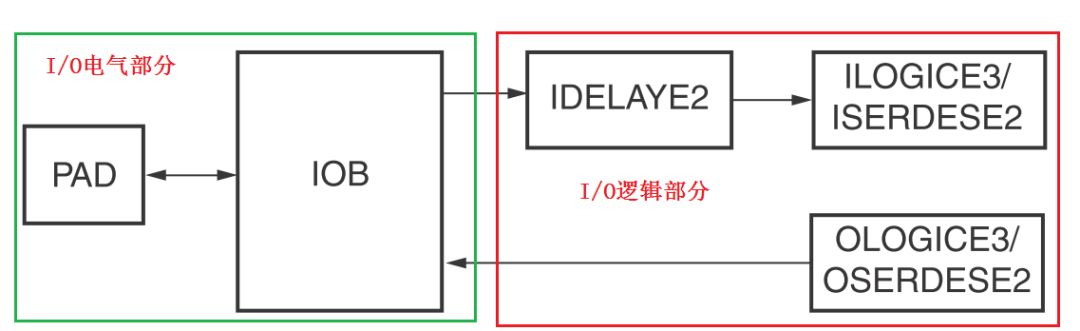

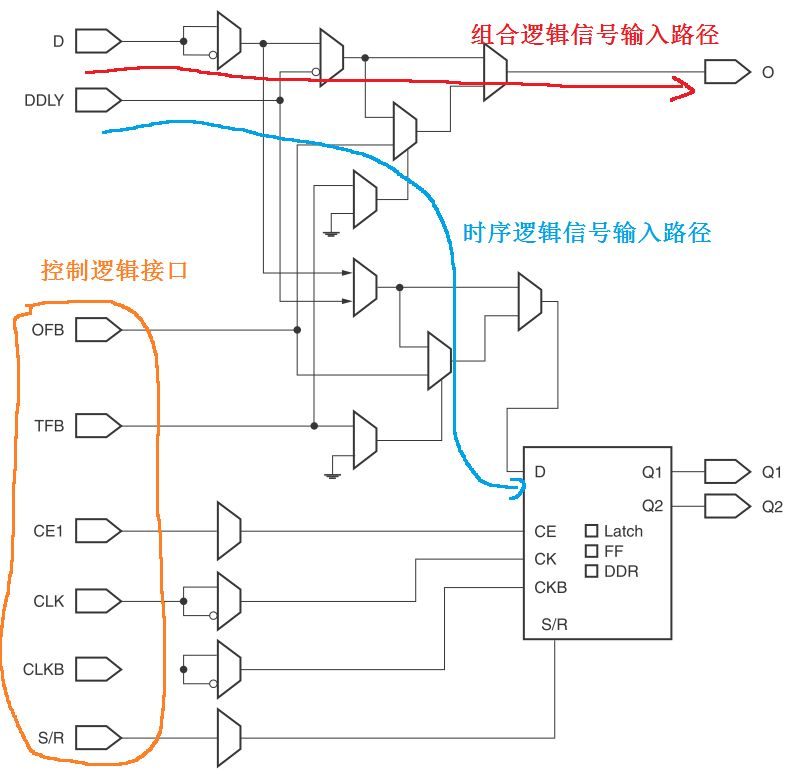

上篇咱们简单的说了I/O的电气特性,本篇咱们接着介绍I/O逻辑资源,先贴上两张图。图1为HPBANK的I/O模块,图2为HRBANK的I/O模块,两者区别在于后者无ODELAYE模块。

图1:HP BANK I/O模块

图2:HR BANK I/O模块

I/O逻辑资源主要包含5部分:

1, ILOGIC

ILOGIC即输入信号处理逻辑,紧挨着IOB,外界的输入信号最先经过的就是ILOGIC。ILOGIC是由许多的数据选择器和一个IDDR(input

Double data rate)触发器构成。该触发器既可以双沿捕获输入数据也可以拆分成普通单沿触发器。在HP BANK中,ILOGIC被称为ILOGICE2,在HR BANK中,ILOGIC被称为ILOGICE3。图3给出了ILOGICE3的示意图:

图3:ILOGICE3示意图

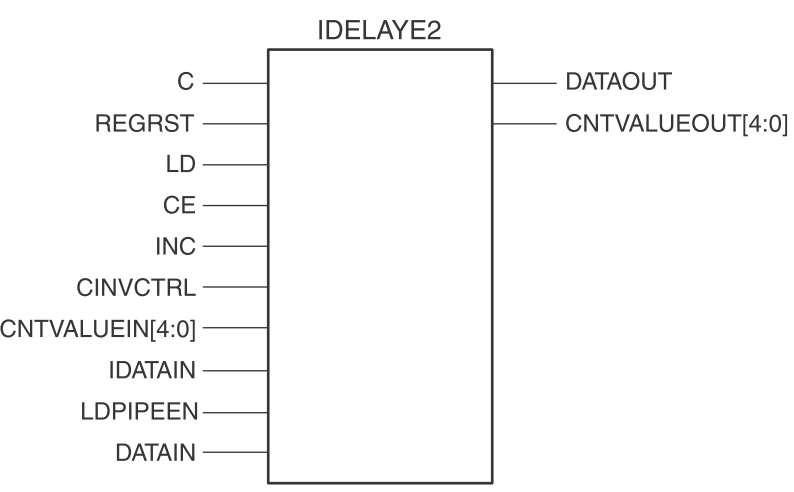

2, IDELAY

IDELAY被称为信号延迟模块,它的作用就是把信号延迟一段时间。对于一些需要对齐的输入信号来说,这至关重要。在7系列FPGA中,它被称为IDELAYE2。IDELAYE2可以将信号延迟0~31节,在这区间任意可调,并且每节的延迟精度约为78ps(1/(32×2×FREF),FREF为IDELAYCTRL的参考时钟)。图4为IDELAYE2例化框图。

图4:IDELAYE2例化框图

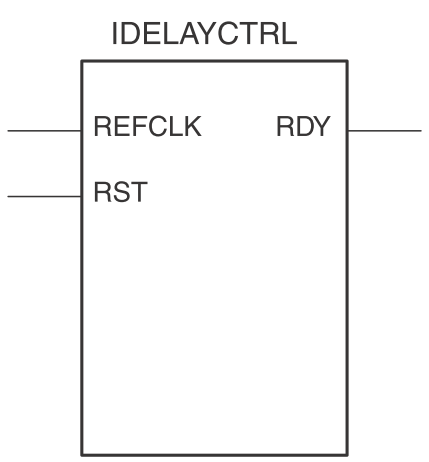

3, IDELAYCTRL

IDELAYCTRL其实是个辅助模块,这么说吧,只要咱们使用了IDELAY或者ODELAY,IDELAYCTRL必须被使用,要不然就无法正常工作。因为IDELAY或者ODELAY的延迟精度是由IDELAYCTRL的输入时钟决定的,一般为200MHz。下图5为IDELAYCTRL例化框图。

图5:IDELAYCTRL例化框图

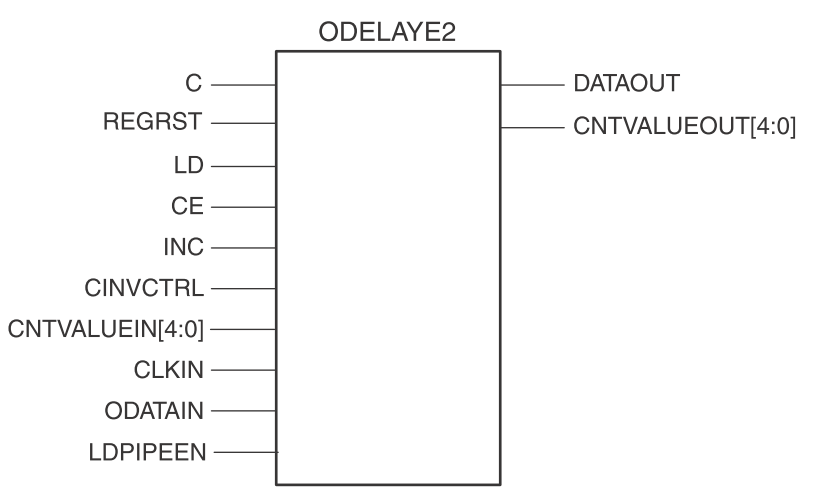

4, ODELAY

ODELAY和IDEALY的使用方式差不多,只不过ODELAY是用作输出信号的延迟。另外,HR BANK内没有ODELAY,HP BANK才有,被称为ODELAYE2。使用ODELAYE2时同样需要例化IDELAYCTRL。图6为ODELAYE2例化框图:

图6:ODELAYE2例化框图

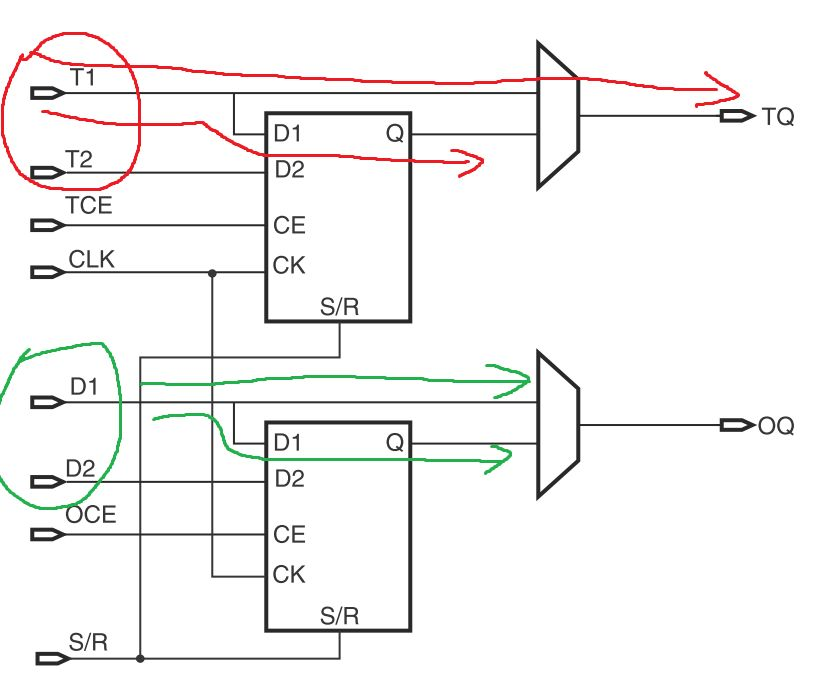

5, OLOGIC

LOGIC包括2个部分:一个用于配置输出路径。另外一个用于配置三态控制路径。输出路径和三态控制路径都可以独立配置成沿触发器、ODDR以及组合逻辑输出。

图7:OLOGIC示意图

总得来说,I/O逻辑资源就是用来获取或者输出信号。对面一般的低速信号而言,I/O逻辑资源体现不出优势,用不用都不影响最终结果,但是对于高速信号而言,就必须使用I/O逻辑资源了,不能够正确使用它,整个FPGA逻辑代码完全无用。但是FPGA不就是用来处理高速信号的么?所以I/O这一块应该是整个FPGA的精华之处,当然也是使用最难的部分了。。。。。。

为了方便咱们使用I/O逻辑资源,xilinx公司专门将本篇介绍的几种模块集中起来,构成了功能强大的源语ISERDESE2和OSERDESE2,咱们只需要调用源语,正确使用源语就能够完成高级的I/O逻辑设计了,下篇咱们就聊聊高级逻辑资源ISERDESE2和OSERDESE2吧!

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主