前些天为了支援兄弟单位的朋友,为其调试了一款激光测距仪,而该测距仪与FPGA的数据通信方式为串口,波特率为115200。该朋友的基本需求是这样的:FPGA首先向激光测距仪发送几个命令,使其以用户需要的模式开始工作,而测距仪开始工作之后就不断的以115200b/s的速度向FPGA发送距离数据。

1. 串口协议介绍

在业界,串口又称为通用异步收发器(Universal Asynchronous Receiver/Transmitter,简称UART),它的通信方式遵循一套串口协议:UART通信首先将接收到的并行数据换成串行数据来传输。数据帧从起始位开始,后面是7个或8个数据位,一个可用的奇偶校验位和一个或几个高位停止位。在接收过程中,UART从数据帧中去掉起始位和结束位,并对收到的有效数据字节进行奇偶校验,最后将数据字节从串行转换成并行。另外,需要注意的是奇偶校验位可以不需要,有些实现为了简单起见,在协议实现时就没有设置奇偶校验位。UART传输时序如下图所示:

2. 串口实现介绍

下面介绍串口的verilog实现技巧:

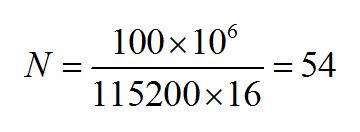

首先是需要产生串行数据发送和接收时钟,为了避免异步通信时发生滑码,确保串行数据被准确接收,一般我们采取的办法是串行时钟频率为波特率的16倍。以我调试的这款测距仪为例,它工作的波特率为115200,而我FPGA板上的系统时钟为100MHz,所以我需要对100MHz进行分频,分频系数N可以计算如下:

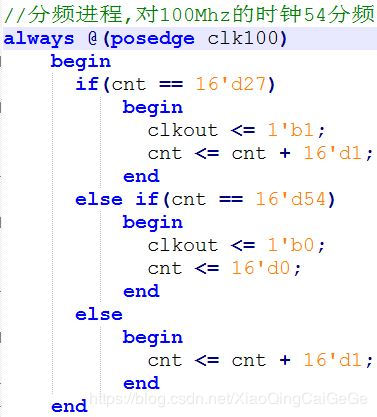

用verilog实现起来也很简单,如下图所示:

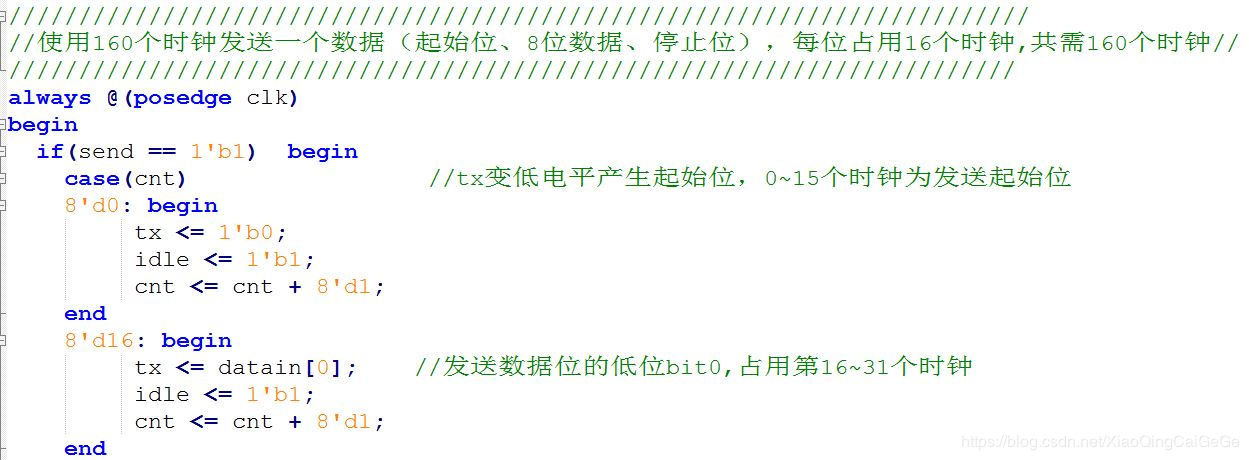

其次是串口发送模块:由于测距仪的串口协议没有奇偶校验位,因此我在FPGA实现端也没有加此功能,也就是说我只需要发送1位起始位、8位数据位以及1位停止位,共10位,而前面提到了发送1位帧数据需要16个时钟周期,所以我们可以知道:只需160个时钟周期我们就可以把10位帧数据发送完毕。

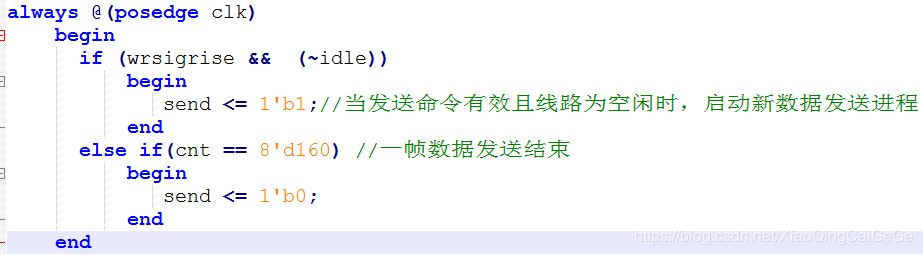

所以就有了如下代码:

其中,wrsigrise为数据使能信号,每当需要发送新数据时,该信号就拉高一个时钟周期。idle为发送模块空闲标志,idle为低电平时表示发送线路为空闲,允许新数据发送,idle为高电平时表示目前的数据还没有发送结束,线路正忙。当发送进程启动160个时钟周期后,10位帧数据就已经发送完毕。

我们再看看发送模块进程,其实也很简单:就是每16个周期发送一位数据,从低到高发送。如下图所示限于篇幅仅给出了一头一尾,中间部分是一样的:

这样10位帧数据就发送完成了,idle拉低表明线路开始空闲了。

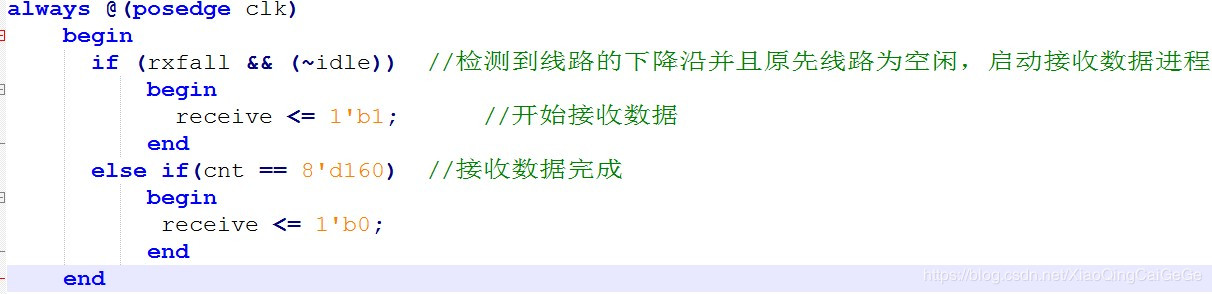

然后是串口接收模块了,其实和发送模块差不多,唯一需要注意的地方就是:如何判断数据的到来。我们看协议知道,接收线路上没有数据时会一直保持高电平,当有数据时线路会出现一个由高到低的电平跳变,我们检测到这个跳变就知道数据要来了,咱们就准备接收。如下图所示为接收控制进程:

rxfall即为接收下降沿标志,只有当该信号出现且接收线路为空闲时,接收模块才开始接收线路上的串行数据,并且160个时钟周期之后,10位的帧数据肯定已经接收完毕。

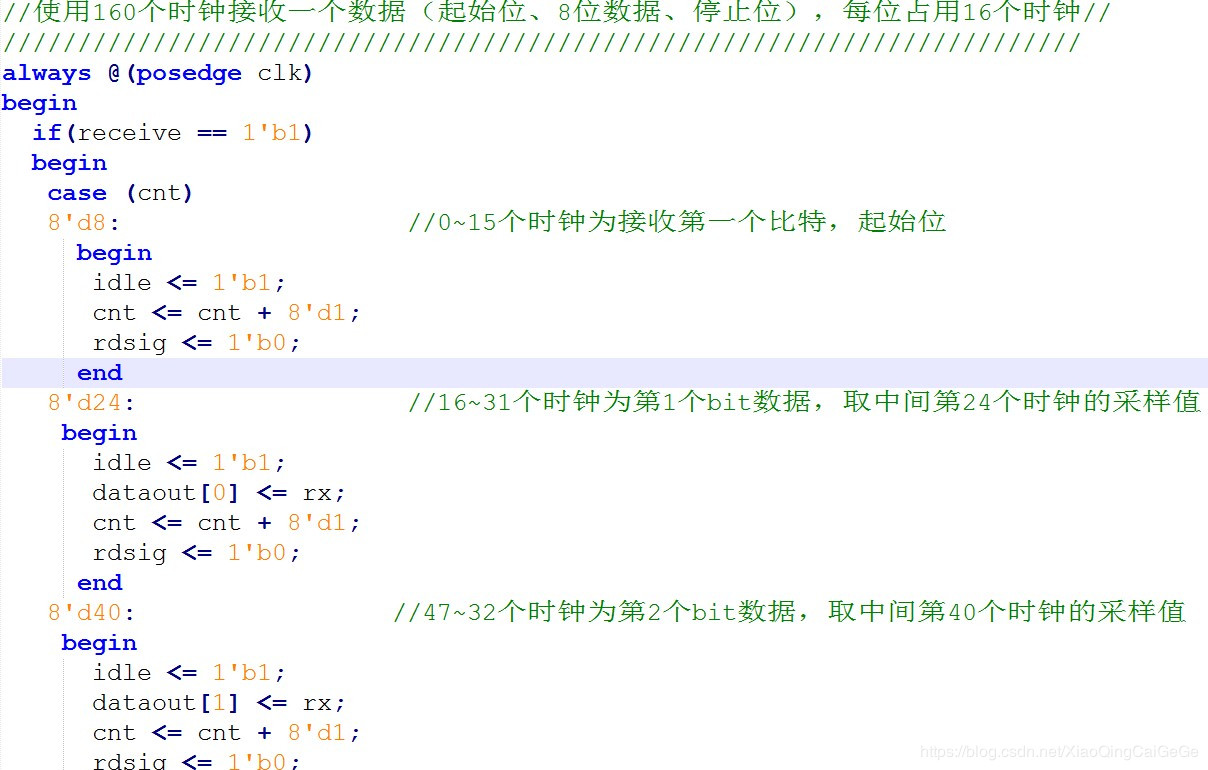

具体的接收模块和发送模块类似,但需要注意一点,我们在数据的中间点取值,这样接收到的数据最稳定,也就是说,第一个起始位是第0~第15时钟周期,我们在第8个时钟周期取数,第一个数据在第16~第31时钟周期出现,我们则在第24个时钟周期取数,以此类推~,如下图所示:

3. 测试结果

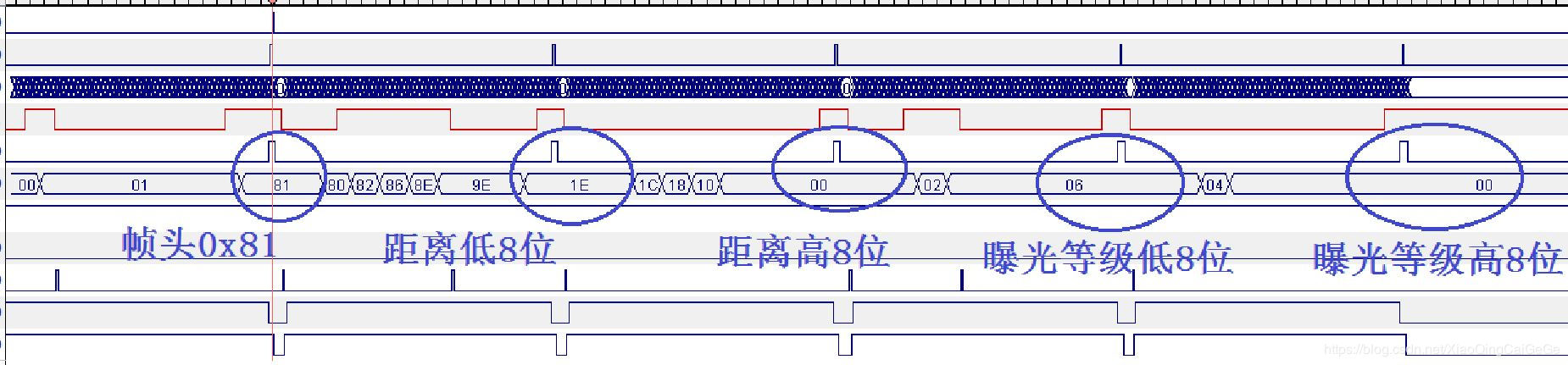

我们看看激光测距仪的数据手册,其正常工作时发送5个字节的数据:第0个字节是数据帧头,固定的0x81;第1个字节是测距的低八位数据;第2个字节是测距的高八位数据;第3个字节是测距仪曝光等级低八位;第4个字节是测距仪曝光等级低八位。如下图所示:

如果FPGA的串口代码没问题,就应该是按这个格式收到数据。启动chipscope,我们观察数据,发现数据完全正确,就此完成调试~

---------------------

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主