版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_37512669/article/details/90321282

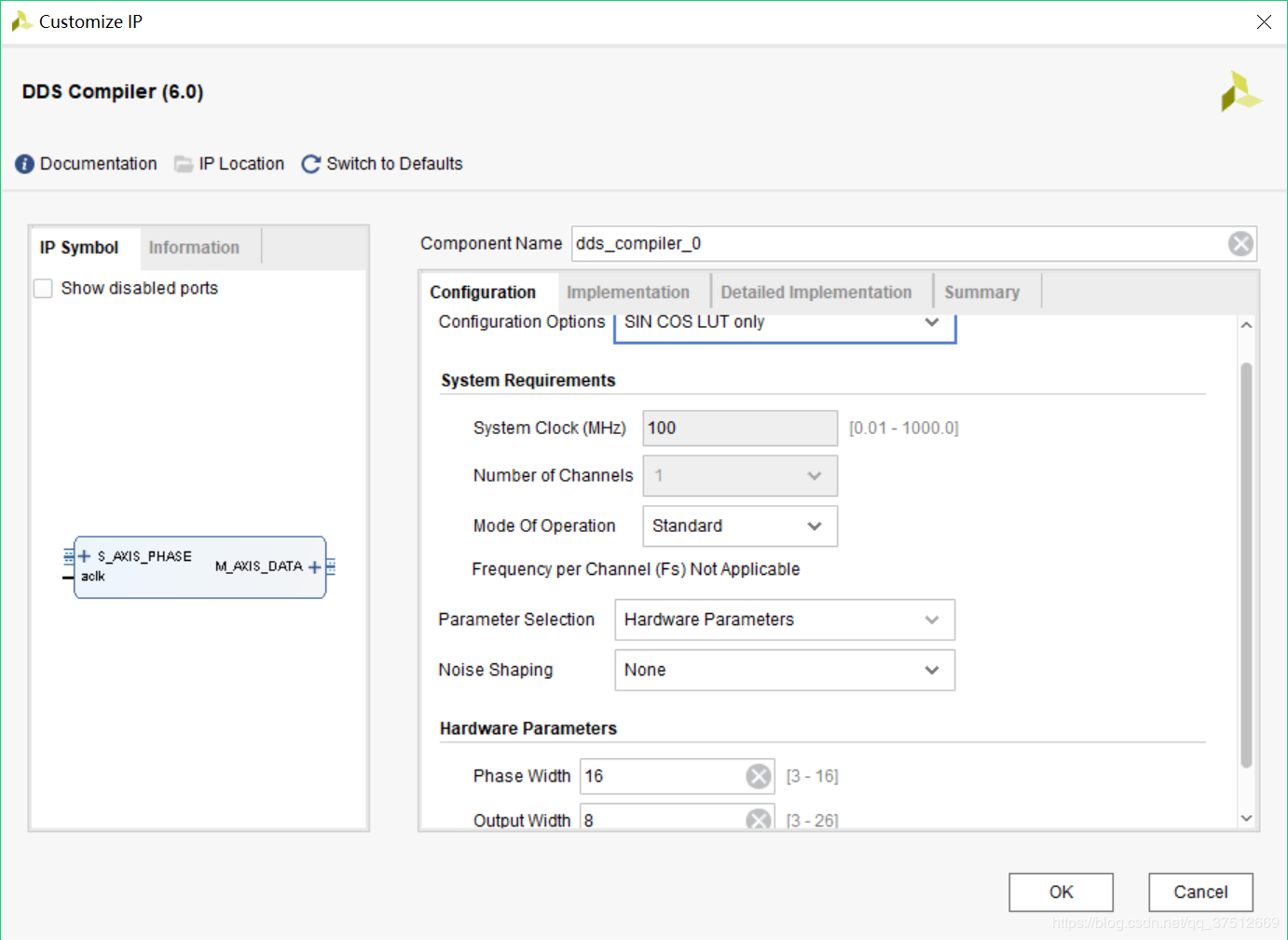

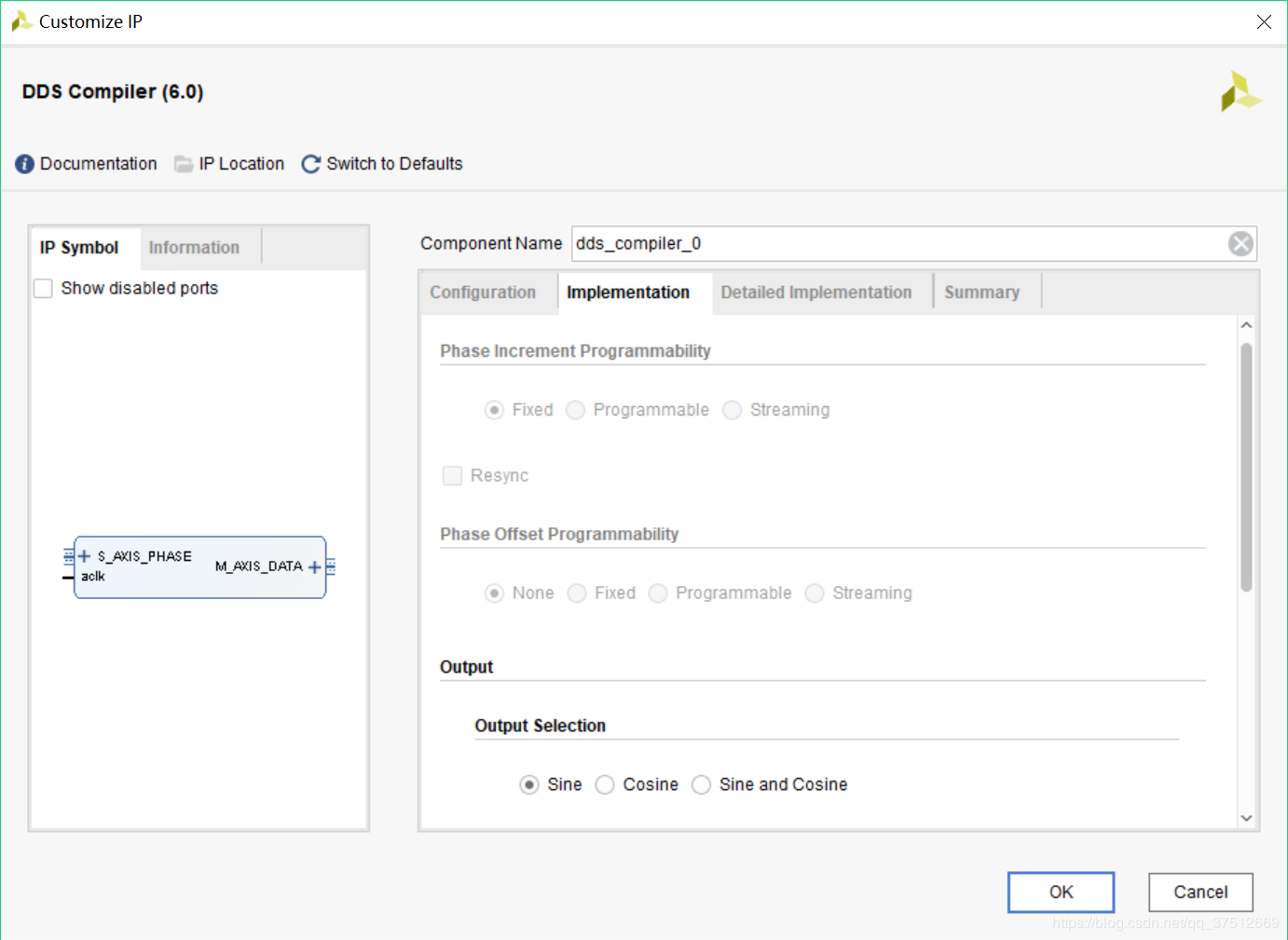

创建工程,DDS_test。在IP Catalog中搜索DDS,选择其中一个DDS Compiler,双击打开。

开发板系统频率为100MHz, 根据输出频率的计算公式,相位步进间隔= (fout / fdds_in) * 2^N (N 为前面相位的位宽),所以如果用系统的频率作为DDS的输入频率,相位步进间隔= (1k / 100M)* 2^16 = 0.65536,显然这在verilog 中无法实现,所以我们要设法使DDS IP 核的输入频率较小。这里我们通过对系统频率进行分频,获得 100KHz,作为DDS的输入频率,此时相位步进间隔为 655。

创建顶层.V文件。

创建仿真.V文件

module simu(

);

reg rst_n;

reg clk_100M;

wire data_tvalid;

wire [7:0] data_tdata;

dds_top dds_top_inst(

.rst_n(rst_n),

.clk_100M(clk_100M),

.data_tvalid(data_tvalid),

.data_tdata(data_tdata)

);

always #5 clk_100M = ~clk_100M;

initial begin

rst_n=0;

clk_100M=0;

#10;

rst_n=1;

#1000000;

$stop;

end

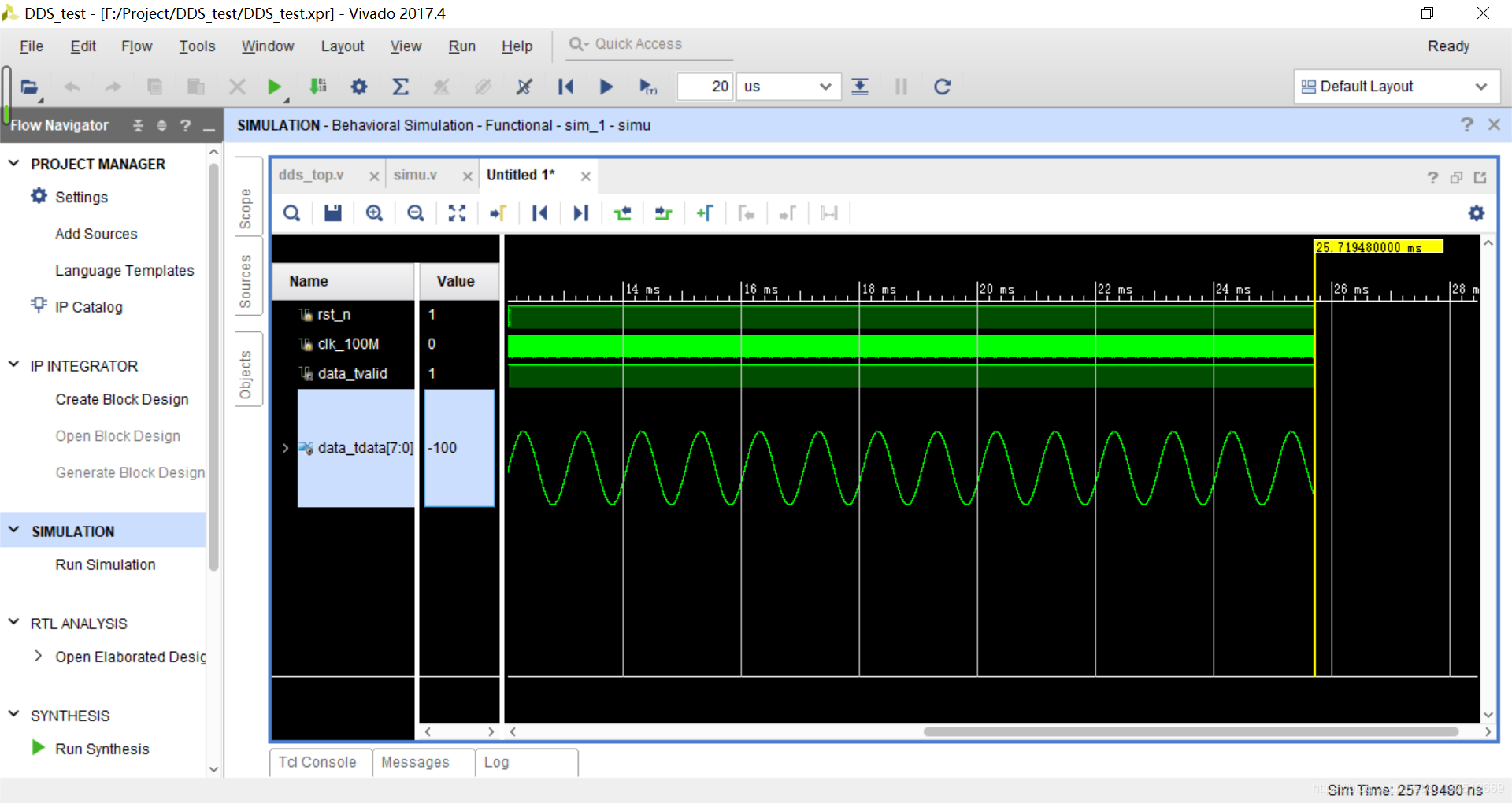

endmodule显示波形设为模拟型,右键点击Waveform style —— > Analog

数值设置为有符号Radix—— > Signal Decimal

版权声明:本文为CSDN博主「李老狗在看FPGA」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_37512669/article/details/90321282