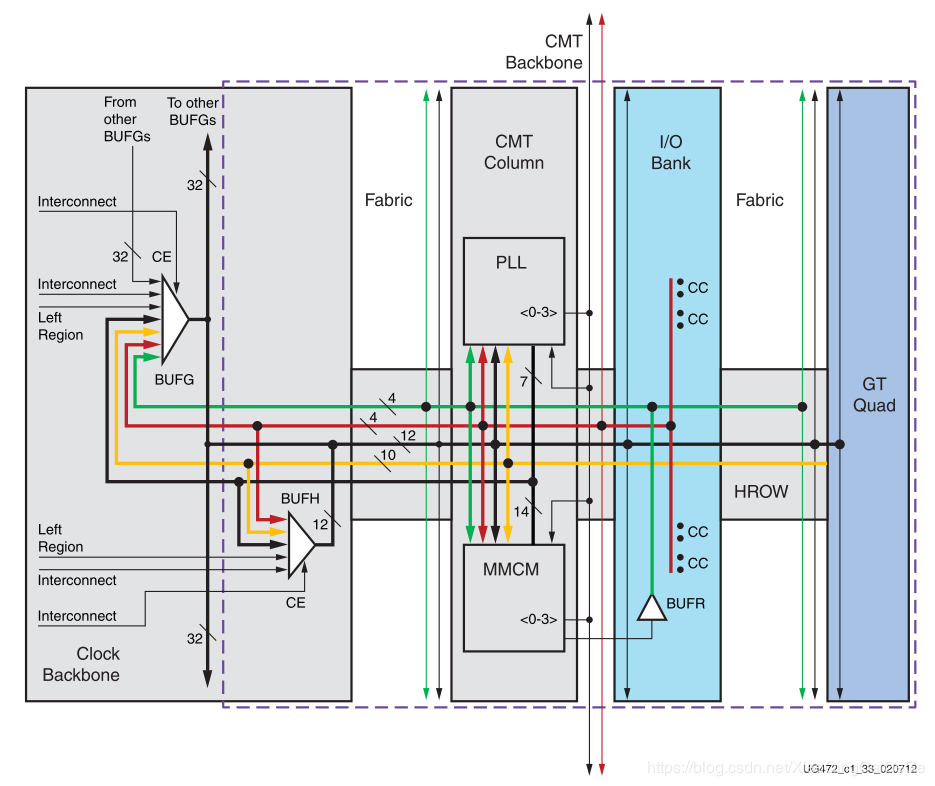

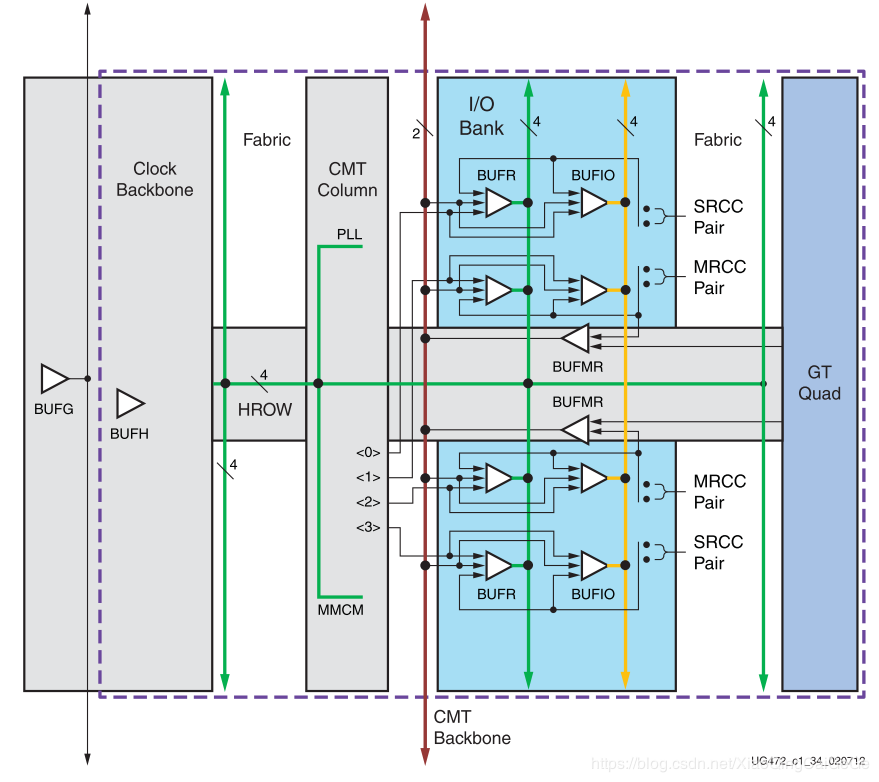

上一篇咱们介绍了7系列FPGA的时钟区域内部结构,本篇咱们接着介绍如何实际操作时钟。不说其它的,直接先上两张图,大家如果能看懂这两张图,那么就不用浪费时间看我接下来的废话了。。。。。

1,MRCC:被外部差分/单端时钟驱动;可以驱动本时钟区域的4个BUFIO、4个BUFR、2个BUFMR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

2,SRCC:和MRCC类似,但只作用在本时钟区域;其被外部差分/单端时钟驱动;可以驱动本时钟区域的4个BUFIO、4个BUFR、本时钟区域的CMT以及上下相邻时钟区域的CMT、16个BUFG、本时钟区域以及水平相邻时钟区域的BUFH。

3,BUFIO:在相同的时钟区域内,其可以被MRCC、SRCC、MMCM的CLKOUT0~3、CLKFBOUT驱动,还可以被本时钟区域以及上下相邻区域的BUFMR驱动;其只能驱动本时钟区域内的ILOGIC、OLOGIC。

4,BUFR:在相同时钟区域内,其可以被MRCC、SRCC、MMCM的CLKOUT0~3、CLKFBOUT驱动,还可以被本时钟区域以及上下相邻区域的BUFMR驱动;其能驱动本时钟区域内的CMT、本时钟区域内所有逻辑单元、以及16个BUFG(不推荐)。

5,BUFMR:其只能被本时钟区域的MRCC以及某些GT时钟驱动;其能驱动本时钟区域以及上下相邻区域的BUFIO、BUFR。

6,BUFG:其能被每个时钟区域内的SRCC、MRCC、CMT、GT、BUFR(不推荐)、其他BUFG;其可以驱动CMT、GT时钟、其他BUFG、FPGA内任何逻辑单元、BUFH。

7,BUFH:其能被本时钟区域以及左右相邻时钟区域内的SRCC、MRCC、CMT、BUFG、GT时钟驱动;其能驱动本时钟区域的CMT、GT时钟、以及本时钟区域内的所有逻辑单元。

8,GT时钟之RXUSERCLK、TXUSERCLK:其能被任何BUFG、以及本时钟区域内的BUFH驱动;其只能驱动专用的串行收发器模块。

9,GT时钟之RXOUTCLK、TXOUTCLK:其被专用的串行收发器模块驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

10,MGTREFCLK:其被外部MGT时钟源驱动;其能驱动BUFG、相同时钟区域内的CMT、BUFMR、BUFH以及相邻时钟区域内的BUFH。

11,CMT(PLL&MMCM):其能被BUFG、SRCC(本时钟区域以及上下相邻时钟区域)、MRCC(本时钟区域以及上下相邻时钟区域)、GT(本时钟区域)、BUFR(本时钟区域或者上下相邻时钟区域加上BUFMR)、BUFMR、MMCM/PLL.CLKOUT0~3驱动;其能驱动BUFG、相同时钟区域内的BUFIO、BUFR、BUFH以及水平相邻的时钟区域的BUFH、MMCM/PLL。

咱们需要用的到时钟单元以及用法都在上面完整列出了(没有列出配置时钟,配置时钟不需要咱们操作),需要使用的时候就可以按照上述的方式来操作时钟。这样是不是使用起来很方便呢?

顺便提一下,CMT即MMCM和PLL很重要,基本上咱们在使用FPGA时,外部输入时钟都需要先用CMT进行校正、去抖、分频等,其输出时钟才能被咱们使用。所以下一篇咱们就单独说一下CMT这个时钟模块之中的重中之重!

文章来源:XiaoQingCaiGeGe的博客

声明:本文由原创博主授权转发,如需转载请联系博主