本文介绍DAC芯片的Interleaved模式的使用,或者叫交错模式。

硬件设计与接口协议

Interleaved模式即用一组数字接口控制两个模拟信号输出,比如ADI公司的AD9763/AD9765/AD9767系列,具有双路10/12/14比特输出,最高时钟125M,可以采用dual-port模式或Interleaved模式。双口模式的用法和本系列第5篇中的介绍基本相同,本文着重讲述一下交错模式。

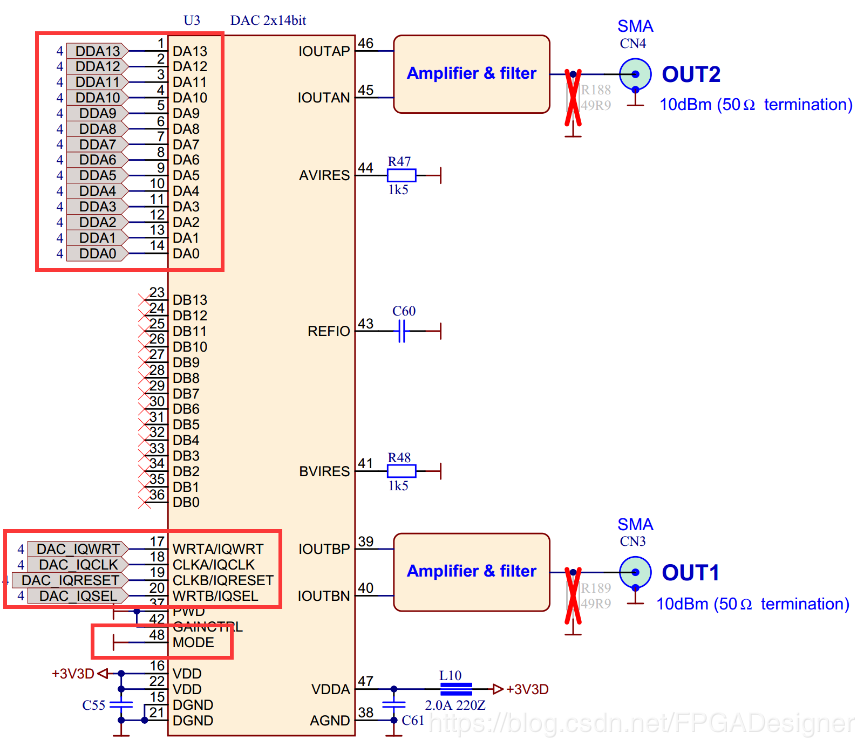

Red Pitaya开发板搭载的便是AD9767芯片,主要是因为这款开发板使用的芯片是Zynq的7010系列,PL部分管脚资源不是很多,使用Interleaved模式可以节省一组数字信号接口。相关部分的原理图如下所示:

DAC芯片的MODE管脚接地,即为Interleaved模式(拉高为dual-port模式)。只使用DDA一组接口控制OUT1和OUT2两路信号输出。Interleaved模式下17-20号管脚启用第二功能,IQWRT、IQCLK、IQRESET和IQSEL。

ADI的官方芯片手册中可以查阅到Interleaved模式下的控制时序:

IQWRT和IQCLK保持同步即可,或者IQWRT的上升沿要早于IQCLK的上升沿。在IQCLK的上升沿,数据会刷新到DAC输出端口。IQSEL控制数据的输出通道,但注意只有在IQCLK为低电平的时候才能改变状态。这样在IQCLK设置为最高的125MHz情况下,每路信号输出最高支持62.5Mhz的刷新率。IQRESET信号是高电平有效的复位信号。

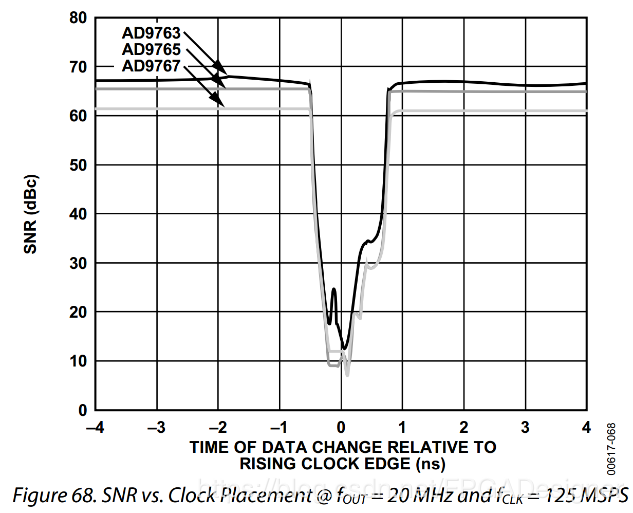

芯片手册中还着重强调了数据与时钟之间的时序关系,两者一定不能保持同步变化关系。如上图所示,当两者同步变化时,SNR只有10dB左右,输出信号质量很差。两者的变化起码要错开1ns的时间,保证达到60dB以上的信噪比。

FPGA设计

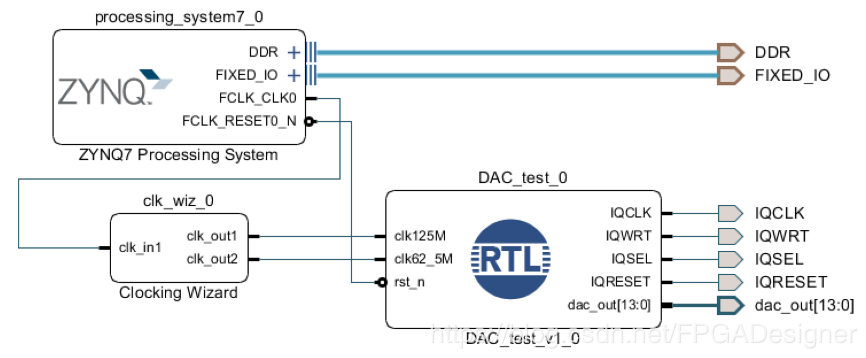

编写Verilog代码时照着时序图设计即可。首先要理清设计思路,IQSEL本质上就是IQCLK的2分频时钟,但是带有一个初始相位,具体是多少可以根据时钟周期来计算。如果IQCLK工作在125Mhz,IQSEL即为62.5Mhz,初始相位设置为90°即可。使用一个Clock Wizard IP核,由主时钟生成这两个时钟。整体设计的框图如下:

这里主时钟由ZYNQ7 IP核的FCLK_CLK0提供。DAC驱动模块中,复位信号IQRESET无需多言,系统复位时为高、正常工作时为低即可。需要注意的便是数据信号的切换,根据上面的时序图可以看出两种切换方式:在IQCLK的下降沿切换、在IQSEL的双边沿切换。一般来说比较忌讳时钟的双边沿同时做逻辑(因为比较难保证时序),因此最好使用前一种方式。

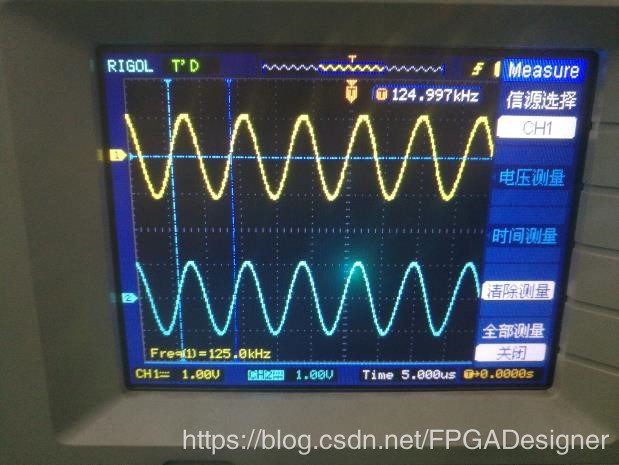

如果不是在Zynq中,只要将主时钟和clock wizard模块放在RTL设计中即可。假设OUT1和OUT2的信号源是一个相同的正弦波,首先最好通过仿真来确实时序设计的正确性,然后在板子中测试,结果如下:

两路信号都正确输出,完成了一组数据控制两路输出的设计。当然,双时钟控制法只是博主根据时序图自己构思的方法,还不知道是否有更好的解决方案,如果有欢迎各位留言。