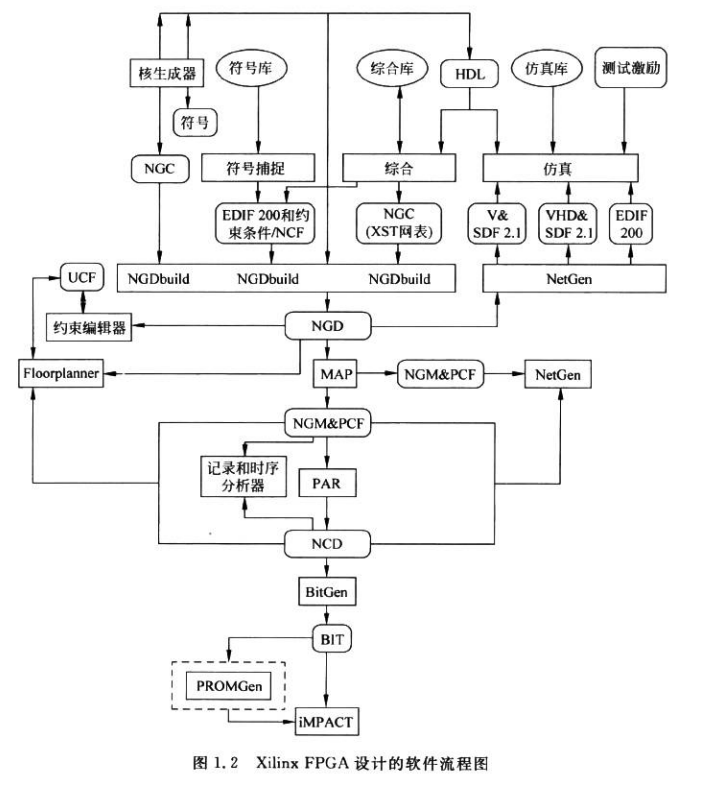

下图为详细的xilinx fpga软件设计流程

一、设计输入和综合

1、输入设计:通过文本编辑器(.v文件),或者核生成器、或者原理图输入一个设计(.v文件)

2、对输入的文件综合产生网表文件:第三方综合工具产生的为edif(Electronic Design InterchangeFormat:电子设计交换格式)文件;xst(xilinx synthesis technology)产生的位NGC文件。

ps:

①在创建设计之后,可以直接进行功能仿真(对设计中的逻辑进行测试,判断是否正常工作);

②xilinx的约束文件为.ucf,包括:

映射约束:可以使用FMAP来确定逻辑块如何映射到CLB(configuration logic block);

模块布局:模块布局可限制在指定位置布局逻辑;

时序规范:指定设计中路径的时间要求,在布局布线时,PAR使用这些时间规范达到最佳性能;

二、设计实现

1、translate(转换):将网表文件和约束文件通过NGDbuild生成NGD(native generic database逻辑本地通用数据库)文件;

2、映射(MAP):输入为NGD文件,输出为NCD文件(NCD文件使设计被映射到xilinx FPGA内元件的物理描述)和PCF(物理约束)文件;

3、布局布线(PAR):输入映射后的NCD文件,生成一个布局布线后的NCD文件。

4、比特流生成(BitGen):输入为完整的布线的NCD文件,生成一个配置的比特流(.bit扩展名的二进制文件)

5、下载到芯片(iMPACT):使用iMPACT图形工具下载到芯片,或者使用PromGen程序将BIT文件转化为PROM文件,用iMPACT工具下载到PROM。

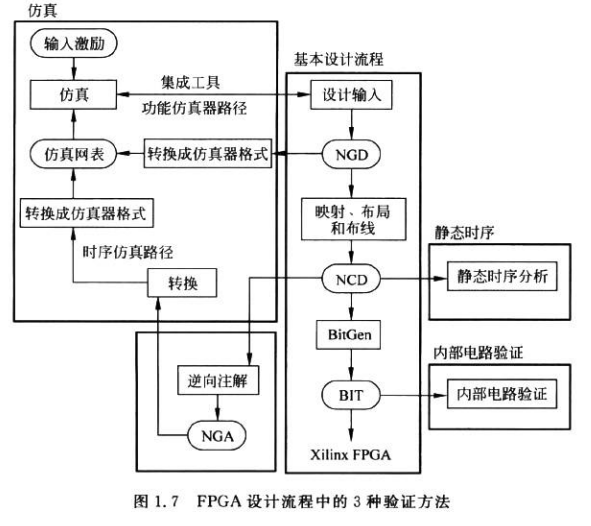

三、设计验证:

包括三方面:仿真(功能和时间)、静态时序分析、电路验证;

1、仿真:RTL级仿真,包括例化的UniSim库文件和LogiCORE模型;综合后功能仿真须有门级UniSim库元件或门级预布线SimPrim库元件;实现后,逆向注解时序仿真包括SimPrim库元件;标准延迟格式(SDF)文件。

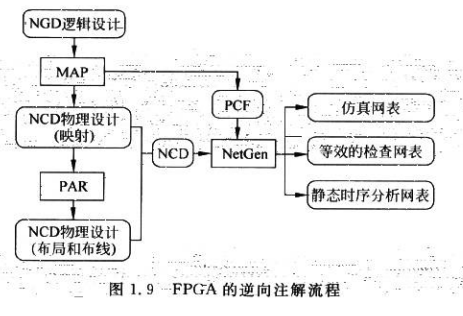

ps:逆向注解:在时序仿真之前,物理设计信息必须转化并分配回逻辑设计,FPGA使用程序NetGen进行逆向注解过程。

2、静态时序分析

可以使用时序报告程序和电路评估期(TRACE)命令行程序来运行静态时序分析。也可以使用时序分析图形化工具在执行这一功能。

3、电路验证

a、设计规则检查:BitGen中包括(design rule check,DRC)选项来评估NCD文件问题,除非使用-d选项,请他情况会自动调用DRC选项。

b、Xilinx设计下载电缆:可以通过iMPACT编程软件和使用Xilinx下载电缆对设计进行下载回读,并配置数据验证。iMPACT编程软件不能用来实时设计功能验证。

c、探针:通过使用探针,不用重新布局布线,就能很快识别任何内部信号并通过可用I/O引脚将其连接,然后用逻辑分析仪或者示波器检测。

d、ChipScore:xilinx官方板级调试工具。

版权声明:本文为CSDN博主「dnfestivi」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/dnfestivi/article/details/51841162