二维卷积滤波

二维卷积是常用的图像处理算法,即图像滑窗内的并行数据按滑窗内的坐标与卷积核函数对应坐标的参数相乘后,将所有乘法积值相加得到卷积滤波结果。

但是由于卷积核函数大多数情况下都包含小数部分,在 FPGA 内执行浮点数乘法将占用大量资源。比较常用的处理方法是将核函数内各元素数值都乘以 2 的指数,将小数部分放大至整数部分,并且根据核函数的生成原理选择足够大的指数值以保证各元素间的差异。最终在 FPGA 实现时可以将小数乘法转化为整数乘法,在所有元素的乘法积值相加后通过截去低位的方式实现除以前述的 2 的指数的计算。

以 2×2 的二维卷积为例,原始核函数包含小数部分:

乘以 2N 将小数部分放大至整数部分:

其中,

函数 floor() 表示丢弃小数部分,仅保留整数部分。原因在于必须前述的近似算法的计算结果不会大于原始核函数的计算结果。

因为图像的二维滤波算法根据其原理必须保证计算结果仍然在像素点位宽的量程以内,用于计算产生新的像素点值,即,

如果不使用 floor() 函数,而采用四舍五入的办法消除小数位,则可能出现计算结果超过像素点位宽满量程的情况,导致出错,或者额外的数值饱和判断逻辑。

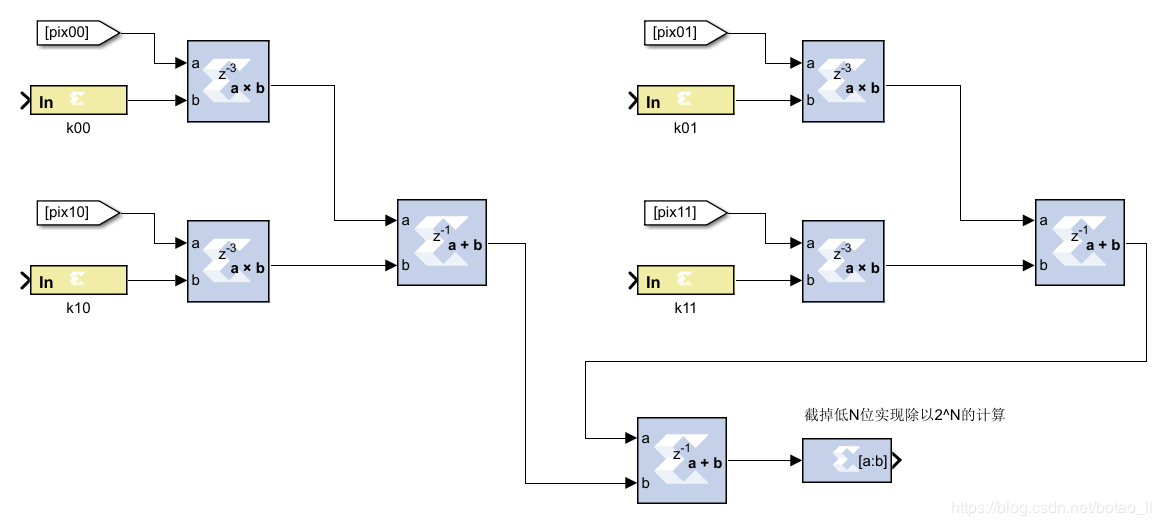

sysgen 二维卷积滤波的示意如下:

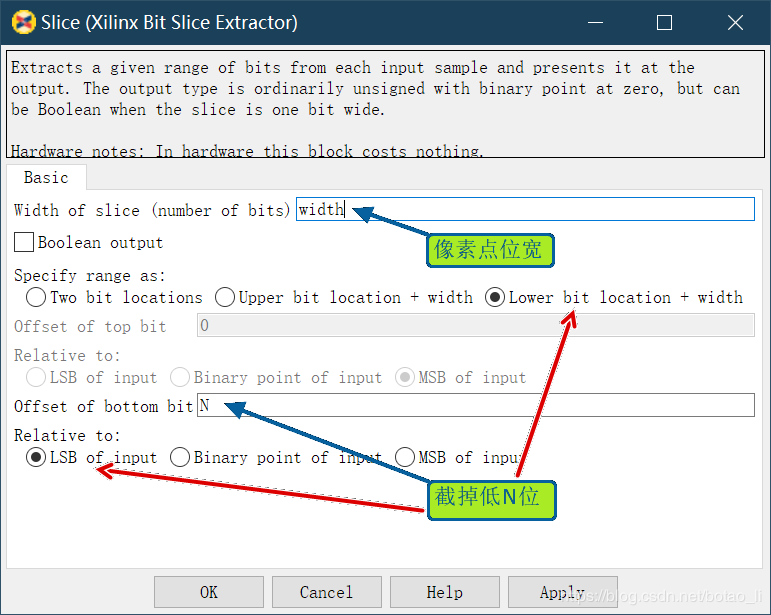

流水线最末端的 Slice 模块,即完成截去低 N 位的 2N 的除法运算,又截去由乘法和加法扩位产生的高无效位。

Slice 模块配置如下:

版权声明:本文为CSDN博主「bt_」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/botao_li/article/details/100521919