作者:romme

阻塞赋值:前面语句执行完,才可执行下一条语句;即:前面语句的执行(b=a)阻塞了后面语句的执行(c=b)。即:always块内,2条语句顺序执行。

always @(posedge i_clk)

begin

b= a;

c = b;

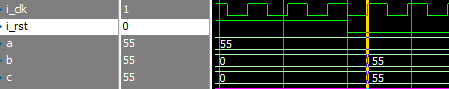

end注意:a的值赋给b,b的值赋给c,是在同一个时钟上升沿完成,如下图仿真结果。

非阻塞赋值:always块内,2条语句并行执行。即:前面语句的执行(b=a)不会阻塞后面语句的执行(c=b)。

always @(posedge i_clk)

begin

b<= a;

c <= b;

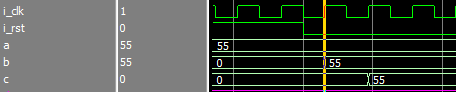

end注意:第1个clk上升沿a的值赋给b,此时b的值还没有更新;第2个clk上升沿,b的值赋给c,此时c才能获得b更新后的值。所以c获得a的值,需要2个clk完成。如下图仿真结果。

多说一句:非阻塞赋值,需理解D触发器的工作原理。b <= a,a和b分别是D触发器的数据输入和数据输出。数据a从触发器输入端输入,要经过1个时钟,数据才能打入触发器,从触发器输出端输出b;同理,从触发器输入端打入数据b,也要经过1个时钟,才能从触发器输出端输出数据c。所以,c要获得a的值,要经过2个时钟周期完成。

总结:

1:组合逻辑,使用 “阻塞赋值”。

2:时序逻辑,使用“非阻塞赋值”。

本文转自: FPGA干货架,作者:romme

*本文由FPGA干货架授权转发,如需转载请联系作者本人