1. Verilog语法的基本概念

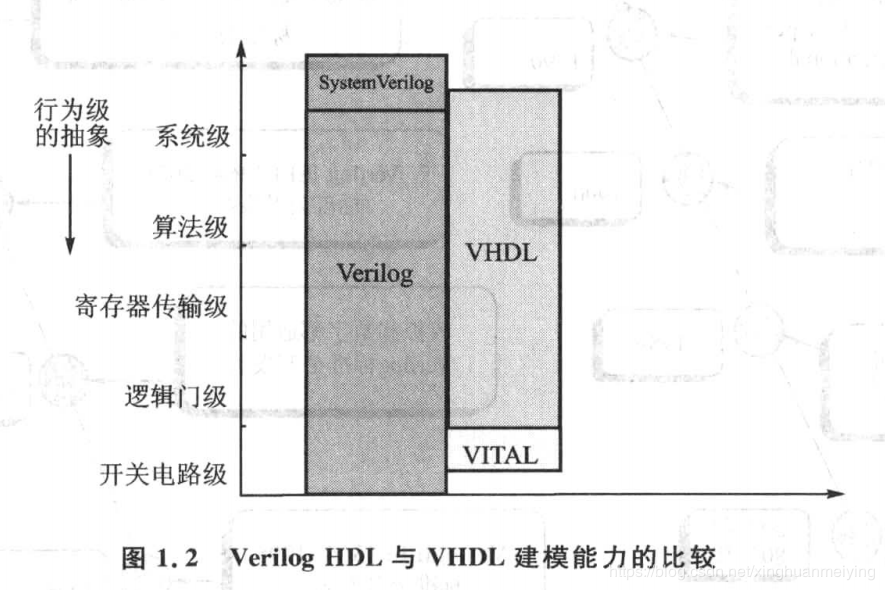

Verilog HDL是一种用于数字系统设计的语言。Verilog HDL既是一种行为描述的语言也是一种结构描述的语言。无论描述电路功能行为的模块或描述元器件或较大部件互联的模块都可以用Verilog语言来建立电路模型。Verilog模型可以是实际电路的不同级别的抽象。

这些抽象的级别和它们所对应的模型类型共有以下5种。

① 系统级(system-level):用语言提供的高级结构能够实现待设计模块的外部性能的模型。

② 算法级(algorithm-level):用语言提供的高级结构能够实现算法运行的模型。

③ RTL级(register transfer level):描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型。

④ 门级(gate-level):描述逻辑门以及逻辑门之间连接的模型。

⑤ 开关级(switch-level):描述器件中三极管和存储节点以及它们之间的连接模型。

2. Verilog HDL 和 VHDL的比较

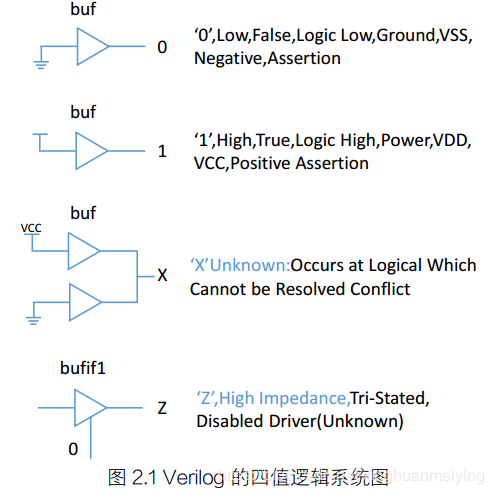

3. Verilog 的四值逻辑系统

在Verilog的逻辑系统中有四种值,也即四种状态:逻辑0,表示低电平;逻辑1,表示高电平;逻辑X,表示未知,有可能是高电平,也有可能是低电平;逻辑Z,表示高阻态,外部没有激励信号是一个悬空状态。

4. Verilog 的数据类型

在Verilog语言中,主要有三大数据类型,即寄存器数据类型、线网数据类型和参数数据类型。真正在数字电路中起作用的数据类型是寄存器类型和线网数据类型,它们共同遵守Verilog的四值逻辑系统。

版权声明:本文为CSDN博主「智小星」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/xinghuanmeiying/article/details/100564908