基于JESD204数字接口的数据转换器正在兴起,目前渐渐取代了部分基于LVDS接口的数据转换器,这种趋势就如同十几年前基于LVDS接口的数据转换器开始取代基于CMOS接口的数据转换器情形一样。

虽然如今还有少量数据转换器采用的是CMOS接口,但基于LVDS接口的数据转换器已是主流产品。

历史总是惊人的相似,技术的迭代更新的趋势之力不可抵挡,相信未来几年内JESD204必将大放异彩!

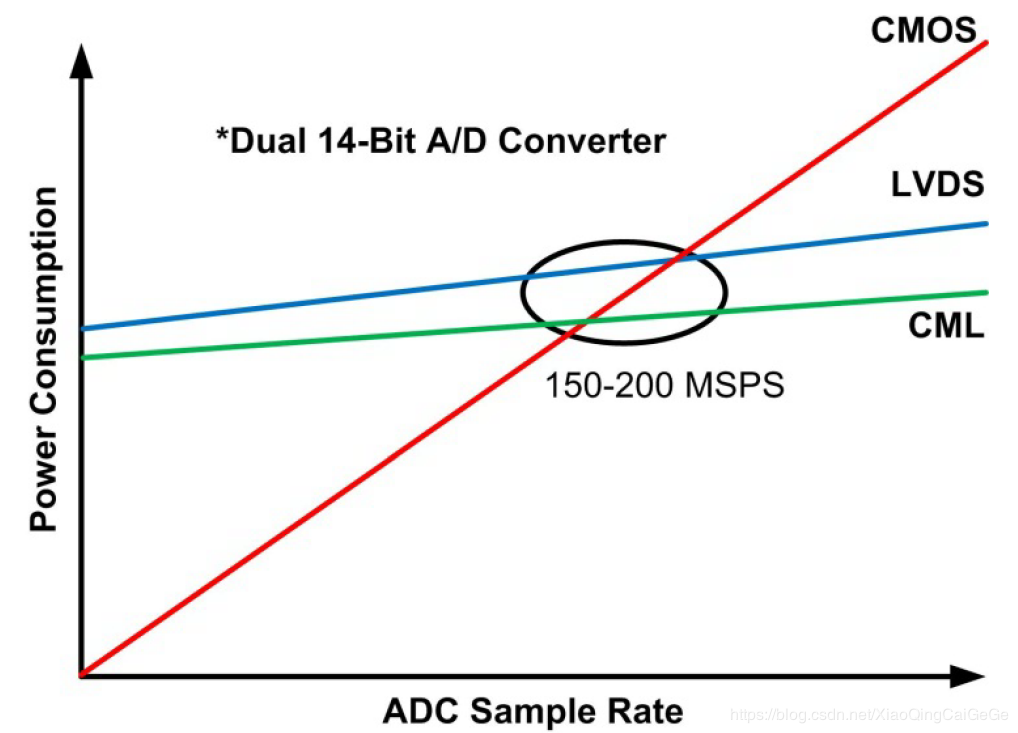

如今用户对数据转换器的采样率、采样精度的期望不断提高,而反过来又希望转换器的功耗不断降低,这导致CMOS和LVDS接口越来越不适合作为高采样率、高采样精度的数据转换器的输出数据传输接口。

比如对于CMOS接口的数据转换器来说,随着数据率的提升,接口的瞬态电流会急剧增大,导致功耗迅速增强。

对于LVDS接口的数据转换器来说,虽然随着数据传输率的提升,电流、功耗不会大幅度增长,但是受该接口本身结构以及需要随路同步时钟的限制,其支持的最高数据率受限,已经无法满足如今高速数据传输的需求。

如下图1所示是一款双通道14bit ADC分别采用CMOS、LVDS以及CML(JESD204标准采用的就是CML接口)输出接口的功耗对比:

图1:基于CMOS、LVDS、CML驱动器的ADC功耗比较

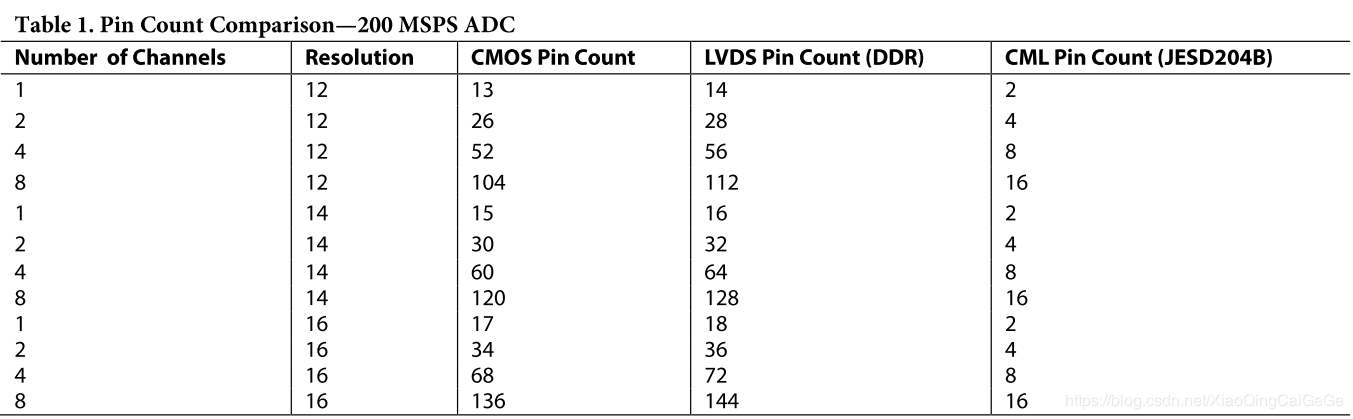

从上图可以看到,14bit采样精度的ADC大概工作在150MSPS~200MSPS区间时,CML接口的驱动器在功耗方面开始变得更加高效。并且由于CML接口采用串行数据传输结构,相比于CMOS、LVDS接口使用更少的数据输出线对,对硬件设计极为有利。表1所示为一款200MSPS的ADC分别使用这三种接口时,在不同采样精度情况下的输出数据引脚数量对比情况:

表中数据结构假定CMOS、LVDS数据输出会产生一路随路时钟,基于CML接口的JESD204B数据传输速率最高4Gbps。

很明显,JESD204B标准采用的CML驱动器接口能够大幅度减小转换器引脚数量。

随着数据转换器的采样速度、采样率不断提高,人们对更加高效的数字接口需求越来越强烈,目前以TI、ADI为代表的芯片巨头们已经实现了JESD204串行数据接口,并且这种JESD204接口协议标准为了适应更高、更快、更稳定的数据转换器和FPGA(ASIC)之间的数据传输需求,目前还在不断更新中.

JESD204协议目前已经渡过了3个版本:JESD204初始版本、JESD204A、JESD204B,现在稳定在JESD204C(JESD204C还没有商用数据转换器产品,几乎所有产品停留在JESD204B阶段)。

很显然,基于JESD204接口协议的数据转换器可以成为用户的另一种选择,并且随着系统设计越来越复杂、转换器性能越来越高,这种接口很可能是未来高速数据采集应用方面用户的唯一选择~

————————————————

原文链接:https://blog.csdn.net/XiaoQingCaiGeGe/article/details/104168691

声明:本文由原创博主授权转发,如需转载请联系博主