作者:小青菜哥哥

原文链接:https://blog.csdn.net/XiaoQingCaiGeGe/article/details/104169300

声明:本文由原创博主授权转发,如需转载请联系博主

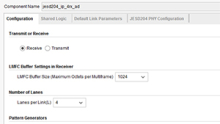

ADC芯片会包含许多性能参数,而我们在选择ADC芯片时,其中有一项关键性的参数值得关注,即数字化的数据输出接口类型(the type of digital data output)。目前在高速ADC芯片中,使用最广泛的数据输出接口类型有3种:

1. 互补型金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)

2. 低电压差分信号(Low Voltage Differential Signaling, LVDS)

3. 电流模式逻辑(Current Mode Logic, CML)

ADC芯片使用的这3种数字接口都存在某些优势和不足,因此设计人员必须考虑到ADC的采样率、采样精度、数据输出比特率、系统功耗等指标和这3种接口之间的内在关系。本篇将简要介绍这3种数据输出接口的电气规范、适用范围以及性能对比。

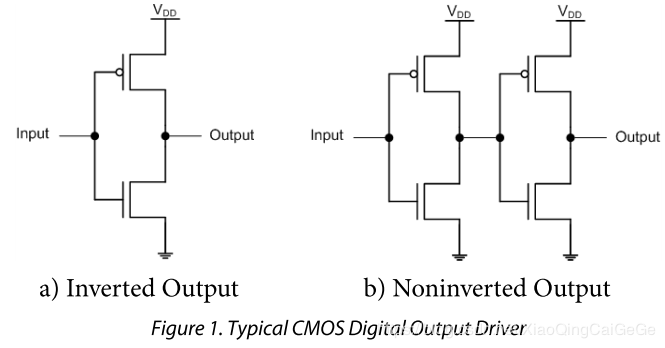

以前许多采样率低于200MSPS的ADC采用的是并行CMOS接口,一个典型的CMOS接口使用了两个场效应晶体管:包含一个PMOS和一个NMOS,分别与电源电压(VDD)和地相连,如图1a所示:

1a这种结构的CMOS接口会导致输出信号与输入信号的高低电平反相,称为CMOS反相驱动器,为了使用方便,使输入/输出信号同相,因此在第一级CMOS反相输出器后面又加了一级CMOS反相器,衍生出了1b所示的CMOS同相输出驱动器。

CMOS接口具有非常高的输入阻抗和非常小的输出阻抗。在CMOS驱动器的输入端,由于门级氧化物的隔离,使得CMOS的两个晶体管的输入门级阻抗非常高,大概可以做到从数千欧姆到数兆欧姆。而在驱动器的输出端,输出阻抗由漏极电流ID决定,在任一时刻总是存在其中一个晶体管导通,导通电阻非常小,因此CMOS驱动器的输出电阻很小,大概在数欧姆到数百欧姆量级。

CMOS驱动器输出信号的高低电平范围从VDD~GND,因此CMOS接口的供电电压决定了信号最高摆幅,目前常见的数据转换器CMOS电平有5V、3.3V、以及1.8V标准。

由于CMOS接口的高输入阻抗和低输出阻抗特性,因此CMOS接口的优势就在于一个CMOS输出可以驱动多个CMSO负载。另外,CMOS接口具有非常低的静态电流,只有当CMOS接口正在进行信号的高低电平切换时,才考虑有电流流过CMOS接口。

无论CMOS接口处在低电平或者高电平期间,流过CMOS接口的电流几乎可以忽略不计,只有当CMOS接口从高电平向低电平,或者低电平向高电平转换时,在VDD到GND之间会出现一瞬间的低电阻特性,此时电流会消耗比较大。主要因为这种原因,当转换器超过200MSPS后,CMOS接口功耗就会变得很大,被其它接口技术取代了。

当然,CMOS接口被取代还有另外一个不得不提的原因,那就是转换器的每bit数据都需要一个CMOS接口。如果一个转换器是14bit精度,那么它就需要14个CMOS接口来完成数据的传输。目前许多ADC/DAC产品,在一个封装内都集成了多个转换器,比如最流行的8通道ADC/DAC芯片,如果采用CMOS接口,这样的14bit精度芯片就需要至少112个CMOS输出引脚来完成数据的传输,这种方式不仅使得封装变得复杂,影响PCB布局布线,还是得芯片整体功耗急剧上升。

为了解决CMOS接口带来的上述问题,低电压差分信号(Low Voltage Differential Signaling, LVDS)接口应运而生。

相比于CMOS接口,LVDS接口在某些方面具备极大的优势:LVDS信号的摆幅非常低,只有±350mV,并且以差分对的形式传输信号。信号的低摆幅特性使得LVDS接口具有非常快的高低电平信号转换时间和极低的电磁干扰,信号的差分传输方式则使得信号的抗干扰性能优异。但是,LVDS信号的阻抗控制非常关键,负载的阻抗需要控制在100Ω左右,且差分信号传输线的阻抗也需要被控制在100Ω。如下图所示为典型的LVDS输出驱动器接口:

我们从图中可以看到,LVDS接口连接负载后,会始终存在一个固定的直流负载电流,无论VDD是3.3V、2.5V还是1.8V,该电流在100Ω的负载端总是会形成一个典型值在1.2V左右的直流共模电压。当输入的信号电平高地变换时,3.5mA的恒流源会在100Ω负载端形成±350mV的交流摆幅。

虽然LVDS接口在PCB布线时,比CMOS接口需要更加注意,但是该接口在处理采样率超过200MSPS的转换器数据传输时,优势明显。首先LVDS接口的恒流特性使得它不需要特别大的电流消耗,而CMOS接口则在电平转换时会出现非常大的电流消耗,对电源电压的稳定造成很大压力。其次,LVDS接口允许数据以DDR(double-data-rate)方式传输,这意味着同一个LVDS接口在一个时钟周期内可以传输2bit数据,而CMOS接口是做不到的。另外,在高速数据传输时,LVDS的功耗要比CMOS小。

虽然LVDS接口比CMOS接口具有更多的优势,但是这种接口同样也存在着一些限制。当转换器的精度提高后,LVDS数据输出的接口数量增多,导致PCB差分等长布线越来越困难,另外由于转换器的采样率如今越来越高,需要的接口传输速率已经超过了LVDS接口所能承受的上限(~1Gbps)。

目前转换器的数字输出接口趋势在向电流模式逻辑(Current Mode Logic,CML)接口发展。当转换器芯片的转换精度更高(≥14bit)、采样率更高(≥200MSPS)、而芯片更小封装、更低功耗时,CML接口是不错的选择。当前基于JESD204协议的高速转换器采用的都是CML接口。

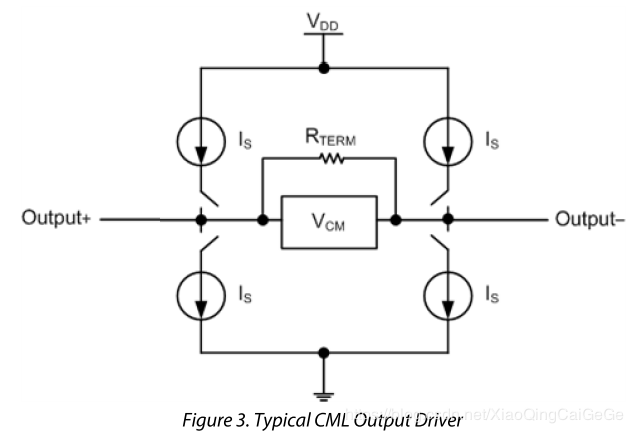

采用JESD204协议后,CML接口不仅可以实现最高12.5Gbps的数据传输速率,而且转换器的接口数量降低的令人惊叹。在转换精度提升、采样率提升、转换通道增加的情况下,基于JESD204协议的CML接口使得器件的数据输出引脚更少、PCB布局布线更加方便。如下图所示为CML接口的示意图:

从上图可以看到CML接口的可选源端匹配电阻和共模电压,这是和LVDS不同之处。电路的输入信号驱动开关,从而控制4个电流源的打开和关断,引起输出信号的高低电平变换。同LVDS一样,CML也在恒流源控制下工作,这样节约了输出引脚数量,且降低了功耗。负载匹配电阻在CML接口中同样需要,单端传输线需要控制在50Ω,因此CML差分走线的阻抗需要控制在100Ω左右。

CML接口为了适应不同版本的JESD204协议标准,在不同的传输速度下,其输出信号的差分摆幅和共模电压会有所不同。传输速度≤6.375Gbps时,CML差分信号的摆幅在800mV,共模电压约1V。传输速度在6.375~12.5Gbps时,差分摆幅为400mV,共模电压还是为1V。

随着转换器的采样率和转换精度不断提高,数据传输接口也要与时俱进,跟得上高速数据传输的步伐,显然目前CML接口成为了转换器输出的高速数据最理想的接口载体。

以上三种典型的数字接口在时序方面都有一些需要注意的地方,由于目前许多的转换器还是采用的CMOS接口和LVDS接口,因此各信号走线路径之间必须保持最低的偏差,如果各个信号线走线路径差别过大,数据时序关系就会被破坏。另外由于CMOS接口和LVDS接口在输出数据的同时,会同时有一路时钟信号输出,时钟走线和数据走线路径必须非常小心,避免造成不必要的偏差。

虽然JESD204协议下的CML接口走线比以上两种接口要简单的多,但同样有需要注意的信号走线方式。由于采用了8b/10b编码,数据传输时无需随路时钟,走线会非常简单,只需注意走线阻抗匹配即可,但数据接收端的时钟数据恢复电路(CDR)就变得非常重要了,幸好用户无需设计CDR,只需使用时注意。

总得来说,这三种接口都有各自的适用范围,当转换器采样率低于200MSPS时,CMOS接口仍然是许多转换器的选择,采样率高于200MSPS后,LVDS接口就相比于CMOS接口具有更大优势。

从转换器向更高精度、更高采样率、更低功耗、更小尺寸发展的趋势来看,CML接口势必会成为高速串行数据传输的首选,例如刚刚崭露头角的JESD204标准。