作者:小青菜哥哥

原文链接:https://blog.csdn.net/XiaoQingCaiGeGe/article/details/106477346

声明:本文由原创博主授权转发,如需转载请联系博主

GTX是kintex-7系列FPGA内部的高速数据收发器硬核模块,专门用于FPGA与外部的高速数据通信,目前许多常用的高速协议(比如JESD204、PCIE、SATA、SGMII接口的以太网等)的实现都需要用到GTX。GTX的基本内容以前介绍过了,这里不再叙述。该篇主要记录两片FPGA利用各自的GTX实现高速数据的收发过程。

1,硬件工作环境

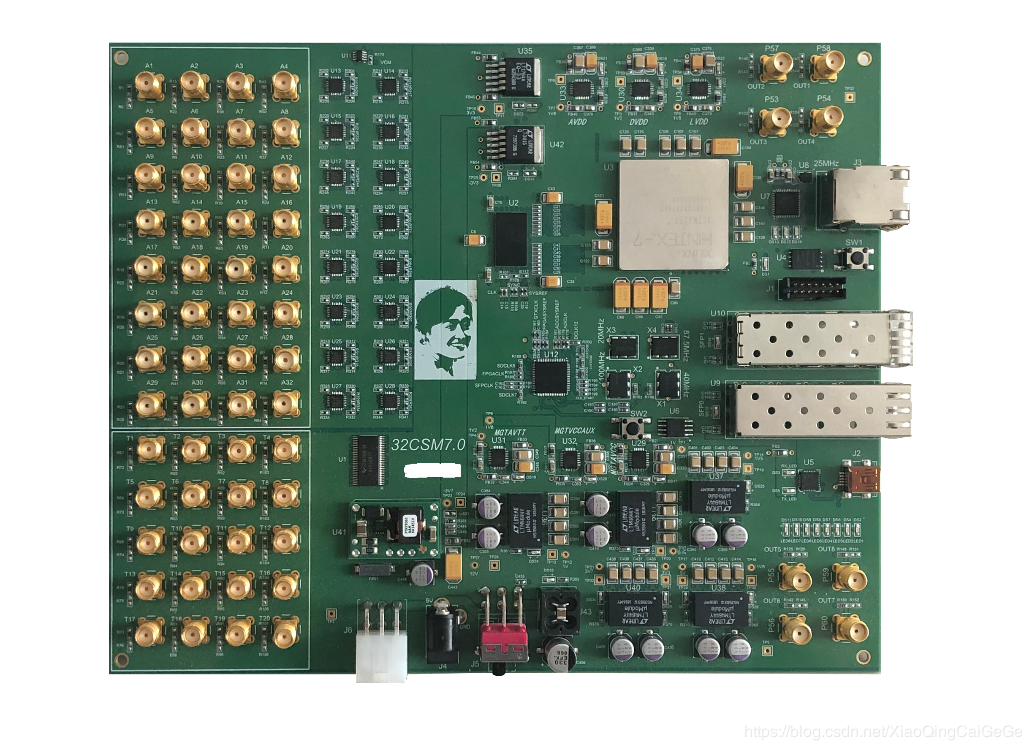

FPGA:kintex-7。供电:12V/4A 直流电源。该板卡最多外接32通道2Vpp模拟信号以及20路外部触发信号。数据传输接口方式有千兆以太网接口、高速光纤接口以及低速USB串口。

图1:硬件PCB

2,逻辑开发环境

Vivado2017.4。

3,测试工程的逻辑介绍

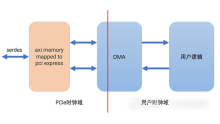

图2:逻辑框图及硬件图

如图2为测试工程的逻辑框图。GTX的参考时钟为板载87.5MHz差分晶振,设置的传输线速率为1.75Gbps。在七系列FPGA中,一个GT quad包括4个GTX收发器,本次实验中的第0、1路的收发端直接板内相连,用作测试使用。第2、3路的收发端引出,用光纤作为传输介质,实现板间高速数据传输。4路发送器分别包含累加数产生器、数据发送FIFO、Comma产生器以及2:1 MUX,MUX的输出最终进入GTX的发送端。4路接收器分别包含Comma过滤器、数据接收FIFO以及累加数检验器。如下图3所示为实测现场硬件图:

图3:实测现场硬件图

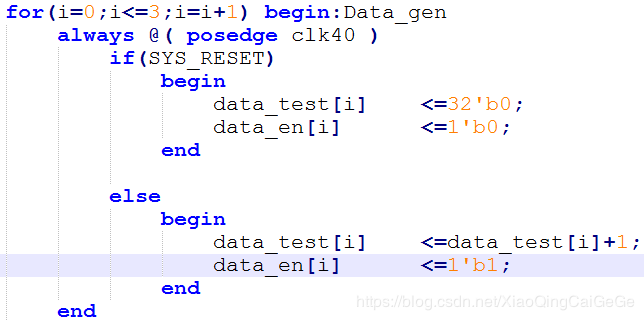

累加数产生器

在40MHz的用户时钟域下,产生4路32bit的累加数,逻辑代码如下图4所示:

图4:累加数代码模块

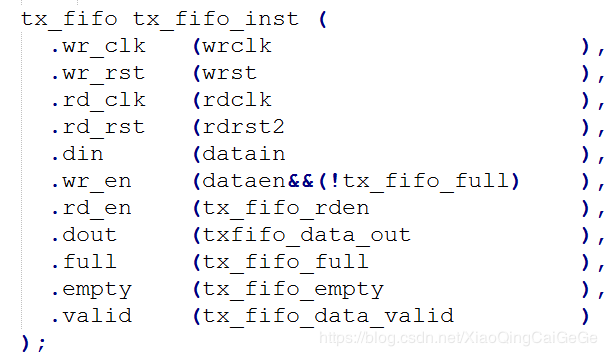

数据发送FIFO

只要FIFO处在不满的状态,那么在每个40MHz的时钟上升沿,将产生的累加数分别写入FIFO中,只要FIFO不空,就在43.75MHz的GTX时钟域(TxClkout[3:0])下将数据读出。如果FIFO被空了,Comma产生器就开始工作。如图5所示为数据发送FIFO模块:

图5:数据发送FIFO模块

Comma产生器&&2:1 MUX

一旦数据发送FIFO的数被读完了,Comma产生器就开始工作,产生重复的32’h000000bc,其中bc就是comma字符K28.5。如果不空,就一直读FIFO中的累加数据,如图6所示:

图6:Comma产生器代码和MUX

GTX硬核

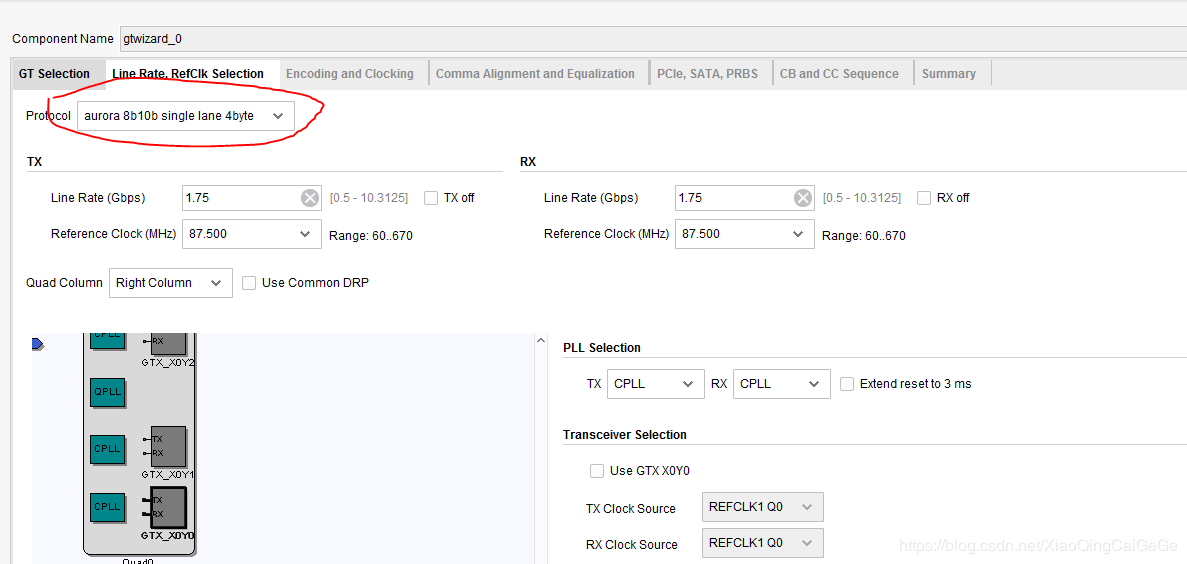

32bit正常数据或者comma字符进入GTX硬核模块,通过内部的8/10b编码、并串转换等操作后,就变成1.75Gbps的高速数据串行流输出了,在GXT接收端,硬核再将串行数据转换为32bit的并行数据。GTX的生成只需要通过IP生成器就可以了,需要注意的是在选择串行协议时,为了最省事,选择aurora 8b10b single lane 4byte就可以了,其它全部默认即可,如图7所示。

图7:GTX例化

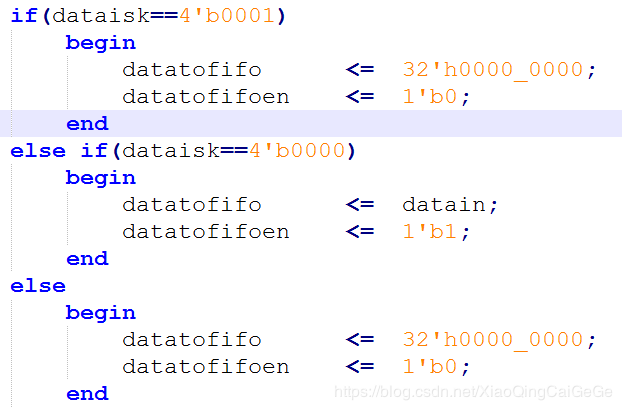

Comma过滤器

由于接收到的数据可能是32’h000000bc的Comma,因此需要把它过滤掉,只留下正常累加数据进入数据接收FIFO即可,如下图8所示:

图8:Comma过滤器

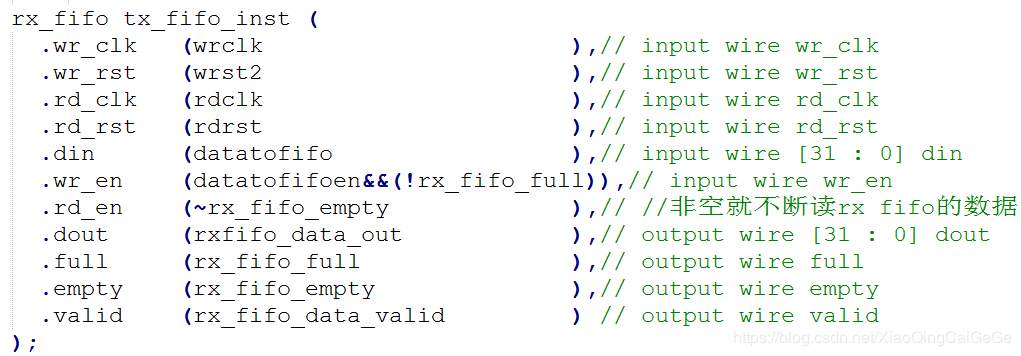

数据接收FIFO

正常累加数据在43.75MHz的GTX时钟域(RxClkout[3:0])下将数据写入FIFO中,在40MHz的用户时钟域下将FIFO中的数据读出即可。其操作和数据发送FIFO刚好相反,如下图9所示:

图9:数据接收FIFO模块

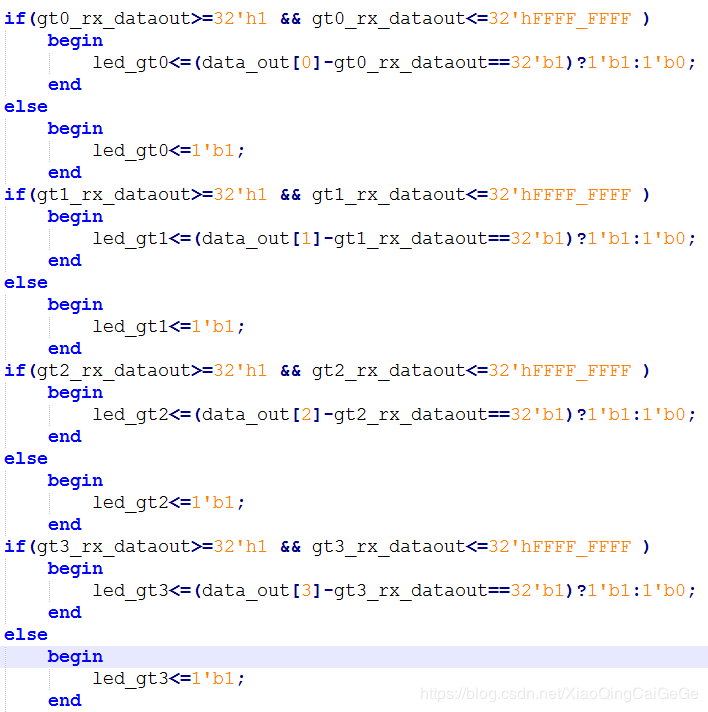

累加数检验器

接收到的数据应该是步长为1的32bit累加数,如果在0~32’hFFFF_FFFF范围内,相邻数相减值不为1,则说明GTX传输有问题。通过连续chipscope监测led_gt[3:0]的状态,就可以判断数据传输的正确性。如下图所示为:

图9:累加数检验器错误监测

如下图所示为实际测试结果,以 led_gt*为0状态做触发条件,ILA核长时间未触发,接收到的数据也为累加数:

图10:累加数测试