版权声明:本文为CSDN博主「Jaenora」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/Jaebeberey/article/details/100045812

由于开发板DIGILENT Genesys2 的开发手册中说明了自带的时钟IP核为差分时钟,所以研究了下Vivado中差分时钟的配置方法。

1.Genesys2开发板用户手册中对内置时钟的说明

1.首先,我在DIGILENT Genesys2 的页面中下载了用户手册,其中对于此开发板的时钟是这样说明的:

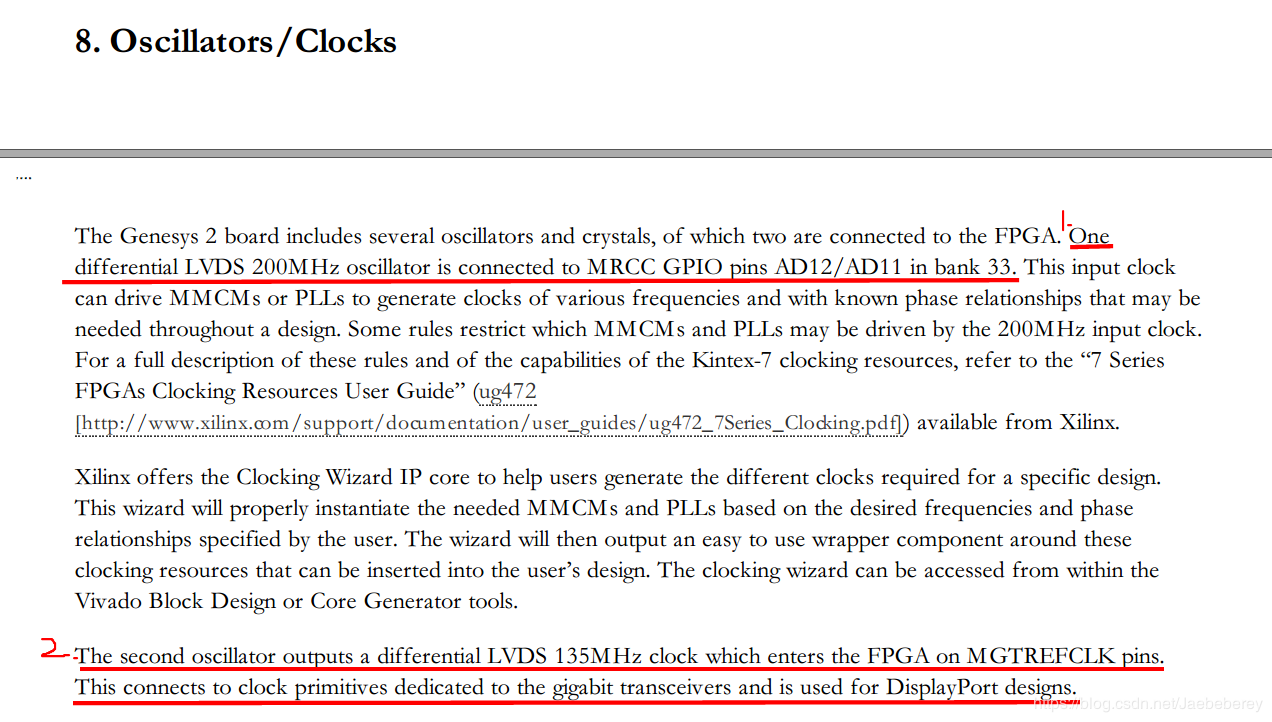

说明中,有两处画红色横线的部分值得注意:

第一句的意思是:一个200MHz的LVDS差分振荡器连接到bank33上面的MRCC GPIO引脚,位置为AD12/AD11。

第二句的意思是:第二个振荡器输出差分LVDS 135MHz时钟,该时钟由MGTREFCLK引脚进入FPGA。它连接到专用于千兆位收发器的时钟原语,并用于DP显示端口设计。(暂时不理解,以后明白了再讨论吧。)

2.因此,可以发现:此开发板的第一个(Primary)输入时钟为200Mhz,引脚为AD11/AD12。(这些信息对于暂时不做显示开发的我来说足够了。)

2.在Vivado2016.4中进行开发板内置时钟IP核的设计与使用

1.添加时钟IP核

1.首先,点击Vivado主界面左侧Project Manger中的IP Catalog,选择我们需要使用的时钟IP核。

2.在出现的IP Catalog选项卡中搜索clk,即时钟。此处选择最后一项,双击即可建立一个新的时钟IP核。

2.时钟IP核的配置

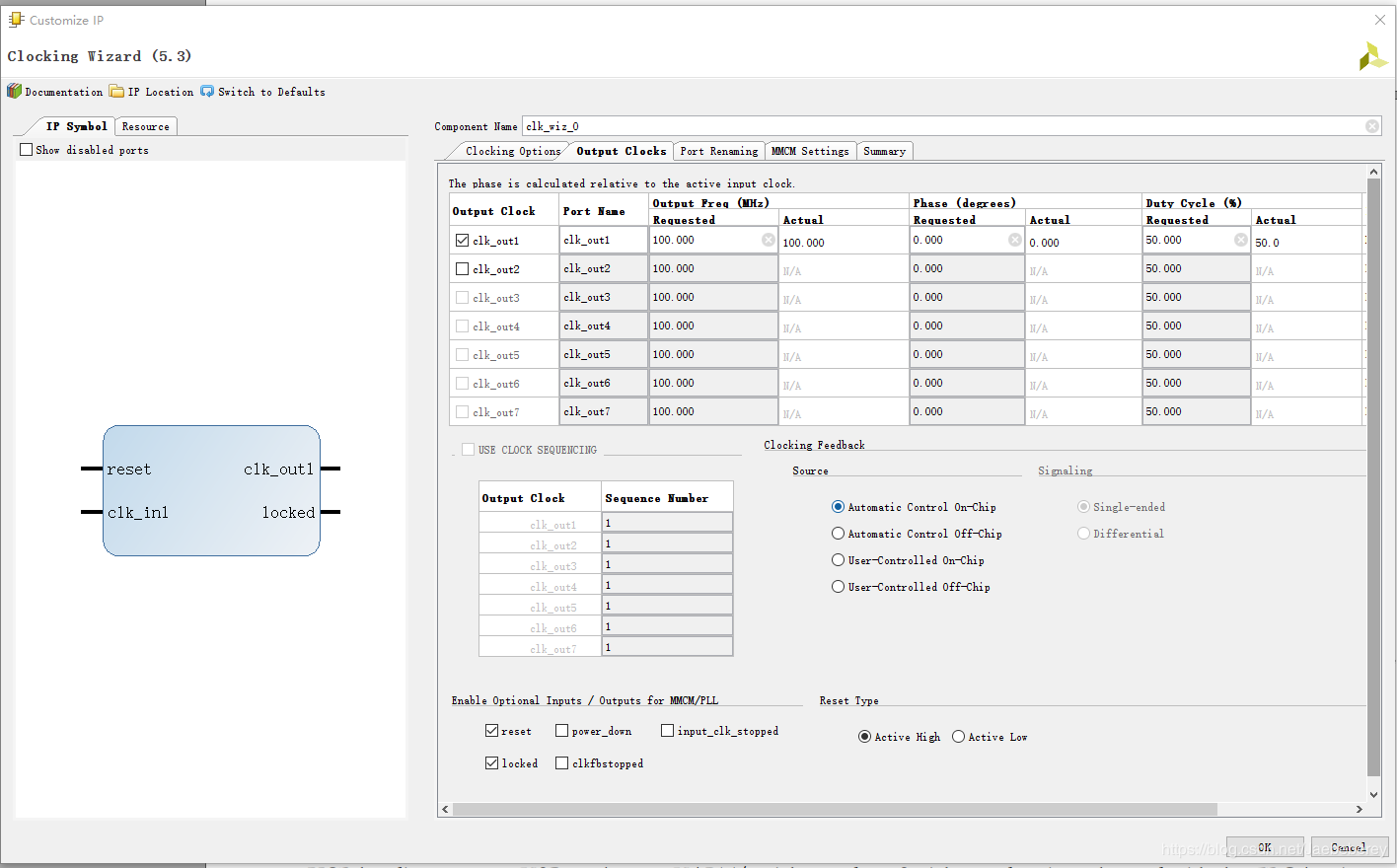

1.上一步结束之后,会出现时钟IP核的配置界面:

第一个是Clocking Options选项卡的默认界面:

第二个是Output Clocks选项卡的默认界面:

2.下面我会根据用户手册中的信息对上面的选项卡内容进行修改。

Clocking Options选项卡:

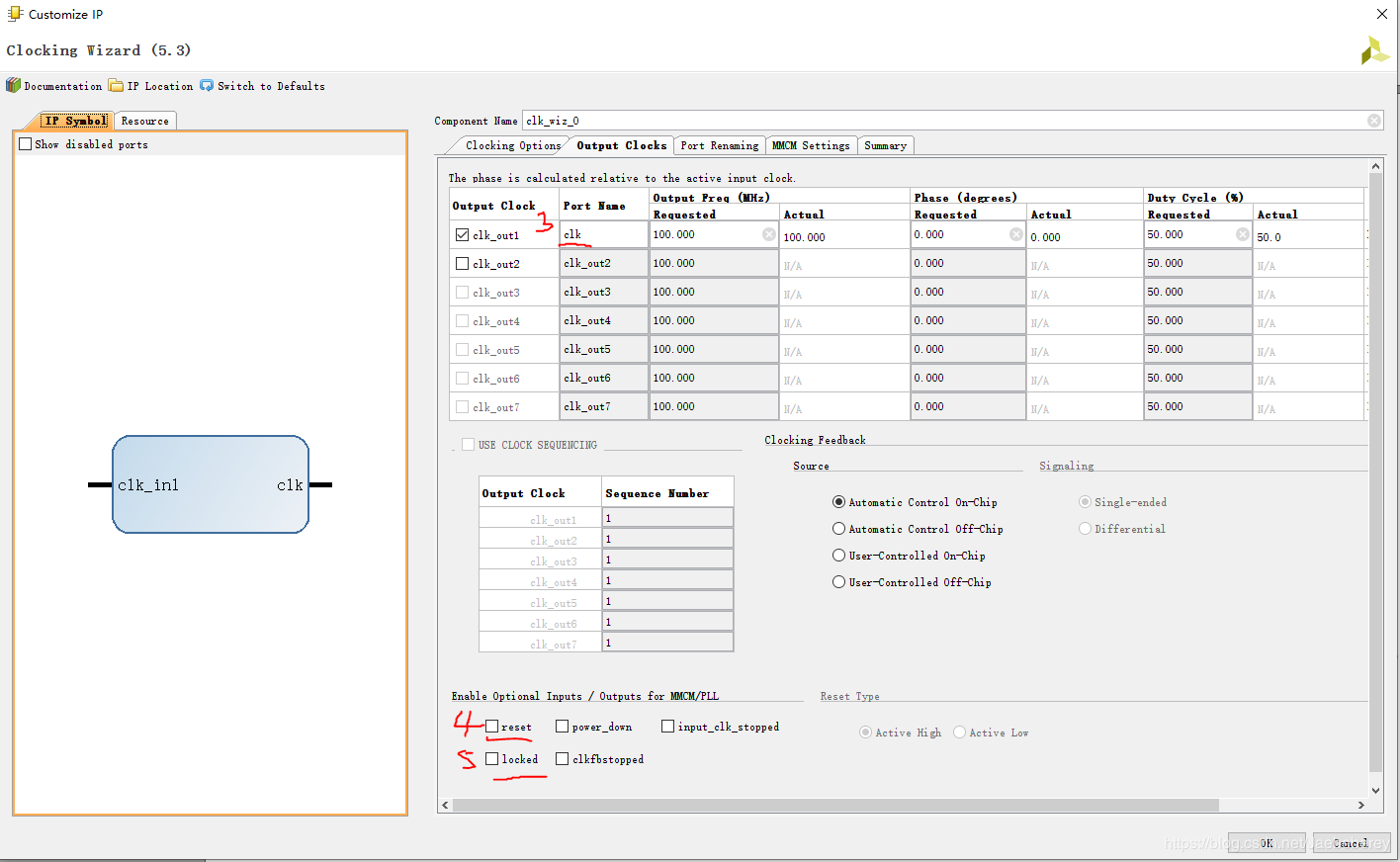

Output Clocks选项卡:

其中画红线的地方,说明一下:

(1)此处使用PLL锁相环时钟;(因为MMCM我不是很清楚)

(2)此处为第一个(Primary)输入时钟,根据用户手册,应设置为200Mhz;

(3)因为我的程序中,输入的时钟信号名为clk,所以此处改成了clk;

(4)reset为输入时钟复位信号,我的程序中没使用,所以取消勾选;

(5)locked信号是指当此晶振产生的时钟信号稳定下来时,产生一个locked信号来表明时钟信号已经稳定。没勾选的原因同上;

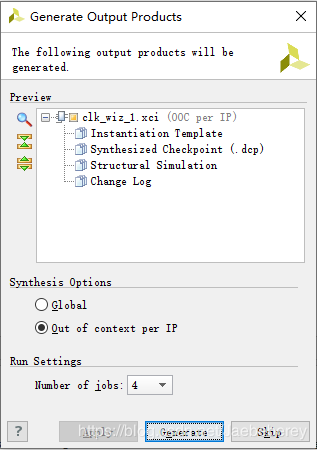

3.上面的修改完毕,我们点击OK,会出现对话框:

点击Generate,就可以生成我们所需要的时钟IP核了。

3.生成的时钟IP核的查看与调用

1.双击Project Manager选项卡中的clk_wiz_0.v文件,即可查看时钟IP核的程序文件:

2.在clk_wiz_0.v程序中,其IP核的时钟接口代码片段为:

// A code part of clk_wiz_0.v

module clk_wiz_0

(

// Clock out ports

output clk,

// Clock in ports

//clk_in_P = ~clk_in1_n

input clk_in1_p,

input clk_in1_n

);

即:输出的信号为clk;输入的信号为clk_in1_p和clk_in1_n,并且互反。

3.在主程序中实例化上面的时钟接口程序,即可完成主程序对时钟IP核的调用:

// A code part of led_s.v

clk_wiz_0 clk_wiz_0

(

// Clock out ports

.clk(clk),

// Clock in ports

.clk_in1_p(clk_in1_p),

.clk_in1_n(clk_in1_n)

);

4.经过以上过程,完整的时钟IP核创建与调用就结束了。

3.总结

在使用开发板时,一定要仔细阅读开发手册,注意其时钟信息以及其他各种有用的资源,这样不仅可以让开发更加便捷,同时也可以避免许多不必要的错误。