本文转载自:根究FPGA的微信公众号

Block RAM与Distributed RAM,简称为BRAM与DRAM, 要搞清楚两者的区别首先要了解FPGA的结构:

FPGA=CLB + IOB+Block RAM CLB

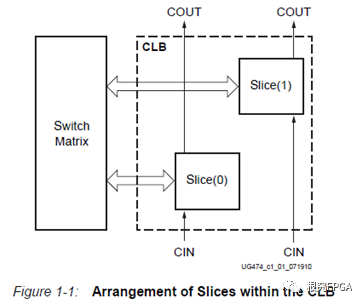

一个CLB中包含2个Slice、8位寄存器、多路选择器、进位链等。

作为CLB的基本单元,Slice分为SliceL和SliceM两种类型,SliceL即Slice of Logice,可用于产生逻辑、算数、rom等。SliceM算是SliceL的升级版,除了具有SliceL的功能之外还可以配置成64bit分布式RAM(64bit Distributed RAM)或16/32位的移位寄存器。每个CLB包含两个SliceL或者一个SliceL+一个SliceM。Slices中SliceL占比大概是2/3,剩下的是SliceM。

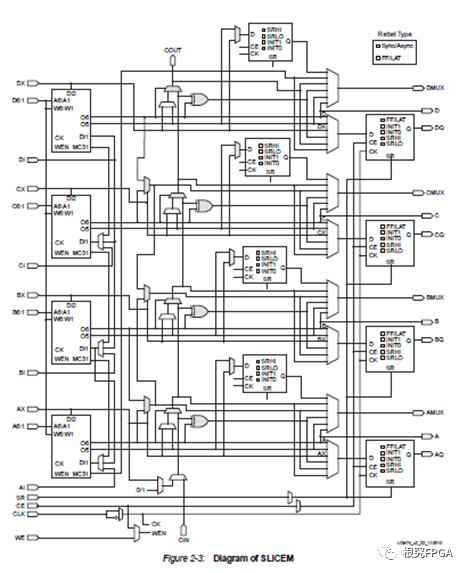

SLiceM结构:

SliceM中含有Distributed RAM资源,而SliceL中不包含DRAM资源:

Xilinx的FPGA中包含Distributed RAM和Block RAM两种寄存器,Distributed RAM需要使用SliceM,所以要占用CLB中的逻辑资源,而Block RAM是单独的存储单元,要一块一块的使用,不像分布式RAM那样用多少bit都可以。

用户申请资源时,FPGA先提供Block RAM,当Block RAM不够时再提供分布式RAM进行补充。Block RAM是单独的RAM资源,一定需要时钟,而Distributed RAM可以是组合逻辑,即给出地址马上给出数据,也可以加上register变成有时钟的RAM,而Block RAM一定是有时钟的。

两者区别总结:

1、 bram需要时钟,dram给出地址后即可输出数据。

2、 dram使用更灵活方便些。

3、 bram有较大的存储空间,dram浪费LUT资源。

4、 如果要产生较大的FIFO或timing要求较高就用bram,否则,就可以用dram。

5、 在异步fifo ,用两种RAM可供选择,BRAM和DRAM,BRAM是FPGA中整块的双口RAM资源,DRAM是拼接LUT构成。