作者:brank_z

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/a52228254/article/details/103445142

本节文章参考的代买为xilinx github上vitis 的事例工程,主要是讲解如何写用户自己的rtl kernel,具体参考链接如下:

https://github.com/Xilinx/Vitis_Accel_Examples/blob/master/rtl_kernels/r...

话不多说,直接上顶层的rtl代码。

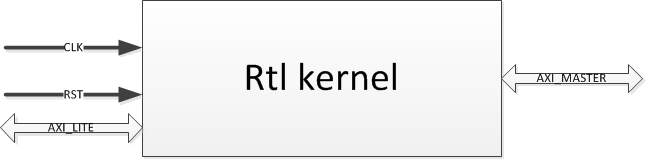

本节事例是针对如下的kernel形式

对外接口主要分为时钟,复位,axi_lite口,和axi_master口,这是最简单的rtl kernel形式,其中左边的部分对时钟部分可以扩张,具体为多时钟的kernel,右边也可以具有多个axi_master接口。

时钟和复位:

input wire ap_clk,//建议直接按照此方式命名自己的kernel时钟和复位

input wire ap_rst_n,

axi_lite口:

// AXI4-Lite slave interface

input wire s_axi_control_AWVALID,

output wire s_axi_control_AWREADY,

input wire [C_S_AXI_CONTROL_ADDR_WIDTH-1:0] s_axi_control_AWADDR,

input wire s_axi_control_WVALID,

output wire s_axi_control_WREADY,

input wire [C_S_AXI_CONTROL_DATA_WIDTH-1:0] s_axi_control_WDATA,

input wire [C_S_AXI_CONTROL_DATA_WIDTH/8-1:0] s_axi_control_WSTRB,

input wire s_axi_control_ARVALID,

output wire s_axi_control_ARREADY,

input wire [C_S_AXI_CONTROL_ADDR_WIDTH-1:0] s_axi_control_ARADDR,

output wire s_axi_control_RVALID,

input wire s_axi_control_RREADY,

output wire [C_S_AXI_CONTROL_DATA_WIDTH-1:0] s_axi_control_RDATA,

output wire [1:0] s_axi_control_RRESP,

output wire s_axi_control_BVALID,

input wire s_axi_control_BREADY,

output wire [1:0] s_axi_control_BRESP

lite口也比较好理解,所有的kernel 的寄存器都需要从lite口设置下来。

axi_master口:

// AXI4 master interface

output wire m_axi_gmem_AWVALID,

input wire m_axi_gmem_AWREADY,

output wire [C_M_AXI_GMEM_ADDR_WIDTH-1:0] m_axi_gmem_AWADDR,

output wire [C_M_AXI_GMEM_ID_WIDTH - 1:0] m_axi_gmem_AWID,

output wire [7:0] m_axi_gmem_AWLEN,

output wire [2:0] m_axi_gmem_AWSIZE,

// Tie-off AXI4 transaction options that are not being used.

output wire [1:0] m_axi_gmem_AWBURST,

output wire [1:0] m_axi_gmem_AWLOCK,

output wire [3:0] m_axi_gmem_AWCACHE,

output wire [2:0] m_axi_gmem_AWPROT,

output wire [3:0] m_axi_gmem_AWQOS,

output wire [3:0] m_axi_gmem_AWREGION,

output wire m_axi_gmem_WVALID,

input wire m_axi_gmem_WREADY,

output wire [C_M_AXI_GMEM_DATA_WIDTH-1:0] m_axi_gmem_WDATA,

output wire [C_M_AXI_GMEM_DATA_WIDTH/8-1:0] m_axi_gmem_WSTRB,

output wire m_axi_gmem_WLAST,

output wire m_axi_gmem_ARVALID,

input wire m_axi_gmem_ARREADY,

output wire [C_M_AXI_GMEM_ADDR_WIDTH-1:0] m_axi_gmem_ARADDR,

output wire [C_M_AXI_GMEM_ID_WIDTH-1:0] m_axi_gmem_ARID,

output wire [7:0] m_axi_gmem_ARLEN,

output wire [2:0] m_axi_gmem_ARSIZE,

output wire [1:0] m_axi_gmem_ARBURST,

output wire [1:0] m_axi_gmem_ARLOCK,

output wire [3:0] m_axi_gmem_ARCACHE,

output wire [2:0] m_axi_gmem_ARPROT,

output wire [3:0] m_axi_gmem_ARQOS,

output wire [3:0] m_axi_gmem_ARREGION,

input wire m_axi_gmem_RVALID,

output wire m_axi_gmem_RREADY,

input wire [C_M_AXI_GMEM_DATA_WIDTH - 1:0] m_axi_gmem_RDATA,

input wire m_axi_gmem_RLAST,

input wire [C_M_AXI_GMEM_ID_WIDTH - 1:0] m_axi_gmem_RID,

input wire [1:0] m_axi_gmem_RRESP,

input wire m_axi_gmem_BVALID,

output wire m_axi_gmem_BREADY,

input wire [1:0] m_axi_gmem_BRESP,

input wire [C_M_AXI_GMEM_ID_WIDTH - 1:0] m_axi_gmem_BID,

按照axi4协议的master口,当然无论是vitis还是sdaccel还需要其他文件来完成集成在shell的工作

其他需要的文件:

(1)xml文件,需要在内部描述kernel寄存器的偏移地址,这样才能让host找到对应的寄存器

(2)package_ip.tcl. 需要将rtl的源文件打包成IP,当然也可以把对应的IP直接用vivado打包好,不过笔者亲测这种方式有些问题,有些文件会找不到

(3)gen_xo.tcl,将IP变为xo文件,xilinx_object,这样vitis和sdaccel会把kernel当成一个lib。

(4)platform文件,对于u200,U50等X86板卡,可以直接从官网下载shell,对于嵌入式端,也可以从官网下载

(5)makefile,这个不用多说了

在整个集成过程中还是会存在各种各种的问题,可以依据xilinx 的github的example多多研究,可能可以解决。