作者:falwat

版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/falwat/article/details/86171571

本文介绍如何在教程(三)基础上, 关联ELF输出文件并使用vivado对系统进行行为仿真。

关联ELF 文件

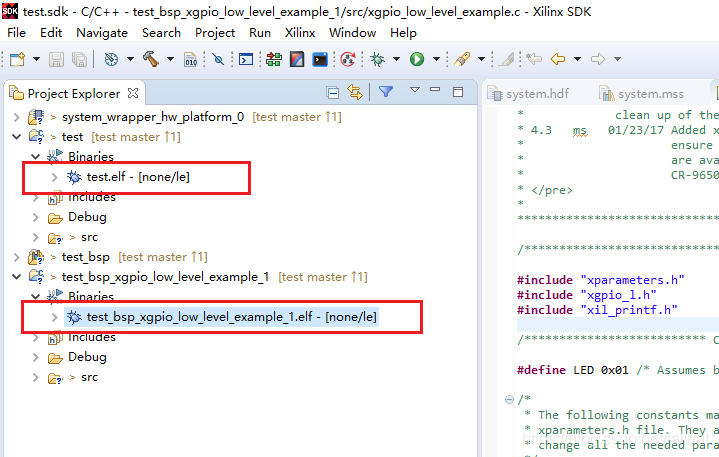

在vivado 开发教程(三) 在SDK中创建应用工程 中, 新建的工程经构建最终会生成ELF 输出文件. ELF 文件是一种用于二进制文件、可执行文件、目标代码、共享库和核心转储格式文件(参考:百度百科). 可以在教程(三)中新建的"test"工程和导入的例程下找到.

切回Vivado, 在块设计文件"system.bd"上右键,选择菜单"Associate ELF Files..."关联ELF文件.

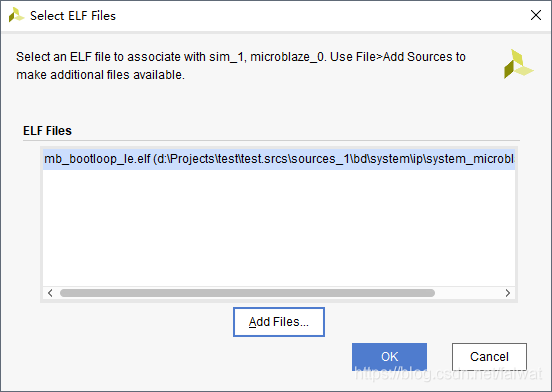

在弹出的对话框中,点击"Simulation Sources | sim_1 | system_i | microblaze_0 "树右侧的"..."按钮, 弹出选择文件对话框.

点击"Add Files..." 按钮,添加ELF文件.

切换目录至"D:/Projects/test/test.sdk/test_bsp_xgpio_low_level_example_1/Debug",选中"test_bsp_xgpio_low_level_example_1.elf", 添加至列表中, 选中新加入的ELF文件并点击"OK"完成.

在工程管理视图 | "Sources"窗口 | "Simulation Sources"文件集 | sim_1 | ELF 下能够看到刚刚关联上去的ELF文件.

新建激励文件

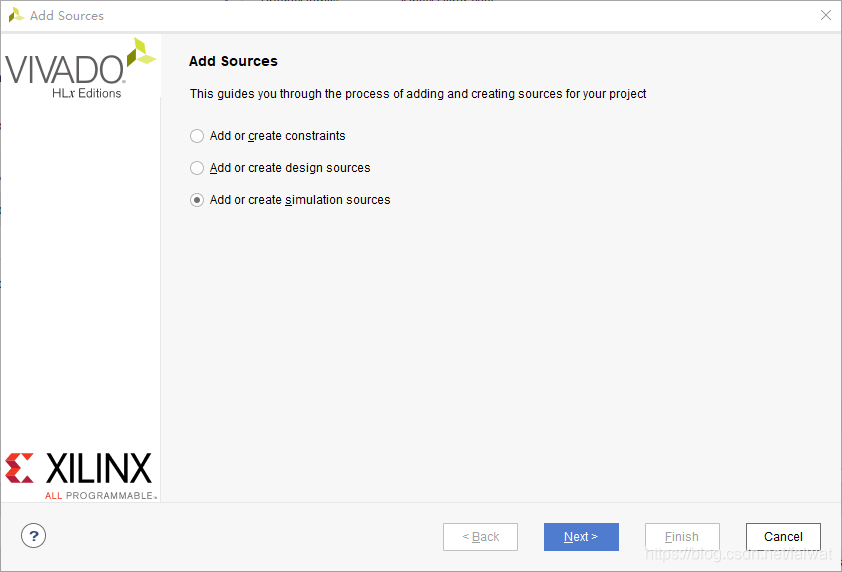

点击"Sources"窗口顶部的"+"按钮, 打开添加源文件对话框. 选中"Add or create simulation sources", 点击"Next"继续.

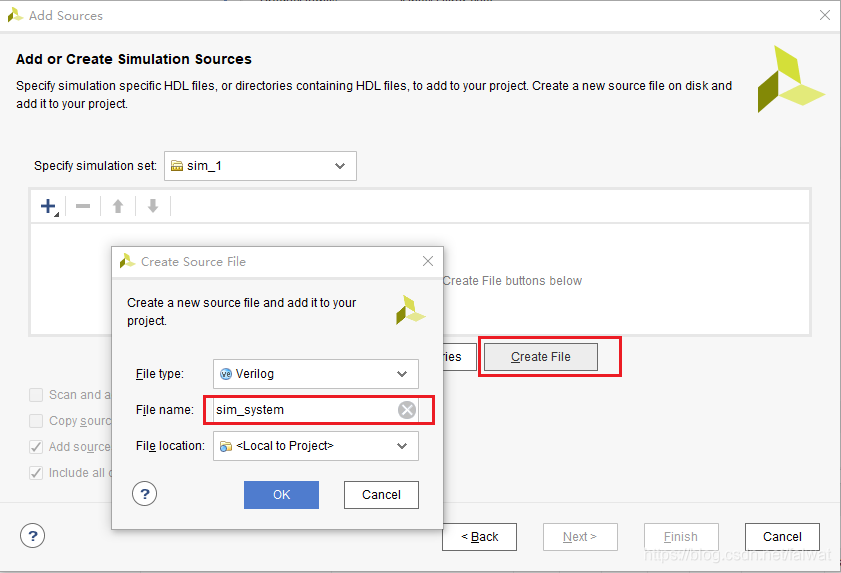

点击"Create File"按钮, 在创建源文件对话框中, 输入文件名. 点击"OK", 点击"Finish".

在弹出的"Define Module"对话框中, 点击"OK"即可. 激励文件不需要有定义输入输出端口.

双击打开"sim_system.v"文件, 复制"system_wrapper.v"文件中的如下内容到"sim_system.v"的模块中.

wire [7:0]led_8bits_tri_o;

wire reset;

wire rs232_uart_rxd;

wire rs232_uart_txd;

wire sysclk_125_clk_n;

wire sysclk_125_clk_p;

system system_i

(.led_8bits_tri_o(led_8bits_tri_o),

.reset(reset),

.rs232_uart_rxd(rs232_uart_rxd),

.rs232_uart_txd(rs232_uart_txd),

.sysclk_125_clk_n(sysclk_125_clk_n),

.sysclk_125_clk_p(sysclk_125_clk_p));修改sim_system.v"文件中, system_i的输入信号为"reg"类型, 编写"initial"块对输入信号进行初始化, 为时钟信号编写激励, 将"timescale" 设置为"1ns / 1ns". 最终生成的代码如下所示:

`timescale 1ns / 1ns

module sim_system;

wire [7:0]led_8bits_tri_o;

reg reset;

reg rs232_uart_rxd;

wire rs232_uart_txd;

reg sysclk_125_clk_n;

wire sysclk_125_clk_p = ~sysclk_125_clk_n;

system system_i

(.led_8bits_tri_o(led_8bits_tri_o),

.reset(reset),

.rs232_uart_rxd(rs232_uart_rxd),

.rs232_uart_txd(rs232_uart_txd),

.sysclk_125_clk_n(sysclk_125_clk_n),

.sysclk_125_clk_p(sysclk_125_clk_p));

initial begin

reset = 1;

rs232_uart_rxd = 1;

sysclk_125_clk_n = 0;

#100;

reset = 0; // 复位完成

end

always #4 sysclk_125_clk_n = ~sysclk_125_clk_n; // 125M

endmodule

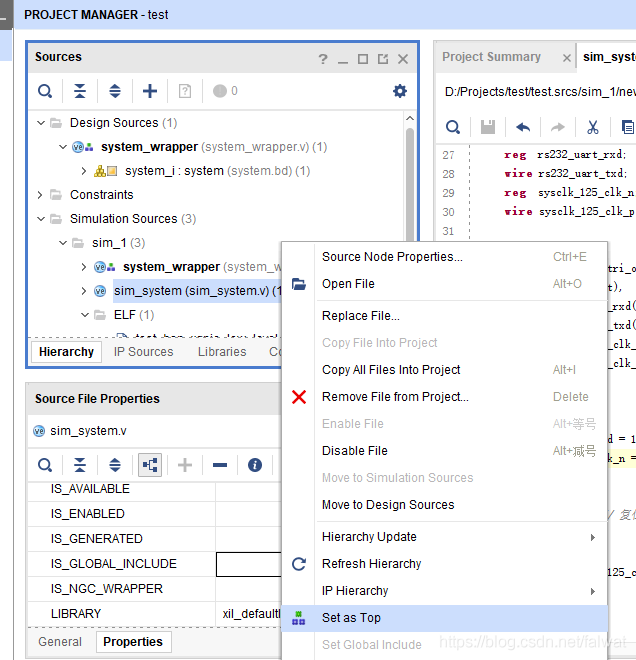

从"Source"窗口中,选中激励文件"sim_system.v", 右键选择菜单"Set as Top", 将激励文件设置为顶层.

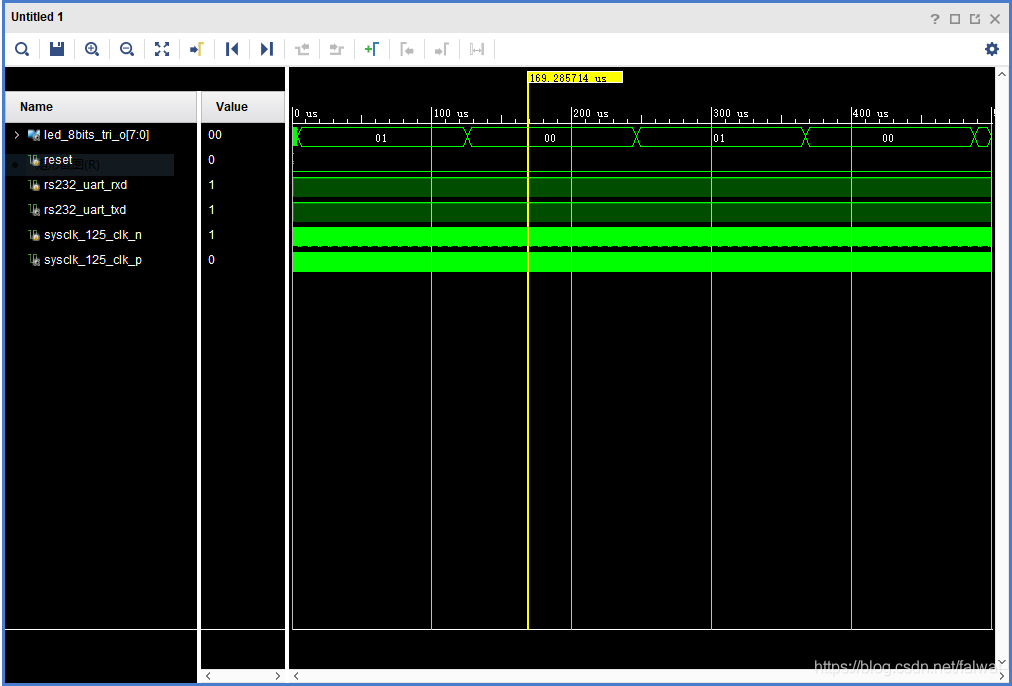

点击左侧"Flow Navigator"工具窗口中的"Simulation" | "Run Simulation", 点击"Run Behavioral Simulation", 运行行为仿真.

编译成功后会自动打开仿真("SIMULATION")视图, 主工具栏会增加如下几个工具图标:

为了能够快速看出仿真效果,缩短仿真时间, 在SDK 中修改"xgpio_low_level_example.c"文件中的宏常量"LED_DELAY" 改为1000 并保存, SDK在保存后会自动进行编译, 更新ELF文件.

#define LED_DELAY 1000

切回Vivado, 点击重新仿真("Relaunch Simulation")按钮.

设置仿真时间为500us, 点击运行指定时间("Run for 500us")按钮.最终的仿真时序图如下所示.