本文转载自:ZYNQ微信公众号

ILA 简介

集成逻辑分析仪 (Integrated Logic Analyzer :ILA) 功能允许用户在 FPGA 设备上执行系统内调试后实现的设计。当设计中需要监视信号时,应使用此功能。用户还可以使用此功能在硬件事件和以系统速度捕获数据时触发。

添加 ILA

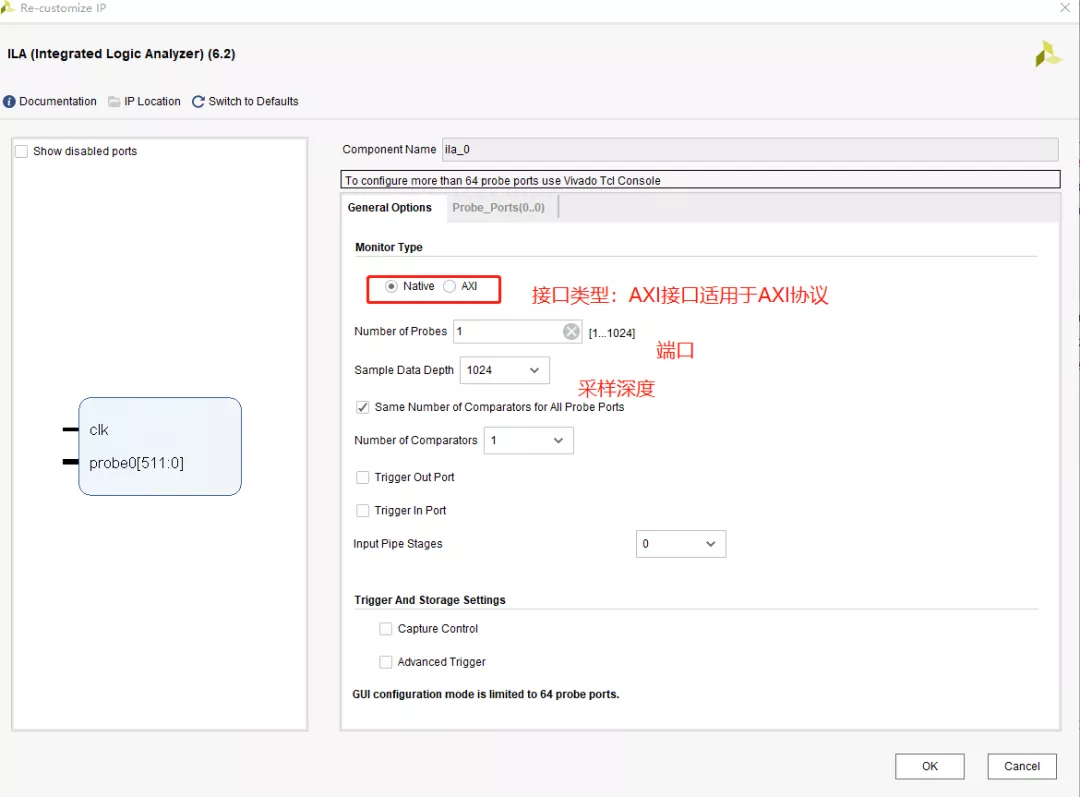

1.使用 IP 添加

添加IP

例化IP,并将所需要的信号放入 Probe 里面

2.图形界面添加

给待测试的信号加上约束,防止被优化

在综合选项下点击set up debug,选择需要查看的信号即可

ILA 数据和波形的关系

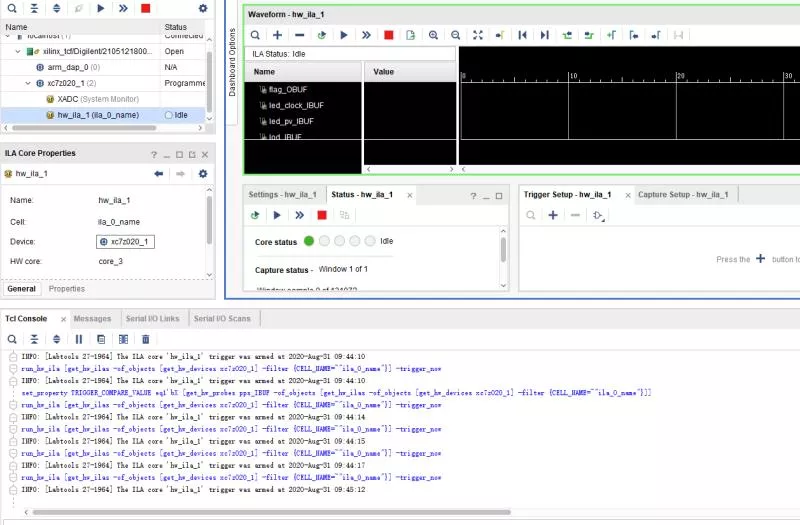

1. hw_ila表示的是ila核

2. hw_ila_data表示保存在存储器中的ila文件

3. WCFG是波形配置(信号颜色,总线进制表示,信号顺序,marker等)

4. WDB是波形数据库(波形数据)

ILA 失败情景

情景1:没有波形窗口

现象如下:

WARNING: [Labtools 27-3123] The debug hub core was not detected at User Scan Chain 1 or 3.

Resolution:

1. Make sure the clock connected to the debug hub (dbg_hub) core is a free running clock and is active OR

2. Manually launch hw_server with -e "set xsdb-user-bscan

WARNING: [Labtools 27-1974] Mismatch between the design programmed into the device xc7z010_1 and the probes file E:/Xilinx/example/dma_sg_m/dma_sg_m.runs/impl_1/debug_nets.ltx.

The device design has 0 ILA core(s) and 0 VIO core(s). The probes file has 1 ILA core(s) and 0 VIO core(s).

Resolution:

1. Reprogram device with the correct programming file and associated probes file OR

2. Goto device properties and associate the correct probes file with the programming file already programmed in the device.

解决方法:查看 ILA 的时钟,如果不是自由时钟会出现这种问题,然后重启VIVADO软件,重新打开

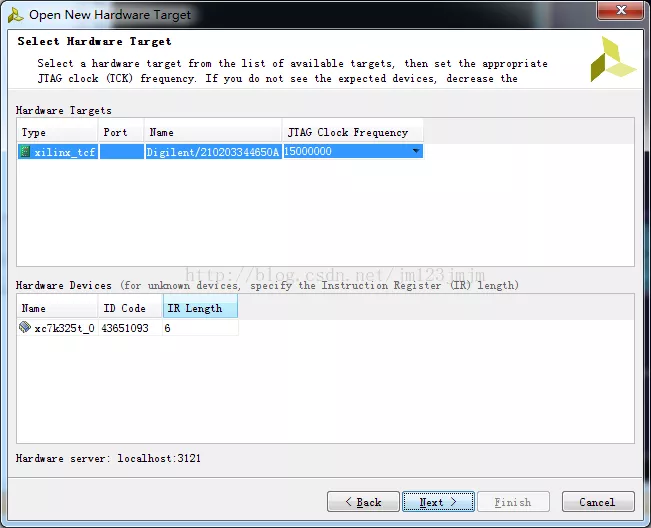

情景2:有波形窗口没有波形

现象如下:

使用示波器查看ILA信号发现时钟频率发现是10M

分析:查看 Xilinx 手册发现JATG的时钟频率要比被ILA的时钟频率2.5倍低

解决方法1:修改 Hardware Target 的 JTAG 时钟频率

解决方法2:在TCL里面添加约束

上电后查看 ILA 信号

使用场景:flash偶尔在上电后读出来后出错,可以使用该方法。

一般情况下都是让要抓的事件延迟发生或者循环发生,方便调试。

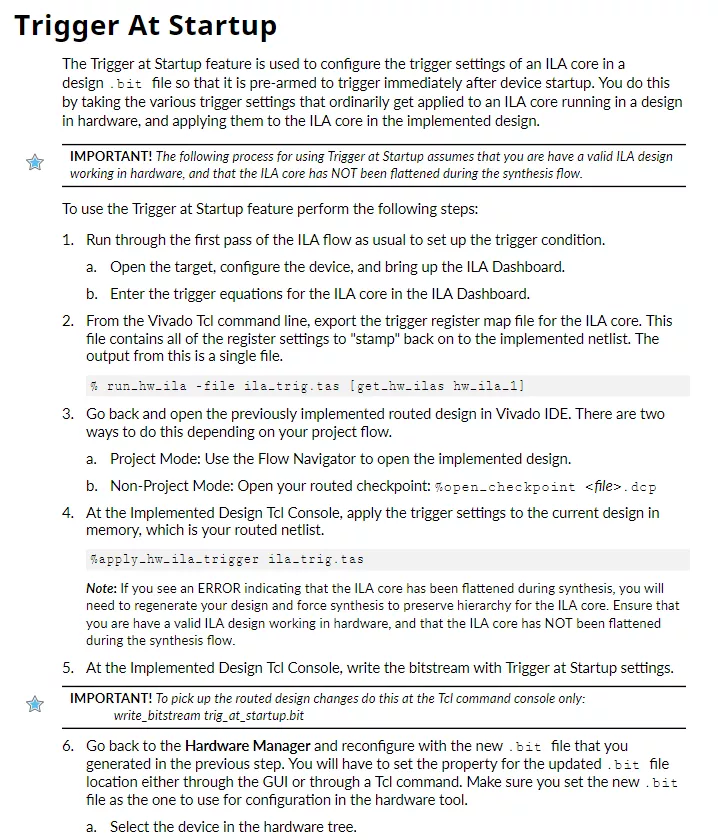

如果实在要抓启动时的事件,按下面的步骤:(下面流程是ILA核在综合阶段不能浮空)

先把有ILA核的bit文件下进去,设置触发好条件

运行下面的Tcl命令把触发寄存器的值保存在tas文件中

%run_hw_ila -file ila_trig.tas [get_hw_ilas hw_ila_1]

打开实现后的implement工程

运行下面的Tcl命令把触发设置加到当前内存里已经布线的implement设计上去

%apply_hw_ila_trigger ila_trig.tas

注意:如果发生错误的话说明ILA核在综合过程中被flattened了,这时需要设置保留hierarchy重新综合实现。

直接用Tcl命令生成bit文件,不能点击生成bit命令,这样工程会认为implement发生了改动而全部重新布线。

write_bitstream trig_at_startup.bit

下载bit到芯片。

参考链接

chrome-extension://ibllepbpahcoppkjjllbabhnigcbffpi/https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug9...

chrome-extension://ibllepbpahcoppkjjllbabhnigcbffpi/https://www.xilinx.com/support/documentation/sw_manuals/xilinx2020_1/ug9...