本文转载自:ZYNQ微信公众号

接线连接

I/O 信号可通过 MIO 引脚获得, Quad-SPI 控制器在共享或单独的总线配置中最多支持两个 SPI 闪存, 控制器支持以多种配置运行:

注意:如果要使用 QSPI 存储器子系统,则 QSPI 0 应始终存在。QSPI 1 是可选的,仅在两内存排列时才需要。因此,不能单独使用 QSPI_1

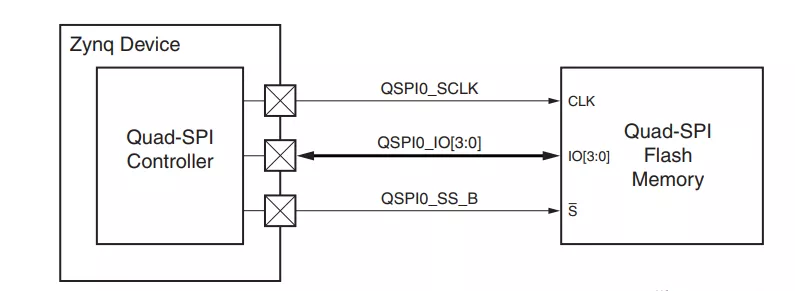

单 SS,4 位 I/O

连接到控制器配置的 4 位闪存接口的框图如下所示,此配置支持就地执行功能。

Quad-SPI Single SS 4-bit I/O

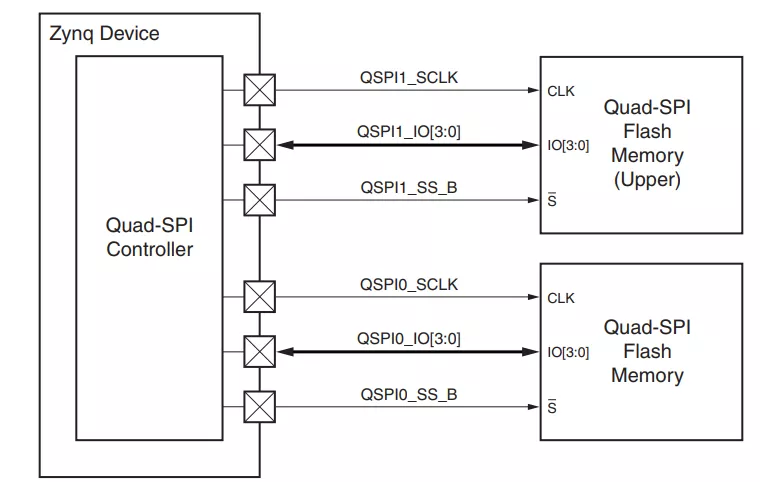

双 SS,8 位并行

控制器最多支持两个并行运行的 SPI 闪存,如图所示,此配置将最大可寻址 SPI 闪存从 16 MB(24 位寻址)增加到 32 MB(25 位寻址),此配置不支持就地执行功能。

Quad-SPI Dual SS, 8-bit Parallel I/O

对于 8 位并行配置,数据字的偶数位位于低位存储器中,而数据的奇数位位于高位存储器中。控制器负责 I/O 和线性模式下的数据管理。Quad-SPI 控制器在将状态数据写入 RXFIFO 之前从两个 Quad-SPI 设备和 OR(或操作)读取两个设备的状态信息。

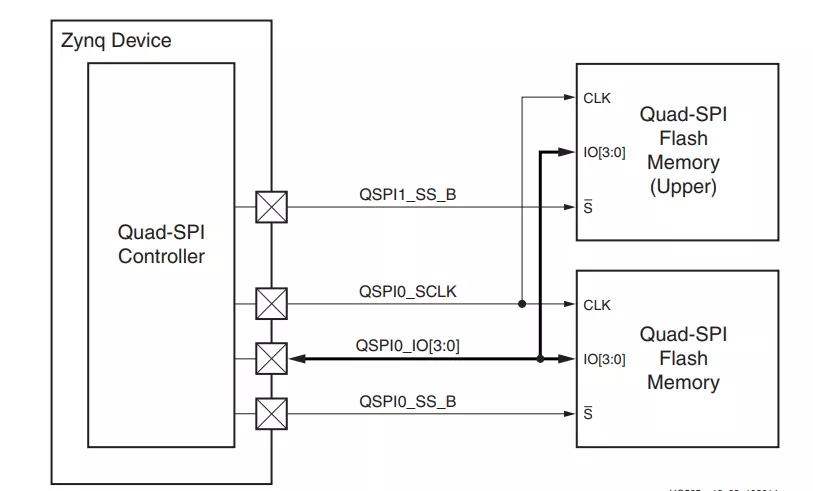

双 SS、4 位堆叠 I/O

为了减少 I/O 引脚数,控制器还在共享总线配置中支持最多两个 SPI 闪存,如下图所示。

Quad-SPI Dual SS 4-bit Stacked I/O

此配置将最大可寻址 SPI 闪存从 16 MB(24 位寻址)增加到 32 MB(25 位寻址),但吞吐量与单内存模式相同,请注意,在此配置中,不支持设备级 XIP 模式(读取 0xBB 和 0xEB 指令代码)。

如果使用线性 Quad-SPI 存储器子系统,则应始终连接下层 SPI 闪存,上层闪存是可选的, 总地址空间为 32 MB,具有 25 位地址。

在 IO 模式下,地址的 MSB 由位于寄存器 0xA0 的第 28 位的 U_PAGE 定义。

在线性地址模式下,AXI 地址位 24 决定内存页的高位或低位,所有命令都将由 U_PAGE 在 I/O 模式和地址位 24 中选择的设备执行线性模式。

单 SS,传统 I/O

Quad-SPI 控制器可以在传统的单比特串行接口模式下运行,用于 1x、2x 和 4x I/O 模式,如图所示。

Quad-SPI Single SS, Legacy I/O