本文转载自: 硬码农二毛哥微信公众号

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。

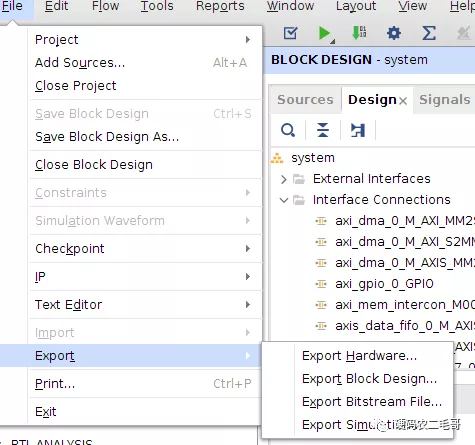

导出硬件平台

在完成硬件平台搭建后,File-> Export->Export Hardware,选择Fixed,include bitstream,导出.xsa文件。

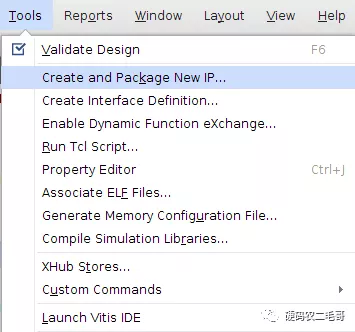

在Vitis中新建工程

在Vivado中打开Vitis,Tool->Launch Vitis IDE,在Workspace中输入Vitis工作目录。

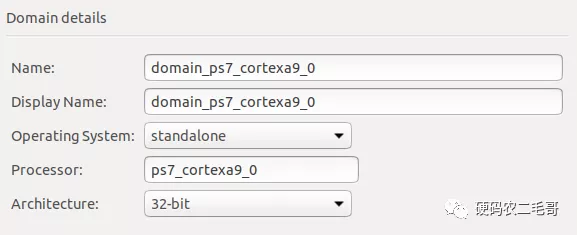

点击Create Application Project,选择Create a new platform from hardware(XSA),选择之前生成的.xsa文件,新建工程zynq7035。

新建Empty Application,Finish。

编写裸机软件代码

建立好工程后,在src中加入软件代码,点击Import Sources,选择编写好的代码。

编译代码,Build Project。

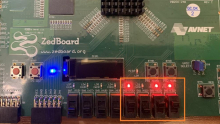

Vivado和Vitis联合调试

使用Vivado和Vitis联合调试分为以下步骤:

在vitis中运行调试程序

右击工程文件,Debug as->1,进入调试界面

在vivado中下载程序

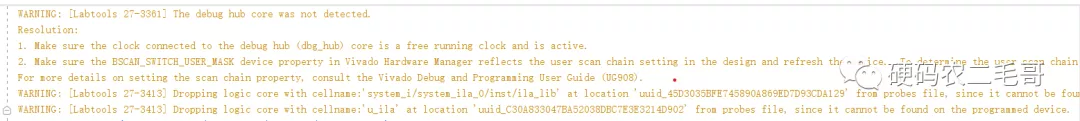

同时下载.bit和ltx文件,下载后遇到如下问题:

在Vitis中运行一下软件代码,然后refresh device可以解决。原因也很好理解,ila时钟使用PS输出,PS先运行后才能输出时钟。

在vitis中单步运行程序

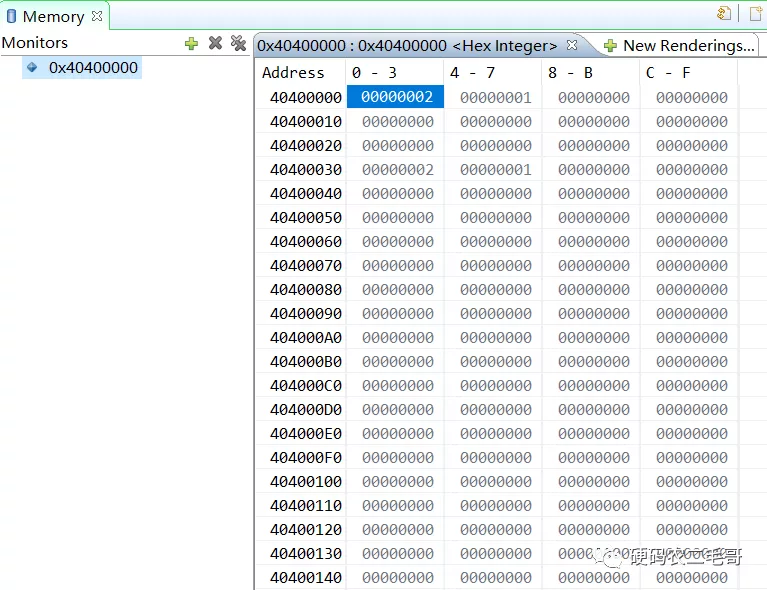

在Window中点击Memory,输入要查看数据在内存中的地址,在Memory中查看数据。

单步运行程序程序

重复上述过程,完成代码调试。