作者:搞FPGA开发的Tony老师,文章来源:CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

之前很早就听说了FSMC(Flexible static memory controller)接口用于MCU与FPGA之间的通讯。

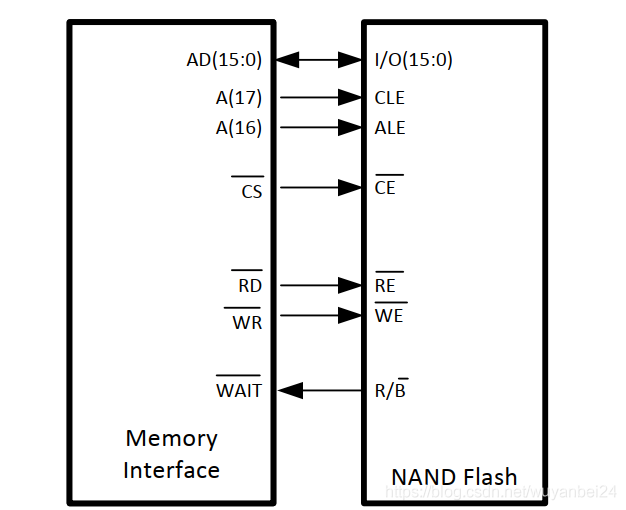

最近使用的一款MCU与FPGA之间通讯,FPGA模拟成NAND Flash作为Memory让MCU读写

FPGA与MCU之间的连接方式如下所示

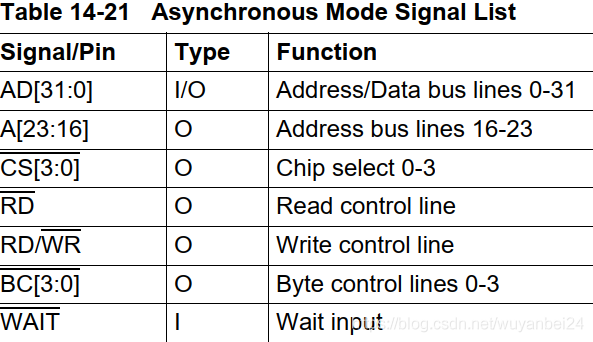

上述信号定义如下

这里可以看到,NAND flash接口,Master和Memory之间是没有同步时钟的,是根据控制信号的边沿来产生控制逻辑的。但是这些控制信号在Master侧是时种下,同步产生的。同理反推,在Memory内部也应该有相应的时钟将外部的异步信号同步化,然后产生对应的控制逻辑。

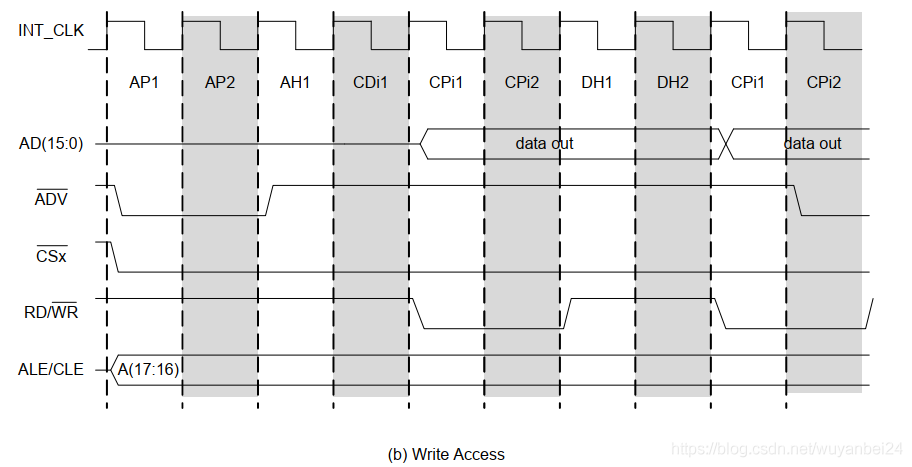

所以在设计中,FPGA内部采用一个高速的时钟对MCU发出的FSMC总线信号进行采样,根据时序完成读写访问。

读操作时序

写操作时序

MCU侧开发注意事项

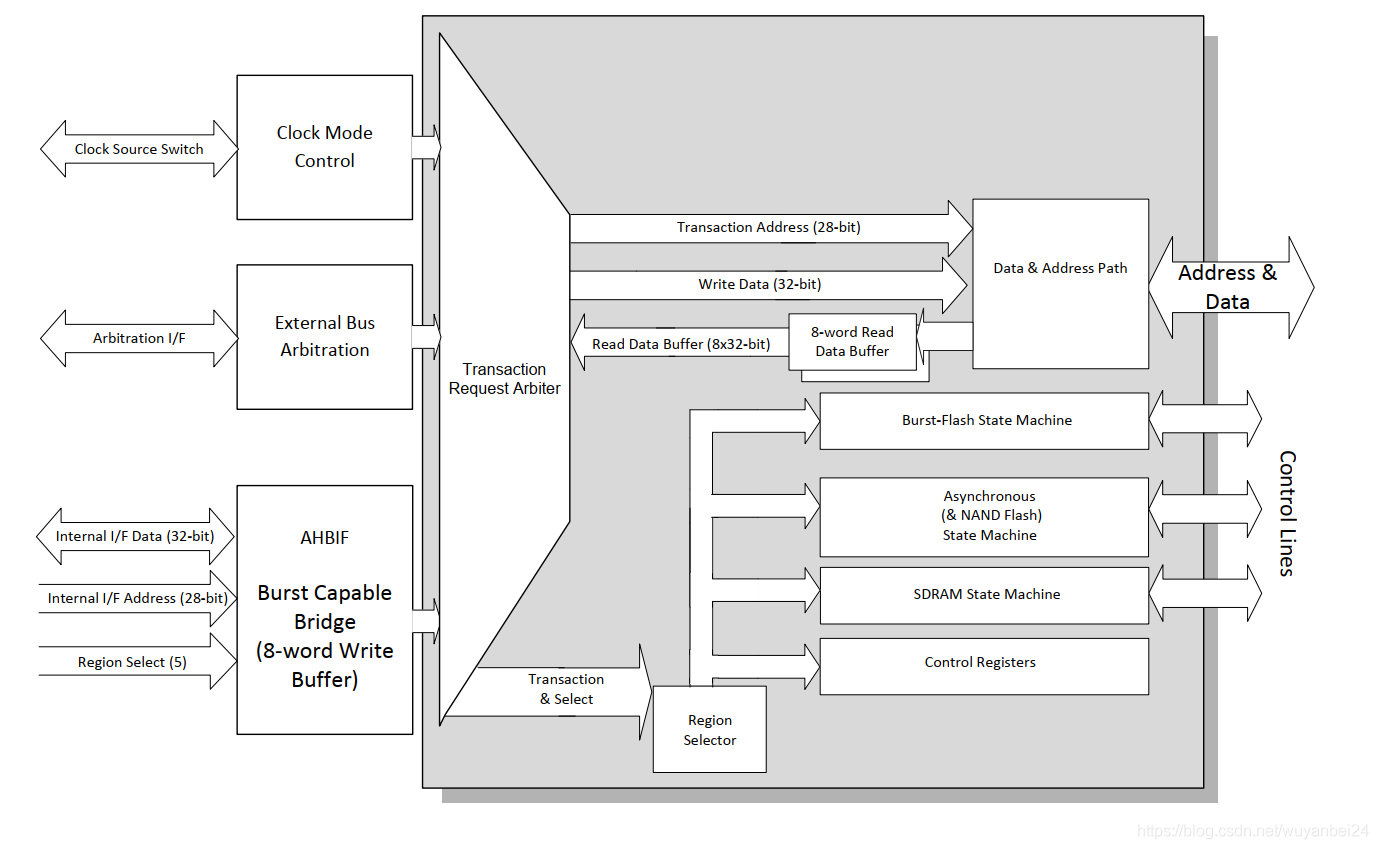

可以看到,MCU将外部存储接口通过AHB总线与系统相连,在调试的时候,MCU侧开发人员需要注意AHB的总线位宽和外设存储位宽在地址、数据上的转换关系。

在调试过程中,发现MCU厂商直接提给用户M4的外设的绝对地址供用户使用,所以在使用时,需要注意地址必须按照4字节对齐进行访问,否则总线会出现莫名其妙的异常。AHB总线默认是4字节地址对齐,通过strobe信号确定4字节中有效的字节。

FPGA侧注意事项

在完成测试寄存器初步单次读写后,压力测试中,发现MCU访问FPGA会时不时出现错误。

检查了FPGA 与MCU之间的连线,发现FSMC接口之间没有做等长约束,导致最长的信号和最短的信号相差近1000个MIL,所以要求MCU侧降低内部的总线频率,增加地址周期、数据周期的时钟周期个数。

在执行了上述操作以后,发现FPGA软件不做改动的情况先多次编译,有一个版本比较好用,压力测试总是能通过,根据经验,这必然是多次编译布局布线导致时序不一致引入的问题。

打开综合后的timing report,发现FSMC接口严重警告,没有约束输入输出时间。但是作为外部输入的异步信号,确实没办法约建立和保持时间,因为是采用控制信号的边沿去取地址、数据的。

那么信号从FPGA的PAD到内部Logic之间,如果不经过IOB则会存在很大随机性。于是在约束中针对所有的输入和输出加上了IOB为true的约束,经过测试,问题得以解决。

set_property IOB TRUE [all_inputs]

set_property IOB TRUE [all_outputs]

以后针对xilinx的器件,尽可能的把IOB约束加上,减少随机的因素。