作者:FPGA技术实战,文章来源:CSDN博客

注:本文由作者授权转发,如需转载请联系作者本人

说明:我们在设计外设和Xilinx 7系列FPGA互联时,经常会用到LVDS接口。如何正确的保证器件之间的互联呢?本博文整理了Xilinx官方相关技术问答,希望能给开发者一些指导。

1. Xilinx-7系列FPGA差分信号接口

Xilinx 7系列FPGA提供了两种I/O Bank:高性能(HP)I/O Bank和宽压范围(HR)I/O Bank。

HP I/O Bank: 支持最大VCCO 电压为1.8V,LVDS为HP I/O Bank差分信号电平

HR I/O Bank: 支持最大VCCO 电压为3.3V,LVDS_25为HR I/O Bank差分信号电平

表1、LVDS_25电平DC特性

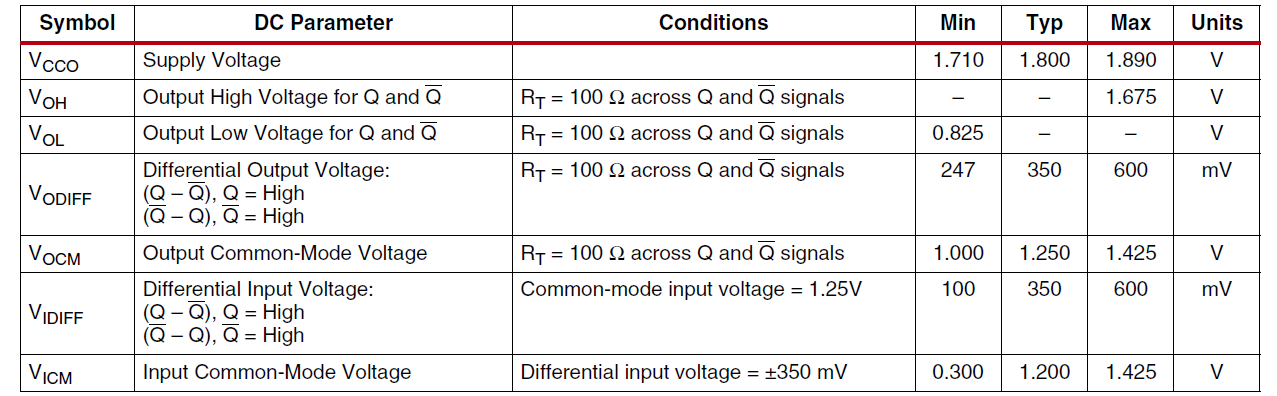

表2、LVDS电平DC特性

2. 差分接口检查表

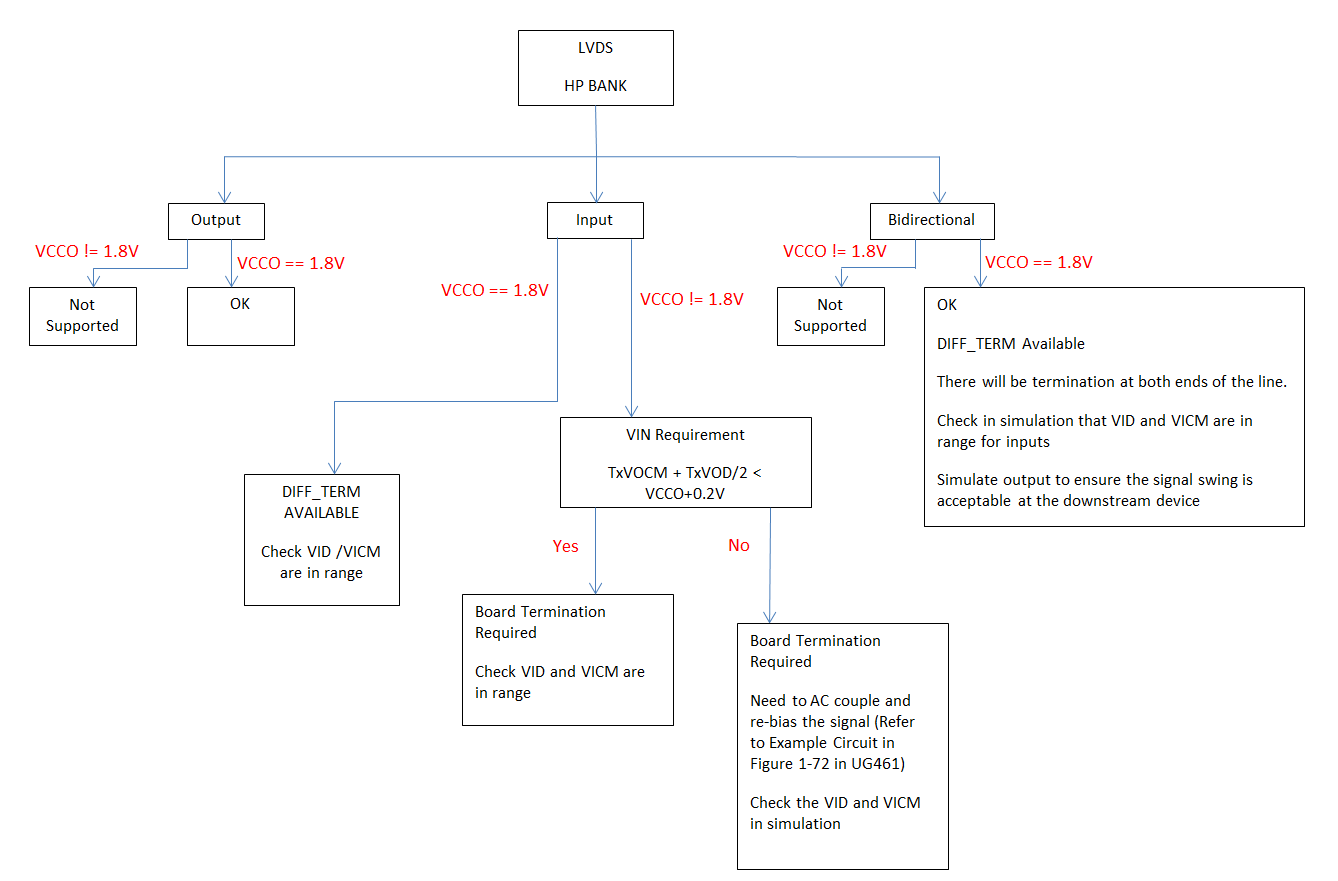

在进行7系列差分接口设计时,我们可以参考图1和图2检查表,遵循图中要求,以保证电气正常连接。

图1、HP Bank-LVDS电平兼容设计检查表

图2、HR Bank-LVDS_25电平兼容设计检查表

在图1检查表中,我们可以看到:

HP LVDS IO 作为输出管脚时,VCCO电压只能为1.8V,IO内部端接电阻可用;

HP LVDS IO 作为输入时,VCCO电压可以不为1.8V,此时,LVDS电平可以输入到HP I/O Bank。这种情况,注意:

1)DIFF_TERM属性必须为FALSE,IO内部端接电阻不可用,只能使用外部端接;

2)确保驱动器件VOD和VOCM电平在7系列接收器VIDIFF和VICM要求的范围内。

举例,假如HP VCCO=1.5V,此时可以接收LVDS输入,但是信号输入摆幅不能超过VCCO+0.25V。

对于图2检查表,类似上述描述。

3.说明

1.关于3.3V LVDS

在某些老版本FPGA家族中,LVDS_33 I/O标准是可用的,但在7系列器件中不支持;如果使用LVDS输出,无论是在HR Bank还是HP Bank,VCCO都不能采用3.3V供电。

7系列I/O Bank支持旧家族FPGA LVDS_33输出,但是必须确保满足:

1) 数据手册中表1和表2中VIN要求不能违反;

2) LVDS(HP Bank)或者LVDS_25(HR Bank)中的VIDIFF和VICM要求不能违反 。