作者:周肇基/施天从/谢昆霖;新通讯 2018 年 8 月号 210 期《 技术前瞻 》

随着网络技术与物联网应用的发展,数据传输流量的需求也不断的增长。在数据传输技术中,下一个重大转变将是400Gb以太网络(400GbE)技术的推展与普及,400Gb以太网络技术预计将很快的会在各种云端服务、电信公司、以及需要超高带宽连接的应用环境中进行试用。数据传输技术朝向400Gbps速率发展的方向应该是主流的趋势,但是400Gbps传输接口模块要采用何种型式的插拔外型,目前产业界仍有不少的讨论,成本的考虑会是技术转型的思考重点。因此,400Gbps传输接口模块技术预计需要考虑向下的兼容性与向上的发展性,以降低发展过程的成本需求。

四路小型可插拔(Quad Small Form-factor Pluggable, QSFP)收发器是目前广泛使用在光纤数据传输的一种紧凑型热插入收发器,在收发器接口具有四个发射与四个接收信道,可将网络通讯设备(如:服务器和交换机)连接到光纤缆线。QSFP的外型和电气接口由多源协议(Multi-Source Agreement, MSA)规定,是由许多网络组件供货商联合开发和支持的产业格式,随着网络传输流量增加的需求,QSFP模块操作速率也不断的发展与演进,QSFP的操作速率为4×1Gbps;QSFP+的操作速率为4×10Gbps;QSFP28的操作速率为4×28Gbps,可使用于100Gbps网络的链结。

由于超大规模数据中心不断增长的带宽需求,使得光通讯的收发器模块急需能提高传输速率至200Gbps或400Gbps的解决方案,以降低带宽成本。因此,MSA已提出QSFP-DD(Double Density)的模块标准,在标准的QSFP四通道接口,多增加一排四通道接口,成为具有八通道的光收发器,若采用非归零(Non-return Zero, NRZ)数据格式,传输速率可达200Gbps;若采用四接脉波振幅调变(Four-level Pulse Amplitude Modulation, PAM-4)数据格式,每个信道传输速率可达50Gbps(或25Gbuad),可实现400Gbps的传输。QSFP-DD模块的结构可以支持QSFP+和QSFP28标准,让使用QSFP-DD模块所设计的系统可以向下兼容,能与目前已在使用的40GbE和100GbE收发器共同操作,提供用户和系统设计更灵活的系统规画。思科也在OFC 2017中展示QSFP-DD模块,预期QSFP-DD将成为下一代400GbE可插拔光模块的主要标准之一。

着重模块整体结构设计 高速光收发器模块开发有诀窍

对于高速光收发器模块的开发,除了关键的高速光电组件、相关的驱动IC外,模块整体结构的设计与制作也是重要的一环,光收发器模块开发制作的流程依序为整体电路设计、印刷电路板迭构设计、印刷电路布局设计、印刷电路制作、电路组件焊接与电源测试、光电组件焊接与耦光测试、整体光收发器模块测试等步骤。

・整体电路设计:

根据光收发模块的相关规范,选择适当的组件、光源驱动IC、光接收IC、微控制器(MCU)、电源IC等建立物料列表,并依照模块的输入、输出端口及功能设计整体电路图。

・印刷电路板迭构设计:

主要针对高频讯号层,选择适合的电路板材料,再根据相关规范设计电路板堆栈层数与结构,并计算高频讯号走线宽度,以符合传输路径之阻抗匹配。

・印刷电路布局设计:

根据电路板迭构与整体电路图,设计高频讯号走线、低速控制讯号与电源走线、接地面等电路板各层布局。

・印刷电路制作:

与电路板工厂制程工程师讨论确认电路板设计与制程工法可以实现,则可依照电路板布局及迭构设计制作模块的电路板。

・电路组件焊接与电源测试:

将电路板先焊接上电阻、电容等被动组件,以及电源相关IC,先进行电路板电源供应测试。

・光电组件焊接与耦光测试:

在电路板上焊接雷射二极管芯片、光二极管芯片、光源驱动IC、光接收IC、微控制器(MCU)等组件,将韧体写入MCU控制相关IC,进一步调控光发射器与光接收器操作条件,接上透镜与测试光纤,并微调透镜位置以获得最佳耦光效果。

・整体光收发器模块测试:

将完成的光收发模块,透过其评估板,设定在多种操作条件下,进行发射与接收讯号眼图质量、传输数据误码率等测试,确认讯号传输质量符合相关标准与规范。

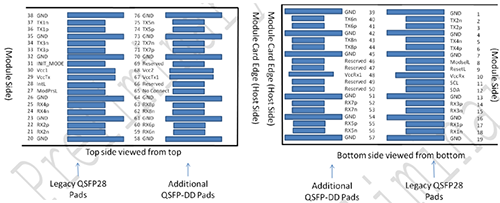

对于QSFP-DD光收发模块的开发,若采用NRZ数据格式操作,单一通道的传输速率为25Gbps,与适用于100GbE的QSPF-28模块速率相同,但是QSFP-DD的光发射与接收通道数由四增加至八信道,而电路板面积仍然相同,所以QSFP-DD的信道密度加倍。因此,QSFP-DD模块输入输出端口的金手指规范与其他QSFP模块不同,共有76个端口,而且排列成两排,如图1,除了八对高速讯号输入端口将数据送入光发射器,八对高速讯号输出端口将光接收器数据送出,以及各对高速讯号输入输出端口两侧的接地之外,还有五个电源供应端口,及八个功能控制使用的端口。

图1 QSFP-DD模块输入输出端口金手指结构

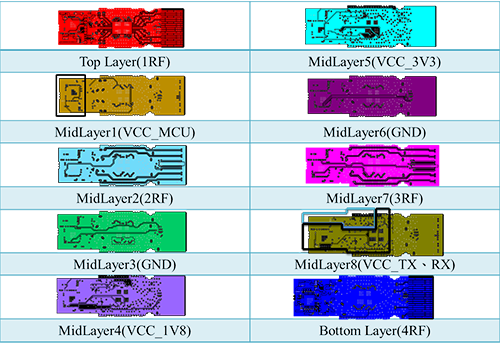

目前适用100GbE的QSPF-28模块,其电路板通常采用六层的迭构,最上与最下层为高速讯号走线层,依序往内有两层接地层,及两层低速控制讯号与电源供应层。但是QSFP-DD模块的信道数倍增,以原有QSFP模块的电路板面积,两层高速讯号走线层将无法实现八通道光发射与八信道光接收的模块,因此QSFP-DD模块的电路板设计需要使用到十层电路板设计,让高速讯号走线层增加为四层。因为QSFP-DD电路板的迭构增加为十层板,但是电路板总厚度仍需与QSFP模块相同,所以高速讯号走线层与接地层之间的厚度将会减小,如此将会使高速讯号走线的电容变大,降低传输带宽。

因此,QSFP-DD高速讯号层的电路板材料必须采用更低介电系数的材料,来降低传输线电容,以符合所需的传输带宽。高速讯号层电路板材料的选择也是QSFP-DD模块电路板设计的关键之一,电路板高频讯号线传输带宽的设计必须与板材的介电系数、损耗系数、最小可制作厚度等条件之间进行设计取舍。

此外,由于使用四层高速讯号层,除了电路板最上与最下层外,高速讯号将会在电路板内层传输,势必会出现高速讯号由外层进入内层或由内层送出外层的传输,此处的讯号完整度常因为走线的不连续或钻孔连接而被破坏,无法达成良好的阻抗匹配,因此内、外层之间讯号的传输必须特别注意讯号完整度的仿真分析与设计。QSFP-DD模块十层电路板的设计范例,如图2。

图2 QSFP-DD模块十层电路板设计范例

高速数据传输技术朝400Gbps发展的方向应是无庸置疑,而QSFP-DD光收发模块开发的目的就是要满足400Gb以太网络的市场需求与系统优化而产生,QSFP的模块的外型尺寸已经被设计使用超过十年,因此具有良好向下兼融的QSFP-DD模块在400Gbps发展初期,是一种低成本的解决方案。而未来高速数据传输光模块的发展,还需要考虑操作速率是否具有向上的发展性、系统对模块的散热机制、以及光学组件与模块间的配合度等问题。400Gb以太网络整体的建构目前仍属于实验室建构与测试阶段,公共部署与示范即将展开,在市场爆发前期,建立新一代高速数据传输光模块技术是刻不容缓的工作。

(作者皆任教于高雄科技大学电子工程系)

文章来源:新通讯