本文是该系列的第8篇。第2篇中以数字滤波器的设计为主题,介绍了System Generator的完整设计流程;第7篇介绍了其中数据类型的选择与位宽截断的问题。本文将对其中使用到的Reinterpret和Convert模块进行详细介绍。

模块功能概述

数据转换,数据类型、位宽等问题都会影响到计算精度,对于设计者而言,需要考虑的就是相关影响是否可以接受,即是否会影响到实际的系统性能。FPGA设计中还经常需要截位,否则位宽在整个系统中不断积累,大大增加资源的消耗。

数据类型的转换和截位是FPGA系统设计的重要内容,博主在《FPGA数字信号处理》系列的很多设计中都有详细讨论。而在System Generator设计中,完成这项任务的便是Reinterpret和Convert模块。

数据类型转换模块在导出到FPGA设计中(定点与浮点之间的转换、浮点与浮点之间的转换),会使用Floating-Point IP核实现,具体可参考《FPGA数字信号处理》,本系列不详细介绍。

Reinterpret block

1.block特性

这个block可以完成以下数据转换功能:

将无符号数转换为带符号数;

将带符号数转换为无符号数;

通过重新规定小数点位置来定义数据范围。

需要注意的是,“转换”在这个block中的含义更接近于其英文直译“重新解释”。事实上,数据在经过该block后,其位宽与每一位的值都没有发生任何改变,变化的只有其所表示的“意义”。正如博主在《FPGA数字信号处理》系列中强调的一样,一个二进制数是无符号数还是带符号数、小数点在哪一位仅仅取决于设计者如何规定和看待它。而Reinterpret改变的便是这种“规定和看待”方式。

比如,“1100”这个数,当视作UFix_4_0(无符号定点数、4Bits位宽、小数部分0bit)时,其值为12;当视作Fix_4_2(带符号定点数、4Bits位宽、小数部分2Bits)时,其值为-1。因为reinterpret实现的只是一种意义上的转换,因此其在转换为FPGA设计后,不会消耗任何资源。

既然reinterpret的输出和输入完全相同,那么加入此模块有什么作用?

从FPGA设计转换到Simulink环境中时会按设定的“意义”解析数据格式;

完成不同格式数据之间的的拼接。

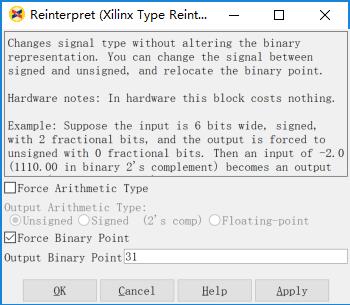

2.参数设置

(1).选中“Force Arithmetic Type”后,输出数据格式的“意义”将转换为(没有选中,则输出与输入的表征意义相同):无符号数(Unsigned)、带符号数二进制补码(Signed(2’s comp))、浮点数(Floating-point)。

(2).选中“Force Binary Point”后,可以重新规定输出数据的小数点位置。比如设置为31时,表明数据中的低31Bits为小数部分。

Convert block

1.block特性

该block不仅可以完成数据类型的转换,还具有如下特性:

重新设置数据的量化、溢出方式;

重新设置定点数格式(进行数据截位)。

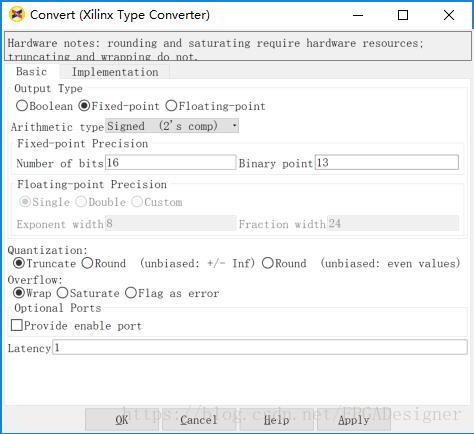

2.参数设置

其中大部分参数设置方法与Gateway In模块的设置完全相同,具体可参考本系列第5篇。这里只讲述两者不同的地方。

(1).Convert模块的量化方式可以配置为“Round(unbiased: even values)”,这是针对“四舍五入”量化方式的缺点所作的改进:

传统的四舍五入所有的中间值(如1.5、2.5)都会向更大的值量化,即不是完全对称的,这样会导致一组数据量化后平均值高于量化前的平均值。

unbiased: even values在处理中间值时会向更接近的偶数量化。比如1.5会量化为2;2.5仍然会量化为2(因为二者最接近的偶数都是2)。这样量化规则在整体上会呈现出对称性。

(2).选中“Provide enable port”后,block会增加一个en使能管脚,只有当使能有效时convert block才会执行数据转换功能,否则将保持当前状态不变。

(2).Latency设置了Convert输出数据要经过多少个采样时钟周期的延时。注意不要混淆“采样时钟周期”和“FPGA时钟周期”的概念,在过采样系统中,一个采样时钟周期可能等于多个FPGA时钟周期。

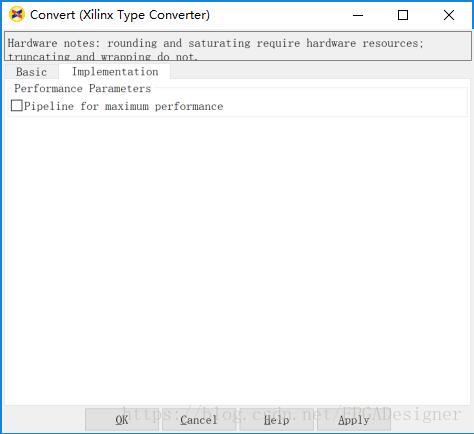

前文提到Convert在导出到FPGA中时会以Floating-Point IP核的方式实现,“Implementation”标签下可以设置Latency在FPGA中的实现方式:

●选中“Pipeline for maximum performance”时,Latency以流水线的方式实现,即在计算过程中增加中间级寄存器,以更多的资源实现更快的计算速度和更大的数据吞吐量。

●未选中“Pipeline for maximum performance”时,Latency以在IP核末尾增加一级移位寄存器的方式实现,这样只是单纯的实现了延时功能。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人