一. 概述

这里以7系列的FPGA为例,先从整体上去了解一下FPGA内部可编程逻辑资源的结构。了解FPGA器件的内部资源与结构有利于我们优化设计与评估设计资源。

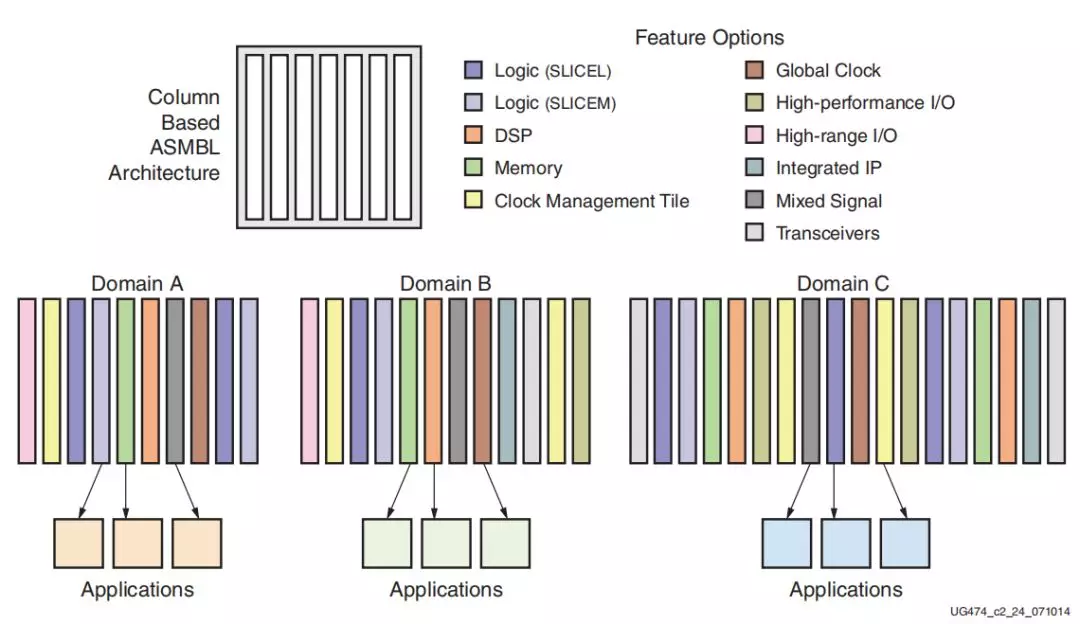

现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。下图是一个抽象的结构图,相同资源以列方式排布。这篇文章主要讲解CLB资源。

二. CLB资源介绍

CLB资源的分布以纵向相连,如下图所示。每个CLB由两个Slice组成。同一个CLB里面的两个Slice之间没有互连线。

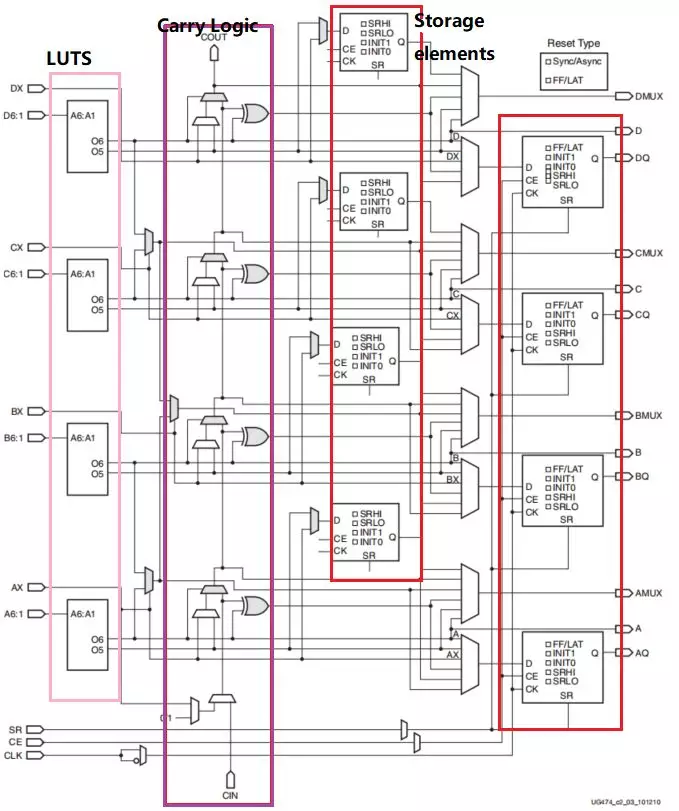

每个Slice里面有4个6输入的LUT(look-up tables(查找表))和8个存储单元(Storage)以及进位逻辑(Carry Logic)和多路选择器(Multiplexers)。同时Slice有两种。

普通的Slice叫SLICEL,电路结构如下,最左边一列就是4个LUT,第二列为Carry Logic,以及红色框框出来的存器单元。

第二种Slice叫SLICEM,电路结构如下。除了LUTS与SLICEL的LUTS不同之外,其余结构都一样。这就是SLICEM与SLICEL之间的区别,利用SLICEM的LUTS还可以构成RAM,ROM,以及Shift Registers(移位寄存器)。

一个CLB里面含有一个SLICEM和SLICEL或者含有两个SLICEL。

Slice就是通过LUTS以及Carry Logic和Multiplexers之间的互连来形成组合逻辑,再通过Storage elements构成寄存器以形成时序逻辑。

同时借助SLICEM的LUTS,还可以构成RAM,ROM,Shift Registers资源。

下表是一个CLB可以拥有的资源数以及可以形成大小为多少的RAM与Shift Registers。我们可以借助这些信息去评估设计需要多少资源和选择什么型号的FPGA器件。

后文预告

接下来我们会继续深入介绍CLB如何构成组合逻辑,时序逻辑电路,RAM,Shift Registers。

文章转载自:Xilinx学术合作