作者:浅搁 FPGA2嵌入式

1. 前言

IP核这个东西相信很多人都不陌生吧,不管是哪个FPGA厂家,都会有自己的一些现成IP核供用户使用,从而节省设计的开发时间。在一个设计中,个人觉得将模块变成一个个直观的图形界面更有助于理清思路,增强整个设计的逻辑性。以前用过Microsemi的开发平台,觉得挺人性化的,你写完代码后,直接把.v文件拉到画布中,文件便会以图形模块的形式显示出来,然后拖动鼠标便可以把两个模块的对应引脚连接起来,十分方便直观。

2. Vivado中的IP核封装

在Vivado平台中,我一直想寻找看看有没有这种形式,最终发现并没有~~。不过Vivado也提供了类似的方式,你首先要把.v文件封装成IP,然后才能放到画布中调用,虽然过程有点繁琐,不过有总比没有好呀~~

IP核的封装其实也不会很难,前提是你得把.v文件先准备好,如果连代码都没有还扯啥犊子哟。

在打开Vivado工程后,单击“Tools ---- Creat and Package IP”。嗯,就是这厮了,然后一路Next。

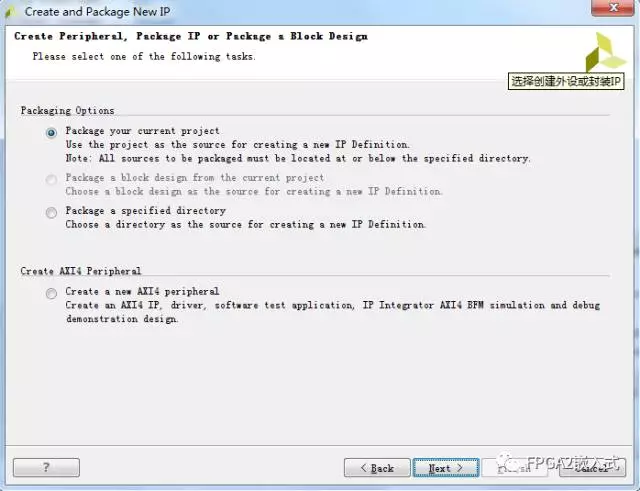

接着出现如下界面,按着选项选择自己的需求即可,点击“Next”,正式进入主题。

一般的话选择第一项即可,如果你的IP核需要走AXI总线,则选择第三项就行了。

普通IP封装

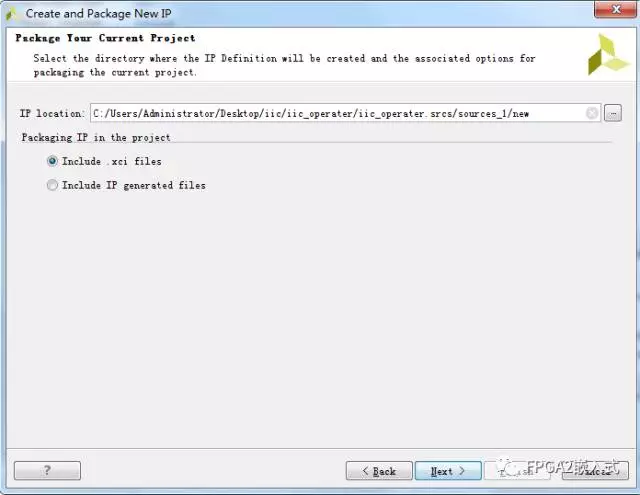

进入普通IP封装界面,如下图所示,如果你要封装的IP里包含有IP核,就要选择第二项,没有的话默认第一项就行了。然后“Next”,"Finish"就这么简单的完成了第一阶段啦。

接下来你会看到一个新的工程出现,没错,这就是IP核的封装工程了!

我们只要关注右边的选项就行了。第一项是基本信息,用户可以给IP命名,进行描述等。

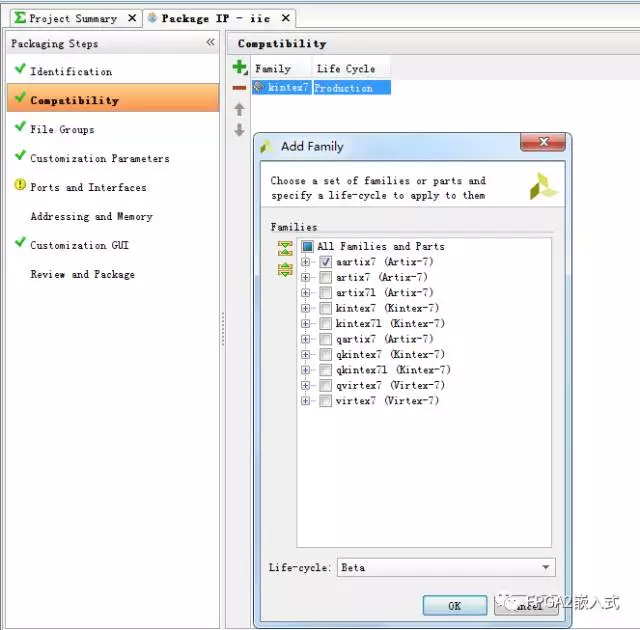

第二项是器件添加,只有选择了相应的器件,你的IP核才能在那个器件里被使用。单击器件,右键——Add——Add Family Explicitiy,于是便可以选择要适用的器件系列了。

其他选项也没啥好改的,直接默认就行了,最后可以看一下IP核的GUI界面,提前欣赏它的风采。

最后一项,点击最下面的“Package IP”,这样一个IP的封装就完成了,就是这么任性这么简单。

AXI总线IP封装

有时候将代码封装成AXI总线的IP核是非常有用的,当你使用软核跟你的模块进行通信时,封装成AXI总线的IP核,是必须要的。

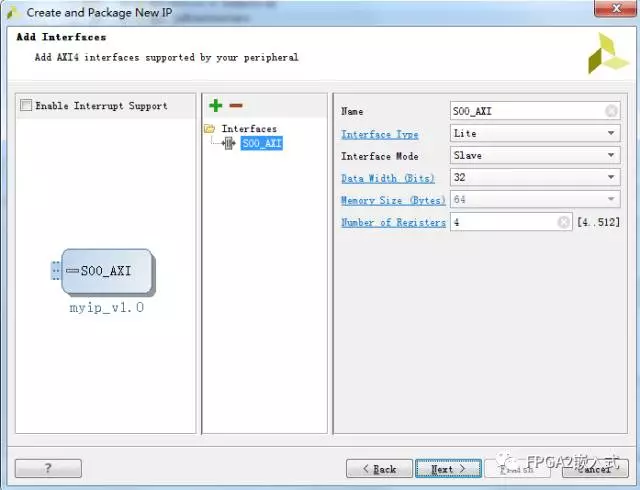

选择封装成AXI总线后,会出现下面的界面,让你选择要封装成哪一种AXI总线,以及有多少个寄存器等等设置。

选择好你想要的设置后,点击“Next”后会出现IP封装界面,注意,此时要选择第二项“Edit IP”,然后“Finish”。

之后照样会生成出一个新的工程,和普通IP封装不同的是,这里会多出一个.v文件,这是AXI总线协议的文件,它已经帮你把顶层做好,你需要把自己的工程加入进去即可。

文件代码基本就是AXI的时序协议,然后你只需要把你数据端口跟它的数据端口相连接就行了。

如上图所示,蓝色框是它的数据端口,AXI总线会把数据写入对应的寄存器中,也可以把这些寄存器的数据读走。红色框就是给用户添加代码的,你可以把自己的模块放进来,然后数据端口跟蓝色框的数据端口相连接即可,这样通信就建立了。

最后保存,综合一下,和前面普通IP封装一样的处理方式,把IP核生成即可。

3. IP核的调用

IP核封装完就可以调用出来使用了,东西做出来不就是为了可以装逼嘛哈哈~~

找到刚才生成IP核的路径下那个文件夹,里面大概就是下图这几项东西了,一项都不要去乱删啊,很有用的这些。

接着把这个文件夹放到你的工程文件夹里(也可以不用,看个人爱好)。接着打开“IP Catalog”,在空白处右键,选择“Add Repository”,然后选择刚才说的IP文件夹,确定后,IP就被添加进去了。如下图所示,iic的IP已经出现在“IP Catalog”里,下次可以直接在这里把这个IP和调出来用,想在哪用就在哪用!

4. 总结

很多时候在项目的后期一些成熟的模块封装成IP帮助会很大,起码在界面上你能看到一个个的模块连在一起思路会非常清晰。同时封装成IP的模块也可以给其他人或者其他项目使用,减少开发周期。所以总的来说,将模块封装成IP还是很有用处滴。

文章来源:FPGA2嵌入式