一. 概述

Verilog HDL不同于我们学过的C,Python等软件设计语言;Verilog是一门硬件描述语言。这里有两个关键词:硬件,描述。

硬件:表示我们时刻要从数字电路系统的角度去认识和学习Verilog HDL

描述:而不是设计。因此表示在用动手进行Verilog编写之前,电路的架构至少已经在你脑子里构建好了,而Verilog只是把它描述出来而已。

从上面两点可以看出,Verilog的学习与编写,不能想软件那样自由,要以数字电路系统为根本。

反过来讲,学习Verilog,可以从下面三个问题入手:

1.设计对象有哪些需要描述?

2.如何描述它们?

3.如何优化设计?

二. Verilog之于数字电路设计

1. 设计对象有哪些需要描述?

答:数字电路系统里面基本的元素如下:

(1)组合逻辑

(2)寄存器

(3)信号线网络

(4)输入输出信号端口

(5)RAM

(6)一些基本的功能电路

当然组合逻辑配合寄存器就可以组合成时序逻辑。

2. 如何描述它们?

逻辑的描述:

(1).可以通过真值表做卡诺图化简,再用门级逻辑去描述,但是设计复杂,编码效率低,同时也体现不出Verilog的优势。

(2).采用Verilog行为级描述方式,描述效率高。当然就要了解相应的可以综合的Verilog描述方式。

3.如何优化设计?

(1):Verilog是对数字电路进行描述,故首先我们需要考虑数字电路有哪些优化方式。例如数字电路需要考虑的问题有速度(时序),面积(所有资源的多少),那么对应的我们需要了解数字电路的优化速度的方式,比如流水线设计以及数字逻辑简化,跨时钟同步的方法等等。

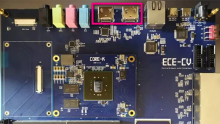

(2):Verilog只是一个描述语言,你还的使用具体的EDA工具去对电路进行综合。然后EDA工具对电路的综合又是结合具体的基本单元库来实现的。比如Vivado对Verilog进行综合实现,最后是将我们描述的Verilog数字电路功能映射成了相应的FPGA基本器件来实现的,比如(CLB->SLICE->LUT)。因此我们在进行Verilog描述时,为了使得我们的设计更具有效率,我们需要对FPGA的资源有一定的了解。

三. 后文预告

后面将会以实例带大家认识具体的Verilog描述语法:Verilog基本描述语法,组合逻辑的行为级描述方式实例,寄存器的描述。

四. 参考资料

Vivado Design Suite User Guide - Synthesis - UG901 (v2018.2) June 6, 2018

7 Series FPGAs Configurable Logic Block-User Guide - UG474 (v1.8) September 27, 2016

文章转载自:Xilinx学术合作