作者:肉娃娃

原语,即primitive。不同的厂商,原语不同;同一家的FPGA,不同型号的芯片,可以也不一样;原语类似最底层的描述方法。使用原语的好处,可以直接例化使用,不用定制IP;即可通过复制原语的语句,然后例化IP,就可使用;Xilinx是通过直接修改原语中的参数再例化IP来使用;Xilinx公司的原语分为10类,包括:计算组件,IO端口组件,寄存器/锁存器,时钟组件,处理器组件,移位寄存器,配置和检测组件,RAM/ROM组件,Slice/CLB组件,G-tranceiver。下图所示为UG799中对原语的分类列表。

项目中主要用到的原语与IO端口有关,所以基本在Input/Output Functions 和IO两类中。下面着重介绍实际中所用到的几个原语,芯片A7系列。

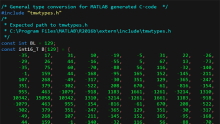

1. IBUF和IBUFDS(IO)

IBUF是输入缓存,一般vivado会自动给输入信号加上,IBUFDS是IBUF的差分形式,支持低压差分信号(如LVCMOS、LVDS等)。在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。一个可以认为是主信号,另一个可以认为是从信号。主信号和从信号是同一个逻辑信号,但是相位相反。

举例说明:

LVDS_25的差分输入的ADC数据。

IBUFDS #( // 差分输入原语,用于LVDS_25端口

.DIFF_TERM("TRUE"),

.IOSTANDARD("LVDS_25")

) IBUFDS_ADC01 (

.O(ADC01_D[i]),

.I(ADC01_P_D[i]),

.IB(ADC01_N_D[i])

);

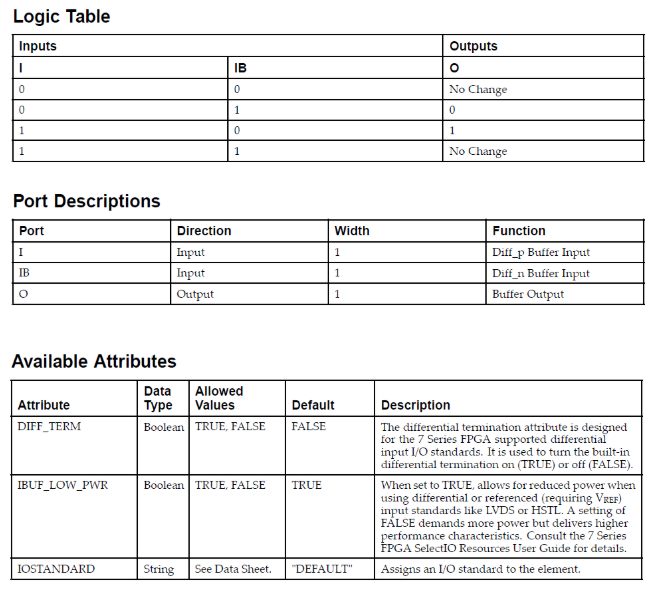

2. IDDR(Input/Output Functions)

被设计用来接收DDR数据,避免额外的时序复杂性。

举例说明:

差分数据源经过差分转单端后,生产ADC01_D,在同步时钟ADC01_DCO的驱动下,产生DDR数据adc01_a_d和adc01_b_d。

IDDR #(

.DDR_CLK_EDGE("SAME_EDGE_PIPELINED"),

.INIT_Q1(1'b0),

.INIT_Q2(1'b0),

.SRTYPE("SYNC")

) IDDR_ADC01_D (

.Q1(adc01_a_d),

.Q2(adc01_b_d),

.C(ADC01_DCO),

.CE(1'b1),

.D(ADC01_D),

.R(1'b0),

.S(1'b0)

);

3. IBUFG和IBUFGDS(IO)

IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。 IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

举例说明:

差分时钟芯片输入的100MHz时钟,作为FPGA的全局时钟。

IBUFGDS #(

.DIFF_TERM ("TRUE" ),

.IBUF_LOW_PWR ("FALSE")

) u_ibufg_clk_100 (

.I (FP_CLK_100M_P),

.IB (FP_CLK_100M_N),

.O (clk_100m )

);

参考文献:

http://blog.sina.com.cn/s/blog_47205d2d0100l5jv.html

《Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for Schematic Designs》(UG799)