本篇主要介绍逻辑互连中的AC耦合电容。

1、AC耦合电容的作用

2、AC耦合电容的位置及大小

一般AC耦合电容的位置和容值大小都是由信号的协议或者芯片供应商去提供,对于不同信号和不同芯片,其位置和容值大小都是不一样的。比如PCIE信号要求AC耦合电容靠近通道的发送端,SATA信号要求AC耦合电容靠近连接器处,对于10GBASE-KR信号要求AC耦合电容靠近信号通道的接收端。

一般放在接收端,其原因如下:

在设计过程中,最好的处理方式如下:

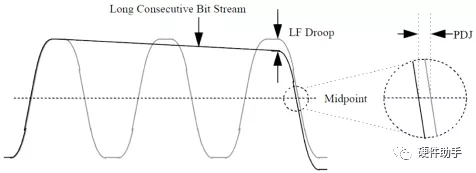

在串行信号中串入AC耦合电容,这个电容可以提供直流偏压和过电流保护,但也会给链路带来另一个问题PDJ(pattern-dependent jitter)。这和码型有关,链路可以等效成高通RC电路,当出现连续的“1”或“0”时,会出现下图的直流压降,这不仅会影响眼高,还会造成PDJ。

怎样才能减小这个直流压降呢?这和RC时间常数有关,RC值越大,能通过的直流分量就越多,直流压降越小。由于链路中等效R是相对固定的,只能调节耦合电容值了。一般情况耦合电容值越大,压降越小。

因为,实际安装后的电容不是理想电容,除了ESR、ESL,还有安装电感,所以就存在一个串联谐振频率。电容在此频率之前呈容性,之后呈感性。电容值越大,谐振频率越小,电容在较低频率就会呈现感性,这样会造成信号高频分量衰减增大,同样会使眼高减小,上升沿变缓,jitter增加。

所以选值时要综合以上两点考量,一般业界都推荐0.01uF~0.2uF,最常见的就是0.1uF的电容。封装的选择不建议使用大于0603的封装,最好是0402的。

交流耦合电容的计算公式为:

C=7.8*NCID*Tb/R

其中:

Tb = the bit period(时钟周期)

NCID = the maximum tolerated consecutive identical digits(连续同一电平的长度)

R = the total resistance asseen from the capacitor(RC电路中的R)

例如在光通信系统中,典型的贷款为0.6~1倍数据速率。比如2.488Gbps的接收器Tb=402ps。如果NCID=72bits,R=100,计算出来的C=2.25nF。如果Tr=120ps,并且C=2.25nF,那么计算粗来的PDJ=12ps。如果将C增大到100nF,则PDJ会减小到<1ps。

一般而言,电容容量越大,ESL也会比较大,所以选择电容时需要综合考虑。详细的选择可以参考MAXIM Application Note HFAN-1.1:Choosing AC-Coupling Capacitors。

3、AC耦合电容的应用

SATA信号传输的过程中会有衰减,传的距离越长衰减会越厉害,所以会给他一个载波(也就是直流分量),在进入IC或SATA device后再用串电容的方法把直流分量滤掉,这样做会有比较好的信号质量。也就是隔直作用。

PCIe板卡放在发送端是协议规定的(可参看后续PCIe相关文章,会详细讲解针对PCIe总线的耦合电容的位置、大小、数量等等)。

USB3.0上TX、RX要加,D+、D-不加,因为要兼容2.0/1.1/1.0,跟2.0和1.1的检测有关。

4、AC耦合电容的PCB设计

每个电容本身,电容的扇出引线和电容换层过孔都是一个阻抗不连续点。高速串行信号对于阻抗一致性提出非常高的要求,如果阻抗匹配不好将会带来反射,最后影响整个通道的IL、RL、Jitter以及BER等,最终影响整个通道性能。

4.1、布局

差分信号在设计时候需要尽量做到对称,任何不对称的因素都会使得部分差分信号转换为共模信号。对于共模信号而言,信号和参考面的耦合和回流路径一旦处理不好,都会成为EMI的潜在威胁。

不对称的电容摆放会带来更多的共模信号,将对EMI带来潜在的威胁,而不对称摆放对插损回损影响不大。

4.2、布线

对于0.1uF的0402封装(焊盘尺寸为20mil*20mil)的耦合电容,以一个六层板为例(叠层顺序为TOP-GND1-SIG1-SIG2-GND2-BOT),电容布局在TOP层,如以GND1层为参考,则焊盘处的阻抗为92Ω左右(实际差分阻抗要求是100Ω)。由于电容pad处的宽度为20mil,大于走线宽度,而阻抗和线宽成反比,因此pad处阻抗会变小。为了增大pad处的阻抗,可以使pad和参考面的距离增大。可以把pad正下方的GND1层掏空,电容pad就参考了SIG1层的电源/地平面(在对应位置铺铜,并通过sitching vias连接),这样阻抗就会变大。

为了得到更精确的设计参数,可以利用3D电磁场仿真软件进行仿真,不同挖空形状对阻抗的影响还是比较大的,一般粗略的设计,挖空的形状为和电容长度相等,和两个电容并排的宽度稍微宽一点的矩形即可。这样的设计会让通道的阻抗一致性最好。阻抗通道的一致性越好,其反射会越小,从而带来了插损和回损曲线的改善,最终会使整个系统工作更稳定。

以上就是针对交流耦合电容的粗略理解,后续会以PCIe总线为例,针对PCIe总线的AC耦合电容进行进一步的介绍。

文章转载自:硬件助手