本篇主要介绍MIPI物理层规范中的D-PHY,主要包括D-PHY的架构、操作模式、电气特性等。

MIPI D-PHY将百万像素摄像头和高分辨率显示器连接到应用处理器。它是一个时钟驱动的同步链路,可提供高噪声容限和高抖动容限。MIPI D-PHY还提供高速和低功耗模式之间的低延迟转换。

由于其灵活,高速,低功耗和低成本的特性,MIPI D-PHY是智能手机中用于相机和显示器的主流PHY。它也可以应用于许多其他地方,例如汽车摄像头传感系统,防撞雷达,车载信息娱乐系统和仪表盘显示器。

由于链路收发器的主从关系,链路的操作和可用数据速率是不对称的。非对称设计显著降低了链路的复杂性,并且非常适合于具有一个主要数据传输方向的显示器用例。支持双向和半双工操作。

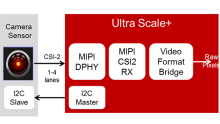

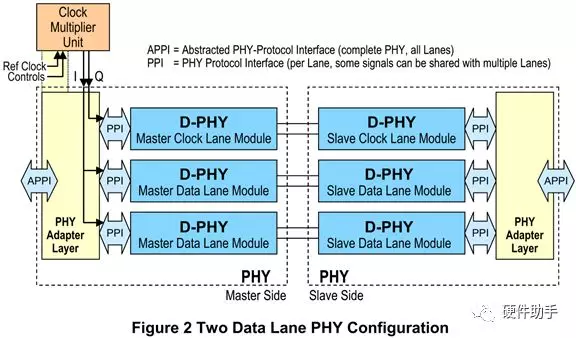

1、D-PHY架构

D-PHY的最初版本的设计目标是500Mbits/s,而D是罗马数字(拉丁文数字)中500。D-PHY采用1对源同步的差分时钟和1~4对差分数据线来进行数据传输。数据传输采用DDR方式,即在时钟的上下边沿都有数据传输。

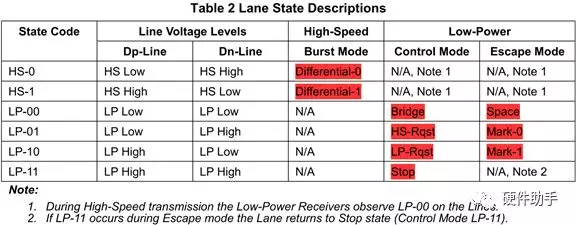

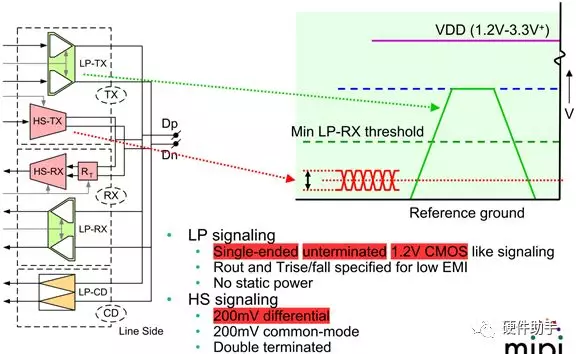

D-PHY的物理层支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号,功耗较大,但是可以传输很高的数据速率(数据速率为80M~2.5Gbps),采用源同步的传输方式,由主机(Master)设备向从机(Slave)设备提供DDR时钟;LP模式下采用单端信号(1.2V LVCMOS信号),数据速率很低(≤10Mbps),但是相应的功耗也很低,用于传输初始化控制信号。两种模式的结合保证了MIPI总线在需要传输大量数据(如图像)时可以高速传输,而在不需要大数据量传输时又能够减少功耗。无论是HS模式还是LP模式,都采用LSB first,MSB last的传输方式。

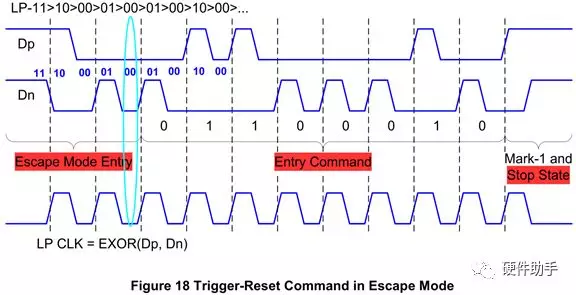

在LP模式下,只用lane0实现双向数据传输,时钟是使用数据Dp和Dn的EXOR恢复的。

链路层的模式分为:Command模式和Video模式。链路层选择Command模式时,物理层可以为HS模式,也可以为LP模式;链路层选择Video模式时,物理层只能选择HS模式。

一个通用的Lane中包含LP-TX、LP-RX、HS-TX、HS-RX和LP-CD模块,所有收发模块均共用同一对差分线Dp,Dn(在LP模式下,为两根单独的信号线)。整个Lane通过PPI接口(PHY Protocol Interface)与系统的其他部分连接。

其中,LP-CD模块仅在存在于需要双向通信(Bidirectional)的系统中,对于不需要双向通信(Unidirectional)的系统,如CSI协议,则不需要LP-CD模块。显然,在Unidirectional系统中,主机(一般固定为Transmitter)则不需要RX模块,从机(一般固定为Receiver)则不需要TX模块。在需要双向通信的系统中,如DSI(当然,在特定的系统中,DSI也可以是Unidirectional的),一般只需要一个Data Lane具有双向收发的能力,其他的Data Lane和Clock Lane则可以根据实际需求,去除RX或者TX模块。需要注意的是,即使在Unidirectional的系统中,Clock Lane也不需要反向传输,即当从机向主机发送数据时(反向传输),此时的DDR时钟仍然是由主机提供(HS模式下,LP模式下则不需要时钟)。

在LP模式下(包括Control Mode和Escape Mode),采用的是Spaced-One-Hot Coding机制。在该机制下,时钟可以从传输的数据中得以体现(时钟恢复),因此不需要传输时钟。此时,用户可以根据实际需求,设置Clock Lane继续运行或者关闭以降低功耗。常见的LPDT模式(Low-PowerData Transmission)和ULPS模式(Ultra-Low Power State)都是Escape Mode的一种。

D-PHY中一共有三种Lane,Unidirectional Clock Lane、Unidirectional Data Lane以及Bi-directional Data Lane。

需要注意的是,D-PHY的Bidirectional通信是一种半双工的双向通信模式,同时,反向传输的速度只有正向传输的1/4。

2、操作模式及转换

一个典型的HS传输过程的序列为:LP-11→LP-01→LP-00→HS→LP-11;

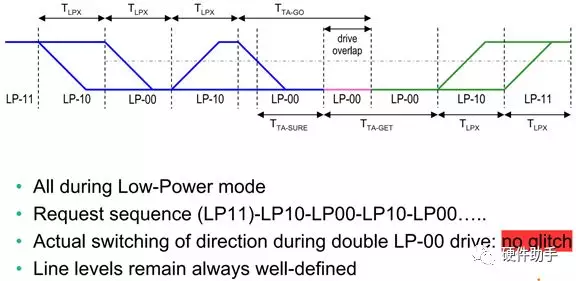

转向(TurnAround)的序列为:LP-11→LP-10→LP-00→LP-10→LP-00;

Escape Mode传输过程的序列为:LP-11→LP-10→LP-00→LP-01→LP-00;

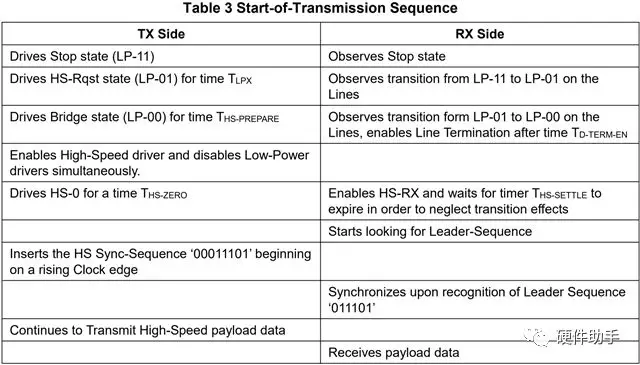

2.1、High-Speed Data Transmission

Start-of-Transmission的流程如下表所示:

End-of-Transmission的流程如下表所示:

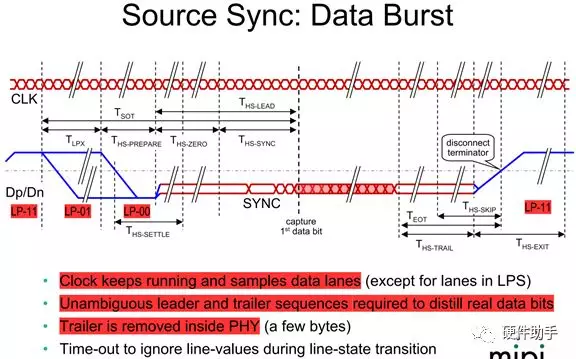

HS Data Transmission Burst的流程如下所示:

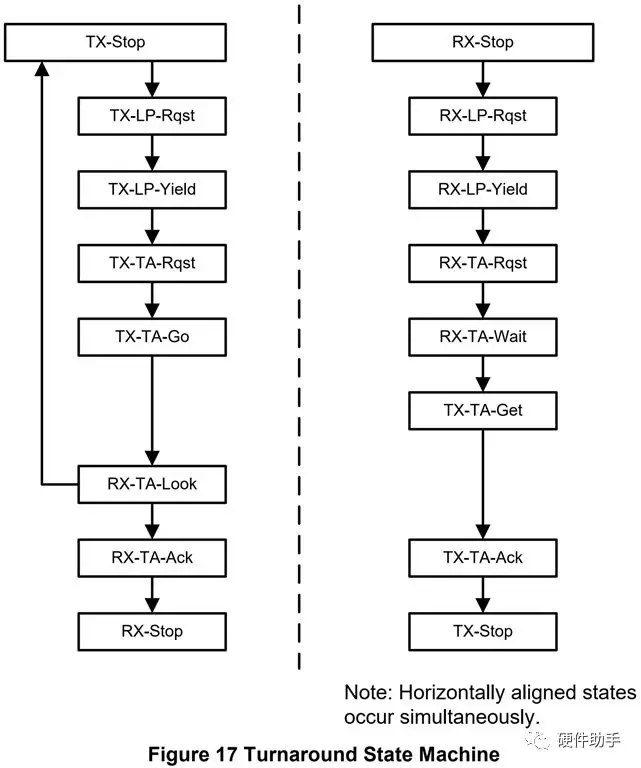

2.2、Bi-directional Data Lane Turnaround

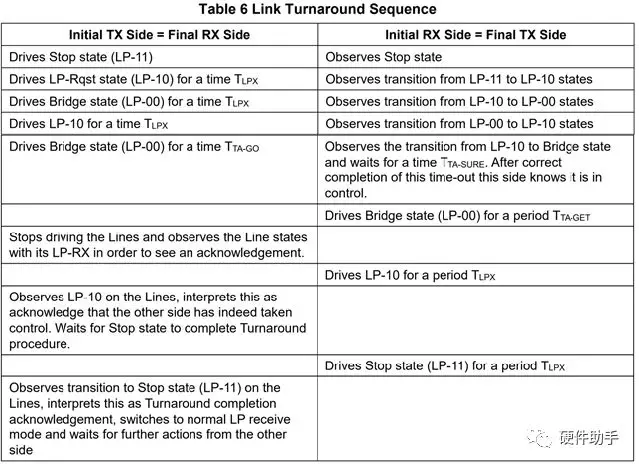

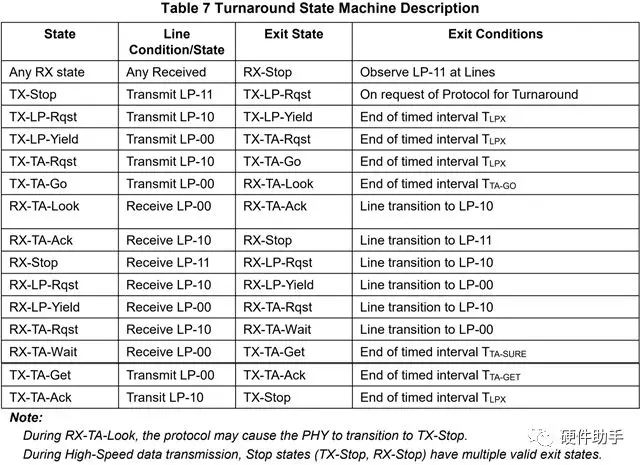

Turnaround的流程如下所示:

当通道没有进入driver overlap阶段之前,如果通道上有STOP状态出现,反转过程可以被打断,当Lane已经完成了driver overlap,通道已经完成了反转,此时再有STOP状态也不能打断turn around过程。

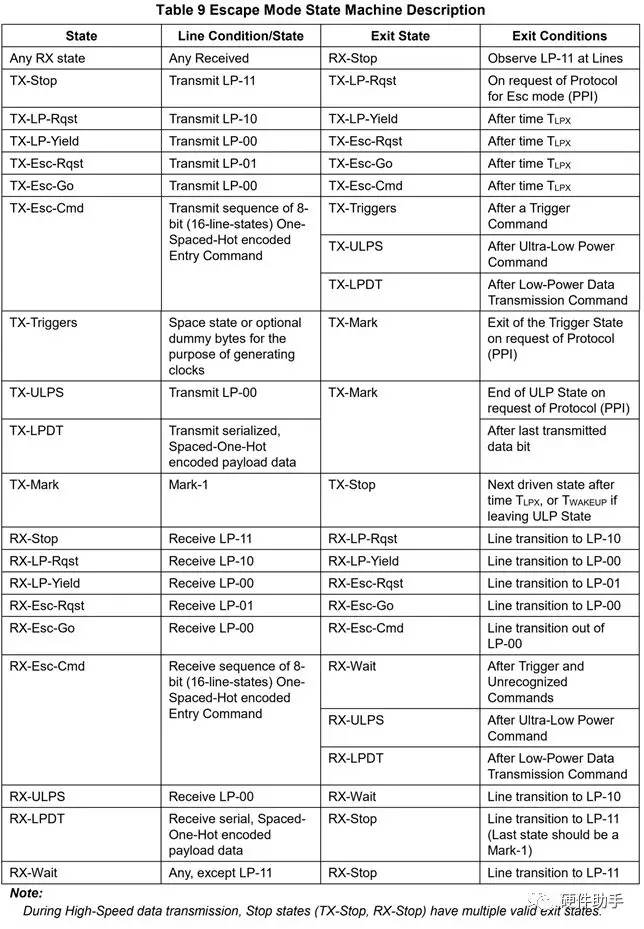

2.3、Escape Mode

LP Escape Mode特性如下:

Does not depend on clock lane

Maximum data rate 10 Mbit/s

Low power data transfer

Ultra low power mode

4 remote triggers

2 reserved functions

8-out-of-256 codes selected for maximum robustness

In case of code mismatch everything is ignored tillnext Stop state

当检测到LP-11→LP-10→LP-00→LP-01→LP-00序列的最后一个LP-00时,就进入了Escape模式。

进入Escape模式后,Data lane上发送的数据都经过了spaced-one-hot编码,每个有效的位置(Mark)后都跟着一个Space。只有STOP之前的最后一个Mark1才不需要跟随一个Space。

当线上检测到第二个LP00(bridge)状态后,通道进入Escape Mode,标志当前状态为space state,在Bridge状态之前,线上检测到任何LP11状态都会导致通道尝试进入Escape模式的努力失败,通道重新返回STOP状态。

由于Space-one-hot编码的特性,PHY不需要Clock Lane来进行解码,如果电路特性满足要求,使用D+和D-就可以恢复出Escape Mode下的Clock信号。由于D+和D-上的Mark是差分的(即D+为Mark0的时候,D-上一定是Mark1状态),只需要把D+和D-简单叠加即可还原出CLK波形。

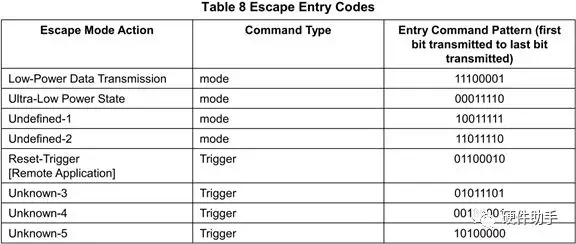

Data Lane进入Escape模式后,发送方需要发送一个8bit的模式选择命令来表明请求的类型,下表是模式选择命令的具体对应关系:

LPDT模式是Escape模式的一种,可以进行低速的数据传输,其数据编码仍然是采用Spaced-one-hot方式。需要注意的是,LPDT模式有Pause模式,在此模式下,传输可以暂停。如上图红线框出的区域。负载(Payload)是一次数据传输中,实际有效传输的内容数目,最小单位为字节。在传输过程中,为了确保Burst传输的正确性,需要在有效数据的前后添加一些辅助头和辅助尾。MIPI协议没有对Payload的最大值作出规定,但是考虑到Payload太小会降低传输效率,太大的话由于误码率的影响会导致频繁的重传,需要使用者权衡出一个比较合适的Payload值。

3、电气特性

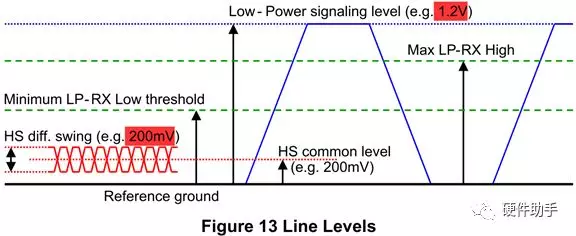

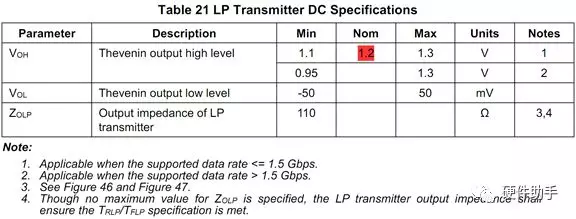

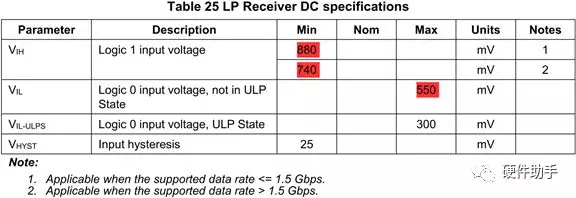

D-PHY两种工作模式的硬件信号不一样,HS模式为LVDS信号,LP模式为LVCMOS信号,其信号电平如下所示:

以上就是针对D-PHY的硬件架构、操作模式、模式转换、电气特性等的简单介绍,详细可参考《MIPI D-PHY℠ v2.1, 28-Mar-2017》,其中有详细介绍。

文章转载自:硬件助手