作者:常凝,闫瑞军等; 来源:电子技术应用ChinaAET

摘要:本文提出了一种基于CAZAC序列的OFDM时频同步方案,给出了方案各部分的FPGA实现框图和硬件电路实测效果。首先利用时域同步参考符号进行分段相关得出定时估计,然后结合最大似然法进行粗小偏估计,再将同步参考符号和FFT解调变换至频域,利用两个符号中所填充的CAZAC序列的差异性完成整偏估计,最后使用这两个同步参考符号进行细小偏估计。理论分析与仿真结果表明,与传统方案相比,本方案定时估计性能较好,频偏估计精度高,同时具有很好的工程实用性。

0 引言

现代移动通信的目标是具有更快的传输速率、更好的传输质量、更好的频谱效率以及更大的系统容量。若要在多径、衰落等环境下实现上述目标,具有传输速率高、频谱效率高以及抗多径能力强等优势的OFDM技术成为首选[1]。存在频偏时,OFDM各子载波间的正交性破坏引发同信道干扰,因此,同步问题已经成为OFDM技术中主要问题之一[2]。已有大量文献对此做了研究,主要可以分为3类:基于循环前缀的同步算法[3]、基于特殊结构性的同步算法[4]以及基于训练序列的同步算法[5-7]。

文献[3]中,由于使用CP定时,存在高原区,精度不高,在多径信道的影响下甚至不能工作;文献[4]使用共轭对称结构的特殊性进行同步定时,在低信噪比下表现不佳,且在FPGA实现上较为繁琐。文献[5]中,利用CAZAC序列构造的训练序列在时域具有前后重复的结构,同时利用PN序列进行加权,使得定时度量函数具有十分尖锐的峰值,但是PN序列加权破坏了训练序列的前后重复性,导致其多径信道下小数频偏估计性能不高;文献[6]利用两段不同的CAZAC序列进行时域定时,同样具有相当尖锐的峰值,但是CAZAC序列的加权操作过于繁杂,不利于在FPGA侧实现,同时整偏估计时,CAZAC序列加权时精度的选择直接影响结果的准确性,在多径情况下会产生较大的影响;文献[7]利用CAZAC序列良好的自相关与互相关性完成定时估计以及频偏估计,但是在频偏影响下,定时性能非常易受频偏影响。

因此,本文提出一种基于CAZAC训练序列的时频同步方案,性能上既可以满足要求,同时可进行工程实现,采用资源少,是一种可实现并且性能较优的方案。

1 系统模型

假设N为OFDM所作FFT的点数,Nu为使用的子载波的个数[8],Xk为传输的调制符号,则作IFFT后的输出为:

2 同步方案

2.1 训练序列设计

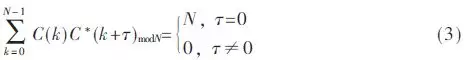

CAZAC序列具有良好的自相关性和互相关性,周期为N的CAZAC序列C(k)的自相关特性是一个脉冲函数:

式中mod表示取模。而且CAZAC序列包络恒定,峰均比低,其傅里叶变换的序列也满足CAZAC序列的特性。因此本文取CAZAC序列作为同步训练序列,生成式为:

式中,Nu为序列在频域上的长度,即一个OFDM的有效子载波个数。同时取r1、r2(r1≠r2)生成两个相同长度Nu的CAZAC序列C1(k)、C2(k),将它们分别在频域填充两个训练序列的有效子载波。同时取r3=|r2-r1|生成长度为Nu的CAZAC序列C3(k),并且在频域满足C2(k)=C1(k)C3(k)。经过OFDM调制,发送长度为2(N+Ng)的同步训练符号,Ng为OFDM符号的CP长度。

2.2 定时同步

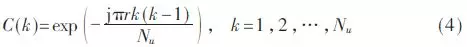

本文中定时同步估计利用训练符号时域序列的自相关性,使接收到的信号与本地序列进行滑动分段相关,从而估计出定时位置。由于CAZAC序列极易受到频偏的影响,造成定时同步估计不准确,因此采用分段共轭相关的方法克服,定时估计函数为:

其中r为接收到的信号,c为本地的定时同步训练序列的时域数据,K为分段的个数,M为分段共轭相关的长度,满足KM≤2(N+Ng)。

由于噪声和多径的影响,设定固定门限获取定时位置有可能出现虚警或漏警的情况,因此本文中采用动态门限作为参考值。用当前时刻定时函数值与其前N个时刻定时函数值总体求取平均的值,作为当前时刻动态门限的基准门限值,即序列第r个数的基准门限为:

根据得出的基准门限的大小选择相应的系数值mul,随后得到当前的动态门限T(r)=TBase(r)·mul。门限的系数值mul由MATLAB仿真得出经验值。

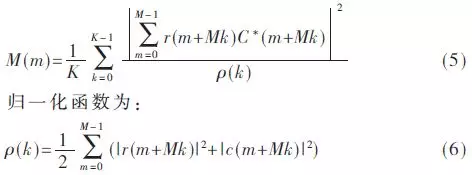

该算法的FPGA实现框图如图1所示。为了减小算法复杂度,这里取符号位进行相关运算,ρ(k)为一常数,从而省略了归一化的过程。

图2给出了使用正常的同步参考符号进行相关运算与取符号位进行相关运算的对比,这里假设OFDM系统IFFT点数为1 024,系统子载波数为751。从图中可以看出,它们的相关函数曲线性能差异并不大,但在工程实现中,正常序列相关函数的实现需要2(N+Ng)个乘法器、1个除法器;而取符号序列相关函数的实现则将乘法器变成了选择器,并且省略除法器的使用,在文中,2.4、2.5节的算法均可以使用此方法。

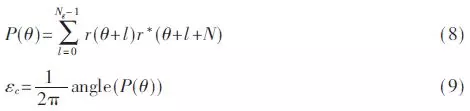

2.3 粗小数倍频率偏移估计

已知粗定时估计的位置,本文使用CP完成粗小数倍频率偏移估计[3]。

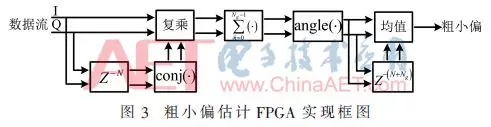

式中,θ为定时位置,P(θ)代表的是OFDM符号的循环前缀与其对应位置的数据进行共轭相乘再求和的结果,εc为粗小偏估计的结果。为了保证估计到的粗小数倍频率偏移更为精确,可使用多个OFDM符号的循环前缀进行估计求平均值的方法。该算法的FPGA实现框图如图3所示。

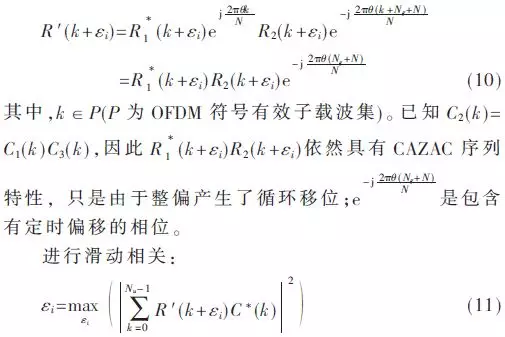

2.4 整数倍频率偏移估计

根据定时的结果,将同步符号数据取出作FFT变换至频域后得到R(k)[2]。此时由多径影响,若粗定时定位有一定的误差,在频域则表现为连续相位的扭转。

令R1(k)和R2(k)分别表示频域的第一个与第二个的训练符号,当有整数倍频偏存在,且定时位置有θ的偏移量时,检测出序列:

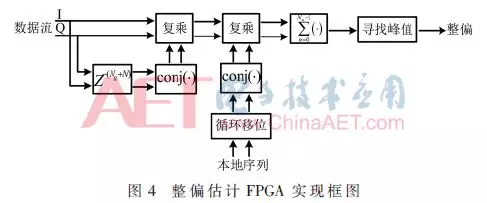

即可得到整偏值,整偏估计范围为(-N/2,N/2)。该算法的FPGA实现框图如图4所示。

2.5 细小数倍频率偏移估计

由训练符号设计可知,C1(k)=C2(k)C3(k)。当定时、频偏理想的情况下,对C2(k)进行加权,这时两个训练符号在频域上一致,可以利用它们进行细小数倍频率偏移估计。

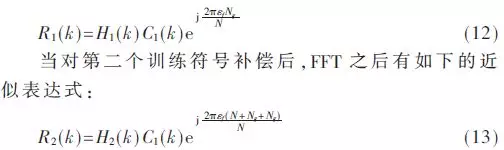

当对第一个训练符号补偿后,FFT之后有如下的表达式:

其中,εf为系统残留频偏,H1(k)、H2(k)为信道频率响应,k∈P(P为OFDM符号有效子载波集)。

假设信道是一个缓变的信道,那么对第一个训练符号和第二个训练符号解调之后,子载波的相关运算可以得到如下的结果:

取出上式的相位角,就可以求出在OFDM频域某个离散导频点上细小偏和采样偏共同作用所造成的相位偏差因子:

由于信号经过信道会受到各种干扰,因此任一组估计值都有误差,为了减小这一误差,对获得的Nu组估计值取平均可以得到:

该算法的FPGA实现框图如图5所示。

3 仿真分析

以下通过仿真验证这种方法在AWGN信道和多径信道下的性能。仿真参数为:FFT点数1 024,循环前缀长度256,有效子载波数751,子载波间隔12.5 kHz。多径信道取ITU-M.1225 Vehicle Channel B信道。AWGN信道和多径信道的归一化频率偏移都取4.2。

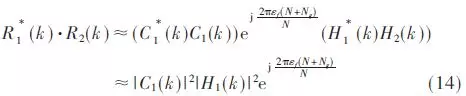

图6分别给出了高斯信道(图6(a))和多径信道(图6(b))下本文算法与文献[3]、文献[4]的算法对同步定时估计方差的性能对比。测试信号为500个连续的OFDM信号帧。从图6(a)可以看出,文献[3]的方法在定时方面准确率不如后两种,尤其是在低信噪比下;文献[4]的方法由于采用了共轭对称结构,除在低信噪比下性能不佳外,其他的信噪比下MSE为零,具有较高的准确率;本文算法的定时估计MSE为零,性能最好。从图6(b)可以看出,由于在多径信道下,CP受到较大的影响,文献[3]的方法失效;而文献[4]的方法在低信噪比下共轭对称结构遭到破坏,系统性能不佳;本文的方法在低信噪比下具有较好的性能。

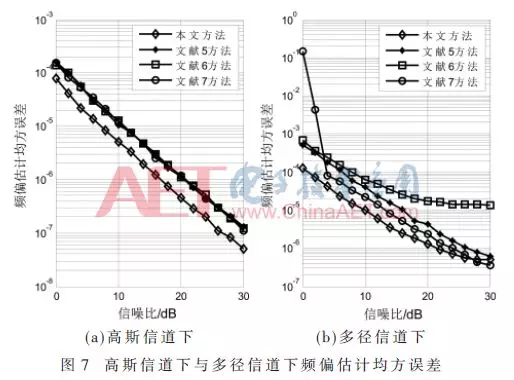

图7分别给出了高斯信道(图7(a))和多径信道(图7(b))下本文算法与文献[5]、文献[6]、文献[7]的算法对载波频偏估计方差的性能对比。由图7(a)可见,文献[5]、文献[6]、文献[7]的性能非常接近,而本文算法的性能要优于其他3种算法,性能较好。由图7(b)可见,文献[6]的性能最差,出现了严重的地板效应;文献[7]在低信噪比时会有严重的性能损失,这是因为它很大程度上依赖于定时位置,在多径信道同时附加有一定的频率偏移时,会受到严重的影响,到4 dB之后性能比文献[5]要好一些;本文提出的算法性能要好于其他3种算法,因为在多径信道中,虽然CP容易受到符号间干扰,但是本文的整偏估计利用差分的方法较其他方法可有效地抵抗多径影响,同时利用CAZAC序列加权的方法进行细小偏估计,进一步减小了干扰的影响,提高了频偏估计的性能。

4 FPGA实验验证

本文使用AD对70 MHz的中频信号进行欠采样,将AD输出的数字中频信号送入FPGA进行数字下变频,之后对基带数字信号进行同步解调。

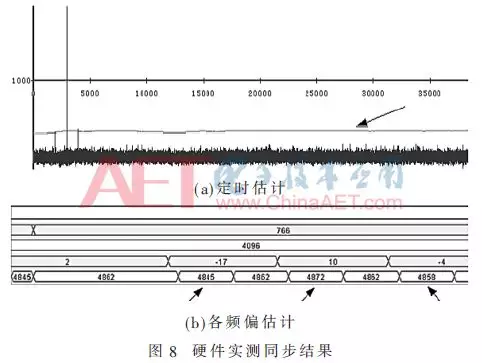

图8为系统在7 dB的高斯噪声,15 kHz的载波频偏环境时,结果采用10跳组成一帧(10 ms),每帧第一跳进行定时、粗小偏与整偏估计,剩余9跳只进行细小偏估计的方法,使用Xilinx公司提供的Chipscope嵌入式逻辑分析仪实测的同步结果。

图8(a)中箭头所标注的线是动态门限,另外一条则是定时估计相关函数。此时所选用的系数mul数值为2.75。可以看出,动态门限的基准值是在不断变化的。当某一个峰值超过当前的动态门限时,开启比较模块,存储并且更新超过当前动态门限的值,在之后的CP个数据时间内将最新且超过动态门限以及之前存储超过动态门限的值重新定位为定时位置。图8(b)中第一行T标所标注的地方就是最后确定的定时位置。图8(b)中,前3行分别为为同步定时脉冲、粗小偏估计结果、整偏估计结果,均是每10 ms估计一次,第4行为细小偏估计结果,第五行黑标指示的则是当前跳频偏总和。以第3个黑标指示的频偏总和值为例,系统的子载波间隔为12.5 kHz,相位控制字为12 bit,估计的频偏为ε 与15 kHz的频偏只相差约170 Hz,其他黑标处估计的频偏值与实际频偏值最大相差在210 Hz,属于系统允许范围内。

与15 kHz的频偏只相差约170 Hz,其他黑标处估计的频偏值与实际频偏值最大相差在210 Hz,属于系统允许范围内。

5 结束语

本文提出了一种基于CAZAC训练序列的时频同步方案,给出了FPGA实现框图并且基于硬件平台给出了硬件实测结果与分析。提出的定时同步方案在多径信道以及频偏影响的情况下实行分段相关、符号位相乘的方法,同时使用动态门限极大地提高了定时同步的性能,并且FPGA实现复杂度较低;频偏估计方案有效地利用了训练符号差分去相位的结果,在多径信道的情况下整偏估计的准确率有所提高,同时使用加权的方法针对训练符号进一步细小偏估计,提高估计精度。仿真结果表明,此同步系统的设计可以在多径信道以及频偏影响的情况下很好地完成频偏估计以及定时估计,FPGA实测表明本文算法可用于工程实现,能实现较为准确的同步估计。

文章转载自:电子技术应用ChinaAET