作者:OpenSLee,来源:FPGA开源工作室

FPGA开源工作室将通过五篇文章来给大家讲解xilinx FPGA 使用mig IP对DDR3的读写控制,旨在让大家更快的学习和应用DDR3。

本实验和工程基于Digilent的Arty Artix-35T FPGA开发板完成。

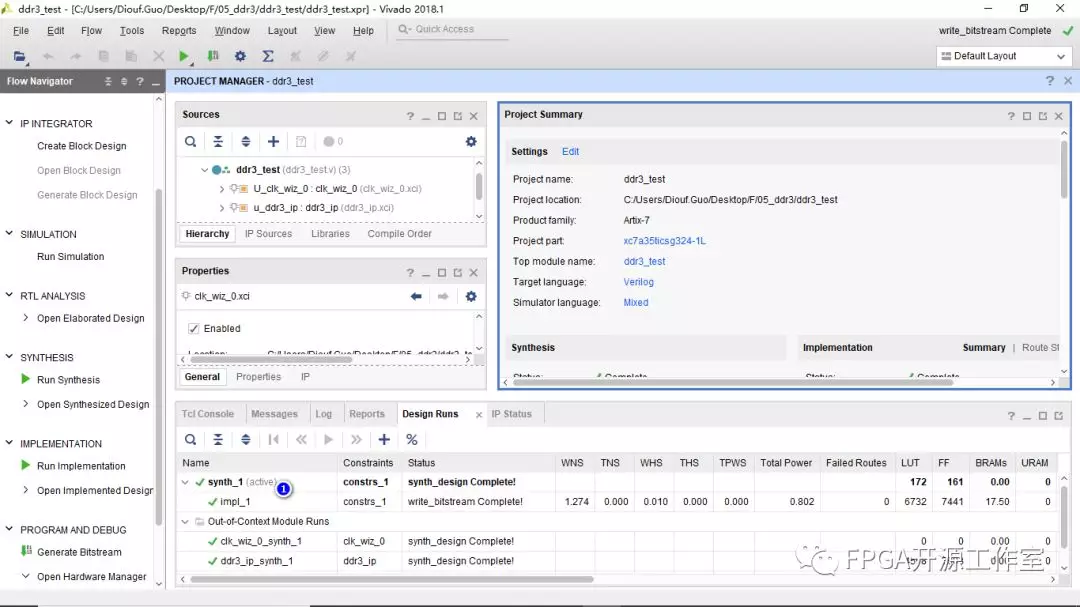

软件使用Vivado 2018.1。

参考工程:ddr3_test。

第五篇:mig读写时序下板实现

1顶层文件和约束文件

ddr3_test.v

参见参考工程:ddr3_test。

ddr3.xdc

1. set_property PACKAGE_PIN E3 [get_ports clk]

2. set_property IOSTANDARD LVCMOS33 [get_ports clk]

3. set_property PACKAGE_PIN D9 [get_ports reset]

4. set_property PACKAGE_PIN E1 [get_ports init_calib_complete]

5. set_property IOSTANDARD LVCMOS33 [get_ports init_calib_complete]

6. set_property IOSTANDARD LVCMOS33 [get_ports reset]

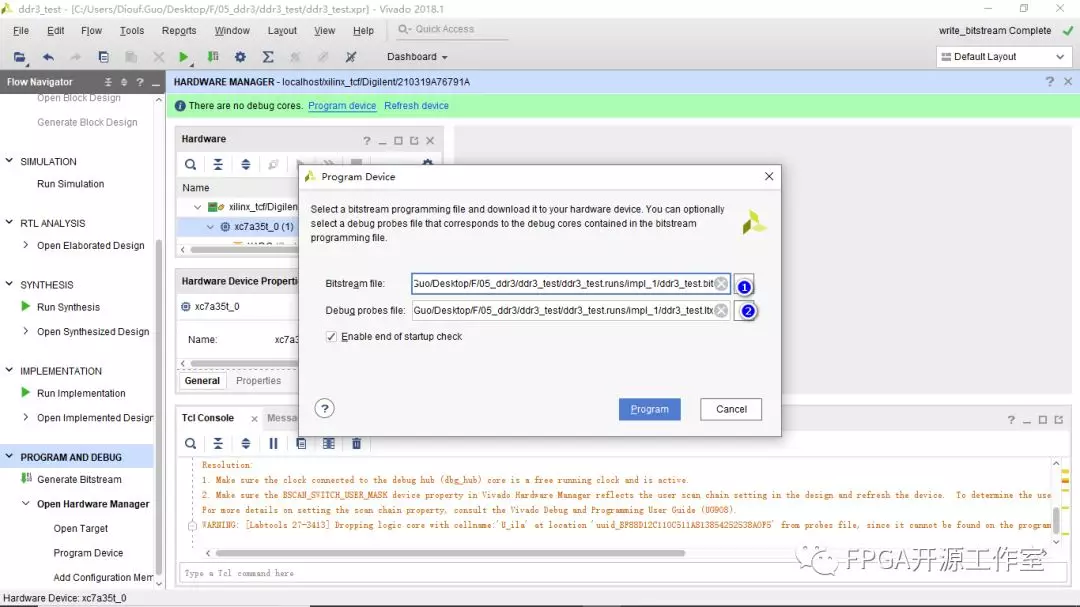

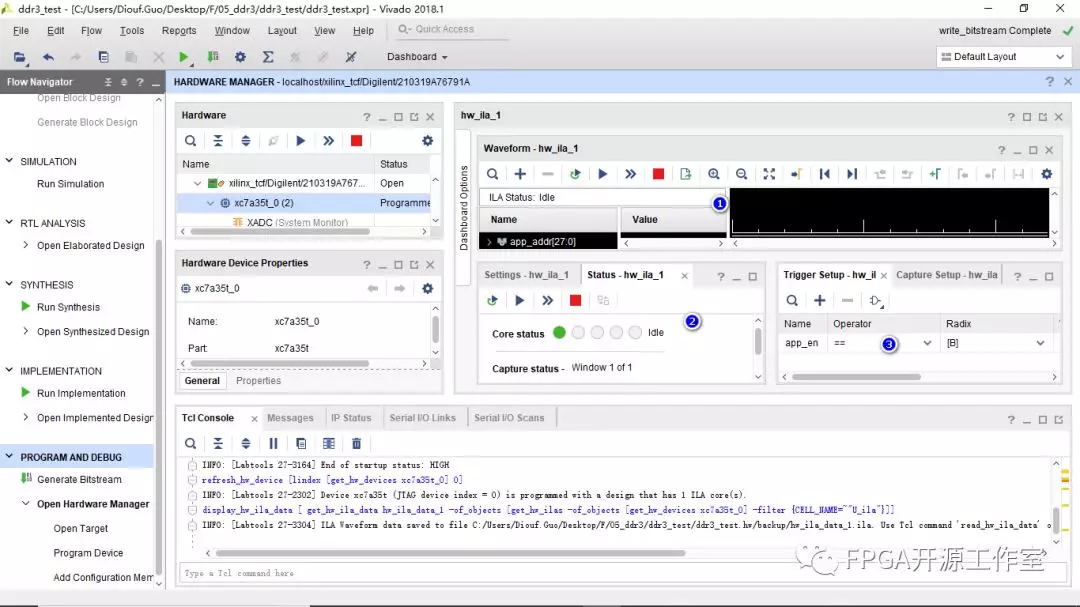

2 下板实现读写时序

1>①完成综合和实现

2>下载bit文件和debug文件。

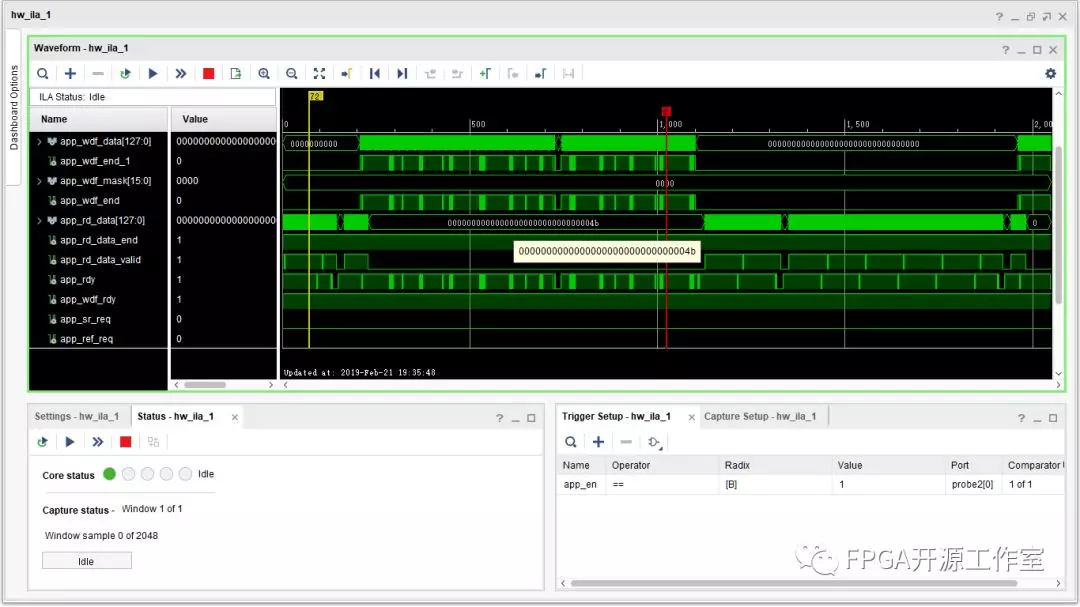

3>下载完成,查看波形。

4>将app_wdf_data数据格式改为Unsigned Decimal。

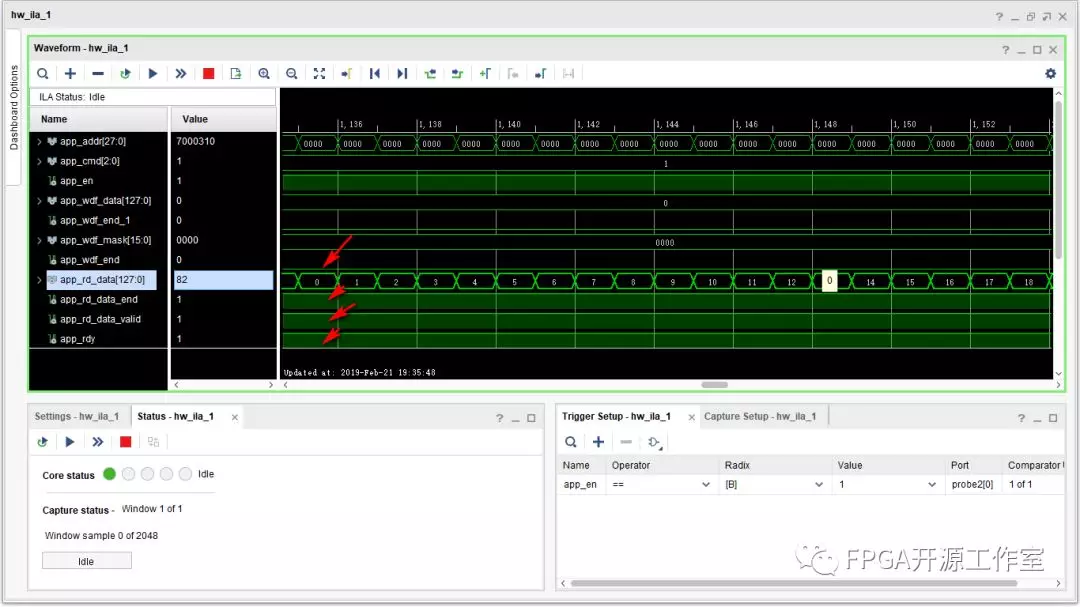

5>查看写时序。

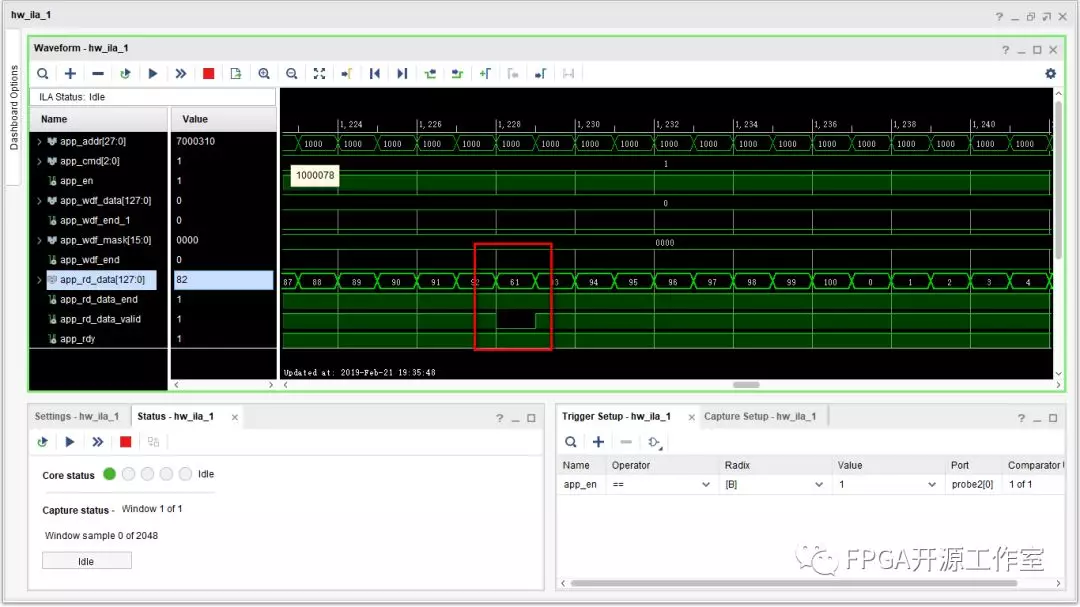

6>查看读时序。

基于xilinx mig ip对ddr3读写验证完成。

文章转载自:FPGA开源工作室