Vivado是Xilinx公司的FPGA开发工具,熟悉Xilinx的工程师应该对ISE比较不陌生,但是随着时代的发展,FPGA芯片进步很快,Xilinx也已经宣布不再对ISE进行更新,这就意味着Vivado将在以后的发展中逐渐取代ISE,所以掌握好Vivavo的使用,是一个FPGA工程师必备的技能。今天的文章主要是讲解怎么调用Modelsim进行仿真。

本次使用的Vivado版本为Vivado_2017.3版本,从Xilinx官方文档可以了解到,该版本的Vivado只支持Modelsim10.6或者更高版本,但是笔者只有Modelsim10.5,发现Modelsim10.5的版本也是可以使用的。笔者尝试过Modelsim10.4,发现该版本不支持。所以需要使用Vivado2017.3来调用Modelsim的工程师,需要选择正确的Modelsim版本。否者将调用失败。

下面将讲解怎样使用Vivado调用Modelsim

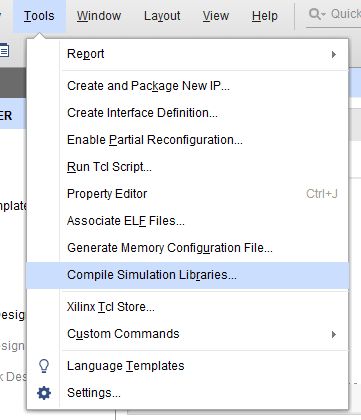

第一步:选择“Tools”在下拉菜单中选择“Compile Simulation Libraries...”

图1、选择 “Compile Simulation Libraries...”选项

第二步:如图2所示,“Compiled library location:”是生成库的位置,可以自行设置。

“Simulator executable path:”选择安装Modelsim路径的“win64”文件夹目录。由于笔者使用的是64位系统和64位Modelsim安装包,所以Compile 32-bit libraries这个选项不用勾选,具体64位系统勾选是否能运行,尚未尝试。如果您是32位的Modelsim和系统,建议勾选。设置完毕,点击“Compile”选项,开始编译库。

图2、库路径选择

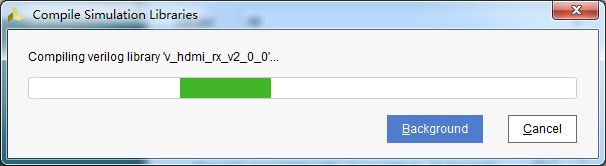

图3、库生成中

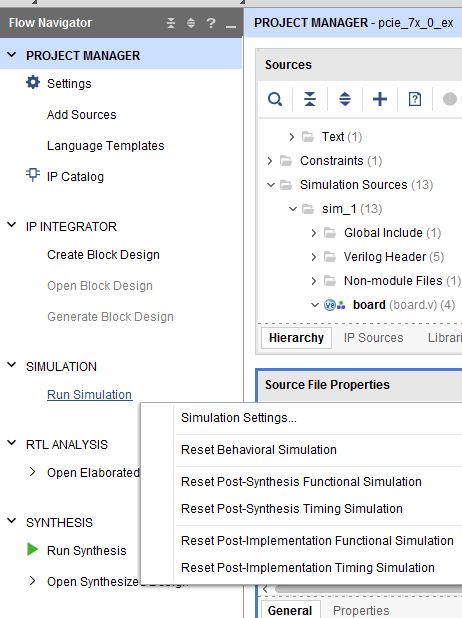

第三步:完成库的编译之后,打开一个有仿真激励的工程,在“Flow Navigator”窗口中,有个SIMULATION,展开有个Run Simulation ,然后右键,选择“Simulation Settings...”

在这里说一点题外话,提及到Flow Navigator 窗口可能有些读者,甚至半吊子的老司机会一时半会不知道是哪里,FPGA开发软件的窗口可能我们都熟悉,但是每个窗口是有对应的名字的,希望大家能够对基本窗口的名字有所了解,起码提倒哪个窗口的时候,能够反应过来。

图4、选择仿真设置

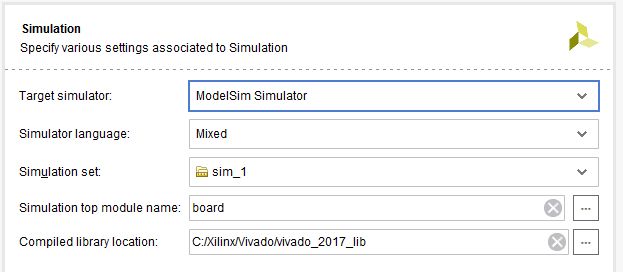

选择进去后,看到如图5的界面。“Target simulator”选择“Modelsim Simulator”

“Compiled library location:”选择您刚才生成库的目录。其它保持默认即可。

图5、仿真设置

最后点击OK完成设置。

第四步:在图4中,左键Run Simulation就出现仿真选项,一般选择第一个行为仿真。到这里,Modelsim就可以调用成功了。

最后需要提及一点:用过ISE调用Modelsim的工程师可能还记得,在ISE调用Modelsim的时候,需要在Modelsim的.int文件添加库路径,在Vivado上是不需要这个操作的。

介于有读者提出为什么不直接使用Modelsim。笔者这篇文章只是告诉大家怎么从Vivado调用,以后的使用还是建议多从Modelsim直接建立工程,待掌握好了Modelsim,相信你们也会知道Vivado或者ISE调用的原理了,它也是生成do文件执行的!