作者:Del Jones,ADI应用工程师

在JESD204C入门系列的 第1部分 中,通过描述它解决的一些问题,对JESD204标准的新版本进行了说明。通过描述新的术语和特性来总结B和C版本标准之间的差异,然后逐层概述这些差异。因为第1部分已经奠定了理解基础,现在我们来进一步研究一下JESD204C标准几个更值得注意的新特性。

64b/66b和64b/80b链路层

对于64b/66b链路层,66位数据块由两个同步头位,后接八个八位位组的样本数据组成,其中部分是基于IEEE 802.3第49条定义的数据块格式。与IEEE标准不同的是,它没有编码——有效载荷数据只是转换器样本数据,由传输层打包到数据帧中。由于没有编码来确保发生一定数量的数据转换来提供dc平衡,因此必须对样本数据进行加扰。这些加扰的八位位组的帧数据被直接放入链路层,两个同步头位附加在其中。

64b/66b数据块的格式如图1所示。该示例展示了这样的情况: 一个数据通道由帧组成,每个帧包含来自一个转换器的一个样本。块映射规则与来自JESD204B标准的帧映射规则非常相似。按顺序完成八位位组到64位数据块的映射,其中D0表示帧的第一个八位位组。例如,如果F = 8,D0表示JESD204C帧的第一个八位位组,D7表示JESD204C帧的最后一个八位位组。该帧的第 一个八位位组的MSB是Converter0的Sample0的MSB(与JESD204B一样)。例如,如果F = 2,D0和D1代表第一个帧,D2和D3代表第二个帧,以此类推。

为了与JESD204B中使用的方法保持一致,多块中的八位位组按MSB到LSB的顺序被转移到加扰器/解扰器中。

在E = 1的情况中,每个多块都从帧边界开始。如果E > 1,扩展多块将从(必须从)帧边界开始。有关更多信息,请参考多块 (MB)和扩展多块(EMB)章节。

图1. 64b/66b数据块格式示例,LMFS = 1.1.2.1,N = N’ = 16

同步头是一个2位未加扰值,位于每个数据块的开始位置,其内容经过解析之后,用于解码单个同步转换位。这些位要么采用0-1序列,表示逻辑1,要么采用1-0序列,表示逻辑0。表1列举了同步头的转换位值。

表1. 同步头位值

| 值同步头位(0.1) | 同步转换位 |

| 00 | 无效 |

| 01 | 1 |

| 10 | 0 |

| 11 | 无效 |

64b/80b数据块的格式如图2所示。除了样本数据的八个八位位组和两个同步头之外,还具有两个填充位,位于每个八位位组之间。填充位的值由17位PRBS序列决定,以减少杂散,并确保适当数量的数据转换以保持dc平衡。未加扰的填充位在样本数据加扰之后插入到块中。

图2. 64b/80b数据块格式示例,LMFS = 1.1.2.1,N = N’ = 16

提供64b/80b选项是为了与8b/10b保持相同的时钟比,帮助简化锁相环(PLL)设计,同时最小化杂散。对于希望通过使用前向纠错或利用同步字提供的其他功能的应用,相比8b/10b,更应该选择64b/80b,稍后将就这一问题进行详细讨论。

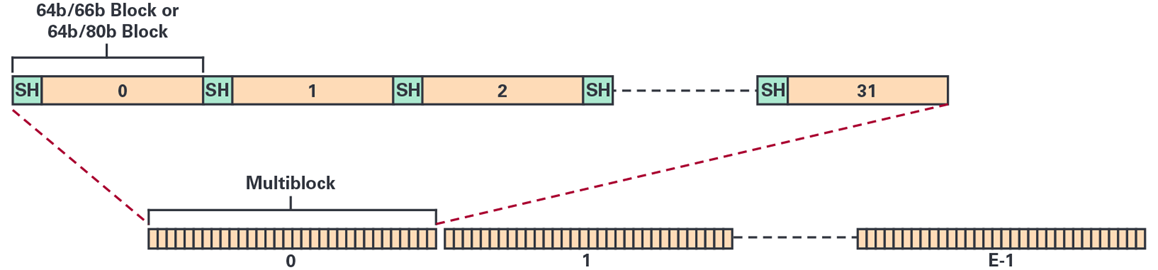

多块(MB)和扩展多块(EMB)

JESD204C多块中包含32个块。每个多块中的32个同步转换位构成一个32位同步字。稍后,我们将就此进行详细讨论。扩展多块是一个E多块容器,必须包含整数数量的帧。当多帧不包含整数数量的帧时,要求E > 1。多块和扩展多块的格式如图3所示。

图3. JESD204C多块和扩展多块的格式

多块可以是2112 (32×66)位,或者是2560 (32×80)位,具体由所用的64位编码方案决定。对于大多数场景,扩展多块只是一个多块。JESD204C中引入了E参数,确定了扩展多块中的多块数 量。E的默认值为1。如上所述,当帧F中的八位位组的数量不是2的倍数时,该配置要求E > 1。E的公式为:E = LCM(F, 256)/256。发送12位样本且N’ = 12时,一般选择这些配置,以最大化链路中的带宽效率。这一要求确保EMB边界与帧边界一致。

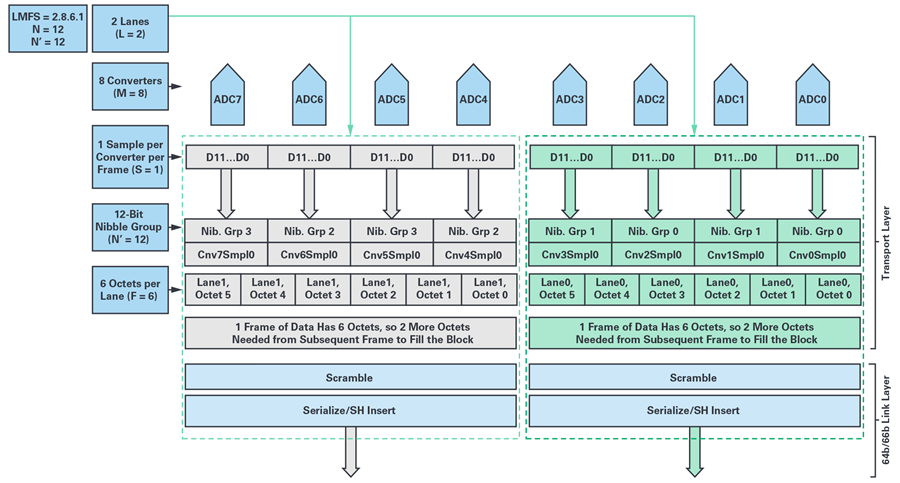

图4和图5所示为E > 1的JESD204C配置示例。所示的JESD204C配置适用于以下情况:LMFS = 2.8.6.1,N’ = 12,E = 3。图4显示 了传输层的映射情况。在这个配置中,每个通道有4个12位样本,相当于6个八位位组。由于多块的每个块都需要8个八位位组,因此该块中填充了来自后续帧的2个八位位组(1.33个样本)。

图4. 传输层映射,LMFS = 2.8.6.1,N’ = 12,E = 3

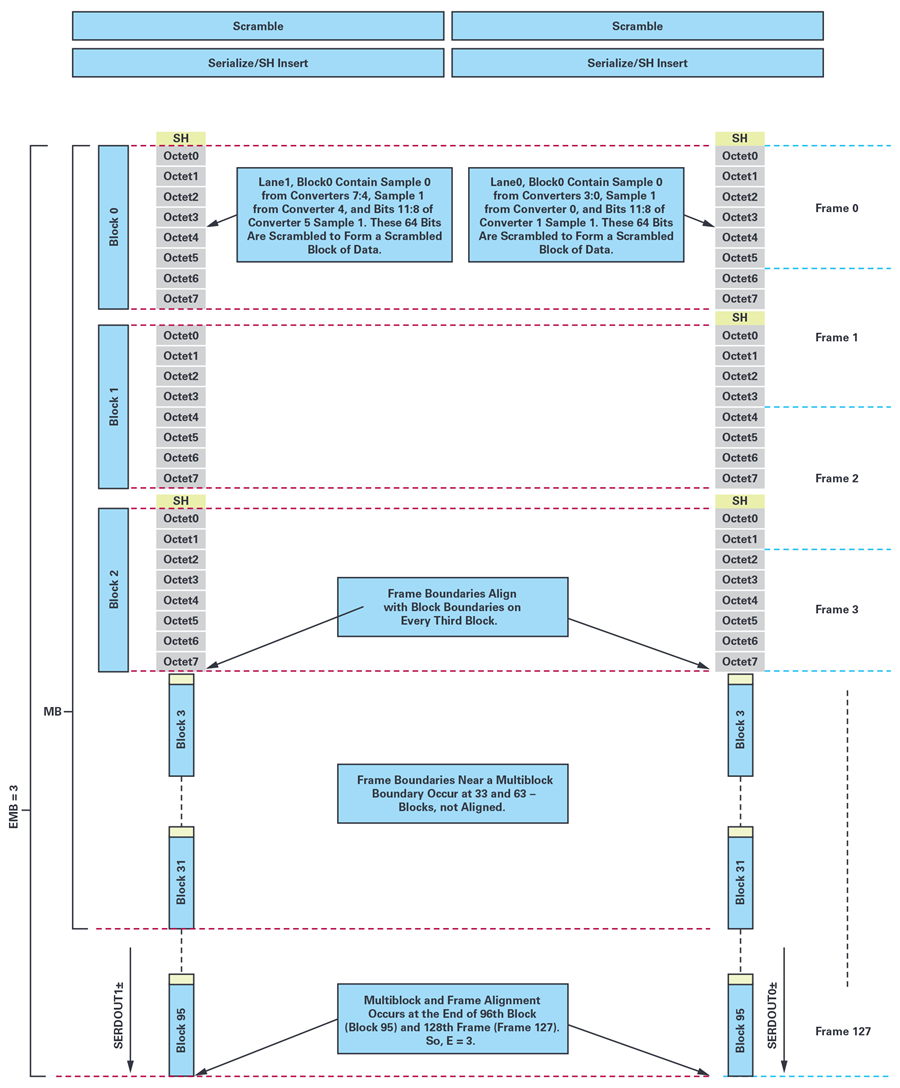

图5显示了如何使用来自传输层的数据帧来形成块和多块。如图所示,可以看到帧边界与每三个块的块边界对齐。由于多块由32个块组成,所以要在第三个多块之后才能和多块对齐。因此,E = 3。

图5. 串行输出多块/帧对齐,LMFS = 2.8.6.1,N’ = 12,E = 3

LEMC是扩展多块计数器,大致相当于8b/10b链路层中的LMFC。SYSREF对系统中的所有LEMC进行对齐,并使用LEMC边界来确定同步和通道对齐。

同步字

32位同步字由多块中32个块的每个同步头位组成,其中第一个传输的是位0。同步字用于提供通道同步,并使能确定性延迟。此外,它还可以选择性地提供CRC错误校验、前向纠错,或者提供一个命令通道,供发射器与接收器通信。

32位同步字有三种不同的格式选项。在每种情况下,都需要多块序列的结束,因为它用于获得多块同步和通道对齐。表2和表3显示了两个最常见用例中可用的不同位字段。

表2. CRC-12同步字

| 同步字位 | 域名 | 功能 |

| 0 | CRC11 | 12位CRC值的位11:9—适用于之前的多块 |

| 1 | CRC10 | |

| 2 | CRC9 | |

| 3 | 1 | 始终为1 |

| 4 | CRC8 | 12位CRC值的位8:6—适用于之前的多块 |

| 5 | CRC7 | |

| 6 | CRC6 | |

| 7 | 1 | 始终为1 |

| 8 | CRC5 | 12位CRC值的位5:3—适用于之前的多块 |

| 9 | CRC4 | |

| 10 | CRC3 | |

| 11 | 1 | 始终为1 |

| 12 | CRC2 | 12位CRC值的位2:0—适用于之前的多块 |

| 13 | CRC1 | |

| 14 | CRC0 | |

| 15 | 1 | 始终为1 |

| 16 | Cmd6 | 7位命令通道的位7:5 |

| 17 | Cmd5 | |

| 18 | Cmd4 | |

| 19 | 1 | 始终为1 |

| 20 | Cmd3 | 7位命令通道的位4:2 |

| 21 | Cmd2 | |

| 22 | Cmd1 | |

| 23 | 1 | 始终为1 |

| 24 | Cmd0 | 7位命令通道的位0 |

| 25 | 1 | 始终为1 |

| 26 | EoEMB | 扩展多块结束位 |

| 27 | 0 | 多块结束导频信号 |

| 28 | 0 | |

| 29 | 0 | |

| 30 | 0 | |

| 31 | 1 |

表3. FEC同步字

| 同步字位 | 域名 | 功能 |

| 0 | FEC[25] | 26位前向纠错字的位25:4—适用于之前的多块 |

| 1 | FEC[24] | |

| 2 | FEC[23] | |

| 3 | FEC[22] | |

| 4 | FEC[21] | |

| 5 | FEC[20] | |

| 6 | FEC[19] | |

| 7 | FEC[18] | |

| 8 | FEC[17] | |

| 9 | FEC[16] | |

| 10 | FEC[15] | |

| 11 | FEC[14] | |

| 12 | FEC[13] | |

| 13 | FEC[12] | |

| 14 | FEC[11] | |

| 15 | FEC[10] | |

| 16 | FEC[9] | |

| 17 | FEC[8] | |

| 18 | FEC[7] | |

| 19 | FEC[6] | |

| 20 | FEC[5] | |

| 21 | FEC[4] | |

| 22 | EoEMB | 扩展多块结束位 |

| 23 | FEC[3] | 26位前向纠错字的位3:0—适用于之前的多块 |

| 24 | FEC[2] | |

| 25 | FEC[1] | |

| 26 | FEC[0] | |

| 27 | 0 | 多块结束导频信号 |

| 28 | 0 | |

| 29 | 0 | |

| 30 | 0 | |

| 31 | 1 |

64b/66b链路操作

当使用64b/66b链路层时,链路的建立过程从同步头对齐开始,然后是扩展多块同步,最后是扩展多块对齐。

同步头对齐

同步头中的同步转换位确保在每个块边界(66位)都有一个数据转换。JESD204C接收器中的状态机检测到一个数据转换,在66位后再查找另一个转换。如果状态机检测到64个连续以66位间隔进行的位转换,则会实现同步头锁定(SH_lock)。如果没有检测到64个连续转换,则重新启动状态机。

扩展多块同步

一旦实现同步头对齐,接收器就会在转换位中查找扩展多块结束(EoEMB)序列(100001)。同步字的结构确保此序列只能在适当的时间发生。一旦确定EoEMB,状态机将检查每32个同步字,以确保存在多块结束导频信号(00001)。如果E = 1,EoEMB位也会存在导频信号。如果E > 1,那么每个E × 32转换位,导频信号都将包含EoEMB位。一旦检测到四个连续的有效序列,就可以实现扩展多块结束锁定(EMB_LOCK)。继续监测每个E × 32转换位,如 果没有检测到有效的序列并重置对齐过程,则EMB_LOCK丢失。

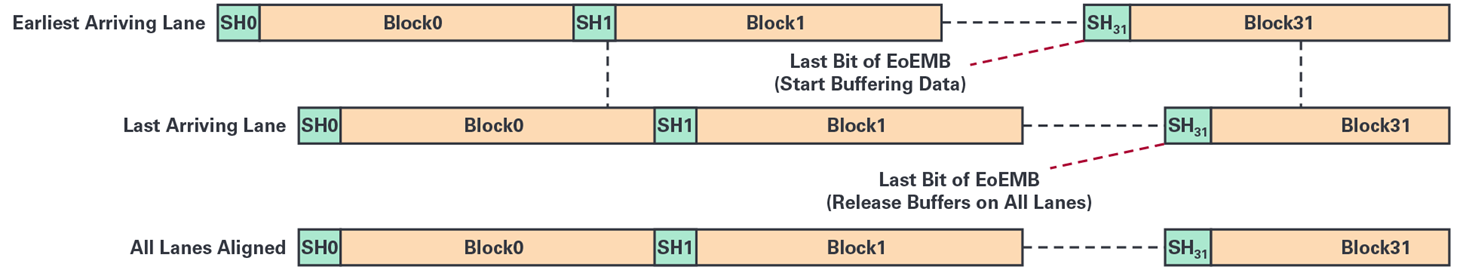

扩展多块(通道)对齐

使用64b/66b链路层时的通道对齐与使用8b/10b链路层时的通道对齐非常相似,每个通道上的JESD204C接收器都使用一个弹性缓冲区来存储传入的数据。这被称为扩展多块对齐,缓冲区开始在EoEMB边界(而不是在使用8b/10b链路层时ILAS期间的/K/至/R/边界)存储数据。图6说明了如何实现通道对齐。每个通道的接收缓冲区在接收到EoEMB的最后一位之后开始缓冲数据(最后一个接收通道除外)。接收到最后一个接收通道 EoEMB之后,会触发释放所有通道的接收缓冲区,所以现在所有通道都是对齐的。

图6. JESD204C扩展多块(通道)对齐

错误监测和前向纠错

JESD204C同步字选项让用户能够监测或纠正JESD204数据传输中可能发生的错误。纠错会导致额外的系统延迟。对于大多数应用,使用CRC-12同步字进行错误监测是可行的,因为它提供了大于 1 × 10–15的误码率(BER)。

JESD204C发射器中的CRC-12编码器接收每个多块的加扰数据位,并计算12个奇偶校验位。这些奇偶校验位在随后的多块中传输到接收器。接收器同样将从接收到的每个数据多块中计算12个奇偶校验位,并与同步字中接收到的位进行对比。如果所有奇偶校验位都不匹配,则接收到的数据中至少存在一个错误,可以触发错误标志。

对于对额外延迟不敏感但对错误敏感的应用(例如测试和测量设备),使用FEC可以得到优于 10 × 10–24的误码率。JESD204C发 射器中FEC电路计算多块中已加扰数据位的FEC奇偶校验位,并在下一个多块的同步头位流上对这些奇偶校验位编码。接收器计算接收位的校验子,本地生成的奇偶校验位和接收到的奇偶校验位之间的差异就在于此。如果校验子为0,则假定接收到的数据位正确。如果校验子非0,则可以用它来确定最可能的错误。

FEC奇偶校验位的计算方法与CRC相似。FEC编码器接收多块的 2048 位加扰数据位,并添加26位奇偶校验位,以构建一个缩短的二进制循环码。该码的发生器多项式为:

对于每个多块,这个多项式可以纠正最多9位突发错误。

总结

为了满足未来几年数据密集型应用更快处理数据的需求,JESD204C将多千兆位接口定义为数据转换器和逻辑器件之间必需的通信通道。高达32 GSPS的通道速率和64b/66b编码使超高带宽应用能以最小的开销来提高系统效率。这些和其他标准改进对于5G通信、雷达和电子战应用都大有裨益。再加上纠错功能,先进的仪器仪表和其他应用都能够无错运行多年。

有关JESD204及其在ADI公司产品中的实现的更多信息,请访问 ADI JESD204 串行接口页面。。 有关ADI高速转换器的更多信息,请 访问我们的 RF转换器页面 和 28 nm RF 数据转换器页面。 有关ADI 收发器产品的更多信息,请访问我们的 RadioVerseTM 页面。

作者:Del Jones

Del Jones是位于美国北卡罗来纳州格林斯博罗的高速转换器团队的应用工程师。他自2000年以来一直为ADI工作,负责支持ADC、DAC和串行接口。加入ADI之前,他曾在电信行业担任电路板和FPGA设计工程师。Del毕业于德克萨斯大学达拉斯分校,获电气工程学士学位。

文章转载自:ADI官网