2019年8月1日至2日,“中国开放指令生态(RISC-V)联盟”(简称CRVA联盟)与鹏城实验室,在湖北恩施举行的中国计算机学会第二十三届计算机工程与工艺学术年会暨第九届“微处理器技术”论坛(NCCET 2019)现场,联合展示了最新研发的RISC-V开源芯片设计系统级验证及原型平台SERVE(System Emulation and Prototyping for RISC-V Environment),介绍开源理念并鼓励参会人员积极参与。

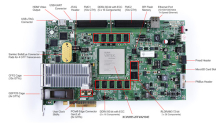

SERVE是CRVA联盟秘书长、鹏城实验室开源芯片院士工作室负责人、中科院计算所包云岗研究员的研究团队历经多年实践、自主研发的一套RISC-V系统级验证和原型平台。该平台基于目前市场上主流的SoC-FPGA可编程逻辑器件及板卡,涵盖精简普及型(SERVE.r)、高性能增强型(SERVE.i)、多节点集群型(SERVE.s)及云化服务型(SERVE.c)等多种不同规格版本,满足不同类型用户进行RISC-V软硬件系统级协同设计及验证评估的差异化需求。

与现有RISC-V的FPGA系统级验证平台相比,SERVE平台实现了RISC-V硬件系统的独立自治,可在上电后自动运行并直接控制平台上真实的物理接口;同时SERVE支持在RISC-V处理器核上运行标准Linux和Debian等主流软件生态,便于用户快速开展各类RISC-V系统级研究工作。值得一提的是,SERVE还将提供支持自研新型标签化冯·诺伊曼体系结构(LvNA)的SERVE.v版本,有效提升不同应用负载的服务质量,降低应用执行过程中的不确定性。SERVE.v已在鹏城实验室iHUB托管平台上全面开源(https://code.ihub.org.cn/projects/159),并由中科院计算所博士生余子濠带领团队维护,可供用户直接下载使用。

中科院计算所的张科和常轶松代表CRVA联盟与鹏城实验室,在展台为与会嘉宾介绍了SERVE系列平台的相关技术特色,并现场演示了低成本、低功耗的精简版平台(SERVE.r)的相关功能和应用实例,受到与会专家学者的广泛关注,并引发热烈讨论。SERVE.r平台的使用方法和启动镜像文件也已在iHUB托管平台上发布(https://code.ihub.org.cn/projects/373);相关软硬件源码也会在后续逐步开源。

SERVE系列平台将为未来RISC-V系统级原型验证提供全新的技术手段。CRVA联盟和鹏城实验室以此为契机,通过参会展示,进一步向与会各界嘉宾传递了开源硬件理念;也鼓励更多有识之士积极参与,为国内芯片领域的发展贡献力量。

文章转载自:Xilinx学术合作