作者: Mike Thompson

赛灵思 Virtex UltraScale+ 产品组合高级产品线经理

世界需要新型的先进芯片与应用

在当今热门的人工智能(AI)、5G、自动驾驶和超大规模数据中心应用领域,我们看到的一大市场趋势。就是越来越多的 ASIC 和 SoC 设计开始启动。在这些应用中,整个开发系统,随着新的芯片架构和集成软件不断更新换代变得越来越复杂。我们看到的另一个趋势,就是由于软件开发者和系统设计师希望在自己的芯片器件投入使用之前就能对实际的 I/O 流量进行测试,原型设计开始飞速发展。

赛灵思连续打破自己创造的记录!

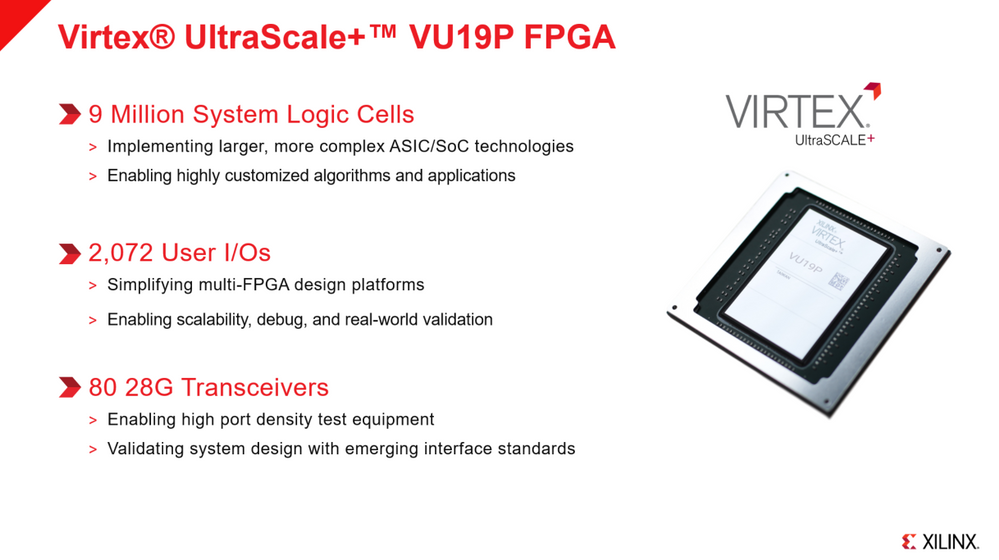

凭借 Virtex®-7 2000T FPGA 和堆叠硅片互联 (SSI) 技术,赛灵思早在十年前便在仿真级器件上居于领先地位。该产品和技术让赛灵思能够打破摩尔定律的限制,所提供的功能可满足最严苛的设计要求。凭借突破性的 UltraScale™ 架构,Virtex UltraScale VU440 FPGA 再次延续了这一领先地位,相较于当时同时期的替代产品,容量提升高达 4 倍。近日,赛灵思又推出世界上容量最大的 FPGA – Virtex UltraScale+™ VU19P FPGA。Virtex UltraScale+™ VU19P FPGA 拥有 900 万个系统逻辑单元,树立了 FPGA 设计的又一新标杆。在连续三代实现高端领导地位的同时,赛灵思也两次打破自己所创造的记录,成为世界上最大的 FPGA 的创造者。

有史以来世界最大 FPGA – Virtex UltraScale+ VU19P FPGA

拥有 900 万个逻辑单元,多达 2,072 个用户 I/O 和 80 个 28G 收发器,使得客户能够对当今最复杂的 SoC 进行仿真与原型设计,同时还能开发用于人工智能 (AI)、机器学习 (ML)、视频处理和传感器融合的各种新兴复杂算法。客户可以开发高度定制的设计,并且对新兴协议进行验证。这些新一代由 AI 驱动的算法,需要快速地将大量数据输入和输出设备,以满足算法的要求。因此,我们纳入了 80 个收发器,这是当前单颗仿真级器件拥有的最大收发器数量。需要进行仿真和原型设计的客户对 I/O 和存储器带宽有着无尽的需求,赛灵思再一次满足了客户所需。借助 2000 多个 I/O,这一全新的 FPGA 提供了更多的调试用外部存储器,为多 FPGA 环境提供更多互联,并为实际的 I/O 流量提供了足够的接口。

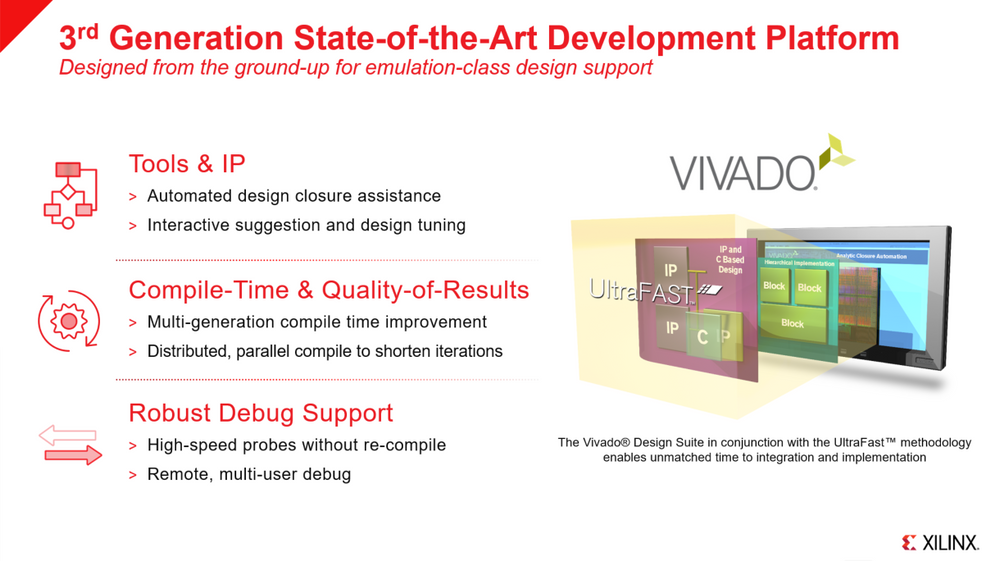

工具也变得更加好用

拥有大容量 FPGA 是一回事,如何最大限度地发挥它的潜力则是另外一回事。部署这些大型设备的最关键因素之一就是拥有稳健的开发平台。为此,我们也早在近十年前发明了面向更高集成度可编程器件开发的 Vivado® 设计套件,以满足仿真级设计的需求。三代工具发展以来,赛灵思一直在优化仿真级设计的编译时间与结果质量 ( QoR)。Vivado 仿真与原型设计的高级特性包括:自动化设计收敛辅助、交互式设计建议、智能设计优化、编译时效率、分布式并行编译、远程 & 多用户调试支持等。Vivado 是我们的第三代仿真级工具、IP 和设计流程。它提供了一种有据可查的设计流程方法,以及专为此类设计优化,包含其他工具与 IP 的成熟的生态系统。

总结

我们拥有世界上最大容量的 FPGA。还有为它提供支持的工具、设计流程和 IP。此外,我们所打造的这个 FPGA巨人,基于业经验证的 3D IC 封装技术,因此,可以全面助力您推进您的下一个大项目。

如需了解更多信息,请访问wchina.xilinx.com/vu19p。