还在为错过XDF上Lab Zone的案例体验而锤头顿足吗?

还在为不知道如何部署和使用Vitis与Vitis AI而心灰意冷吗?

大家都可以通过以下Vitis Acceleration Lab中精选出来的优秀技术分享案例来学习与跟进,帮助大家指导和使用Vitis。

Vitis Acceleration Lab

全流程加速

嵌入式视频处理通常会涉及到几个部分:视频采集、数据处理、视频显示;在一个机器学习的应用中,数据处理一般又分为前处理(比如缩放、调整白平衡等)、学习推理、对结果作后处理等几个步骤。

在这个实验中,我们用 Vitis 一个工具完成了以上所有任务,所有的数据处理都在 FPGA 侧完成加速,以保证最佳的实时性;ARM 在整个系统中负责任务管理,而不进行具体计算。视频输入输出的功能由 Vitis Platform 负责;视频前处理通过调用 Vitis Vision Library 实现;学习推理通过在 Vitis 中调用 DPU 实现。最终结果可以达到1080P60,单帧Latency。

Vitis Acceleration Lab

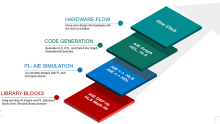

硬件加速设计流程

这个 Lab 通过三个小实验介绍了使用 Vitis 进行硬件加速设计的工作流程与常用工具。

第一个 Lab:

Vector Addition。

向量加法是硬件加速界的 Hello World。这个实验通过分别介绍使用图形界面的方法和使用命令行的方法,来完成一个向量加法设计的功能仿真。

第二个 Lab:

Wide Vector Addition。

这个实验在第一个实验的基础上,添加一系列优化性能的方法,比如增加向量加法器本身的位宽、独占 DDR 等方式,完成一个向量加法的硬件级仿真。这些优化方法都是日常设计中常用的方法。在本实验中,还特别指出了怎样使用 Vitis Analyzer 来观察加速器运行状态和性能的方法,它可以帮助我们分析设计的效果是否达到预期。

第三个 Lab:

使用 Vision Library 来进行图像处理。

Xilinx 提供了很多常用的硬件加速库 (Vitis_Libraries) 供用户使用。本实验介绍了使用他们的基本方法。用户可以使用 Vision 库中的 resize 和 blur 功能,将使用软件计算比较耗时的部分转移到逻辑中做加速。

Vitis Acceleration Lab

代码优化

使用 Vitis 进行加速设计,既牵涉到加速器(Kernel)的开发,又涉及到主机(Host)的开发。两者都对最终运行效率有影响。除了基础实验中的简介流程,如果要得到最优性能,还需要在编程语言层面对编译器以及最终的电路实现有所理解。这组实验就介绍了几个可能影响性能的几个方面。

第一个实验讨论了关于申请内存的不同方法导致的性能差别。

第二个实验提供了一种方法,来尽可能保证每个加速器Kernel都有尽可能高的利用率,而不是在等待。

第三个实验介绍了怎样使用 Streaming 接口,在两个 Kernel 之前传输数据,保证最有效率的数据传递。

*Github上的Link资源正在制作中,敬请期待。

如有技术问题,欢迎在赛灵思中文社区论坛交流:https://forums.xilinx.com/cn

来源:XILINX技术社区