本文主要介绍FPGA选型时的速度等级这个参数。

大家在进行FPGA选型时都会看见一个参数:Speed Grade,这就是芯片的速度等级。

芯片的速度等级不是专门设计出来的,而是在芯片生产出来之后,实际测试标定出来的;速度快的芯片在总产量中的比率低,价格也就相应地高。

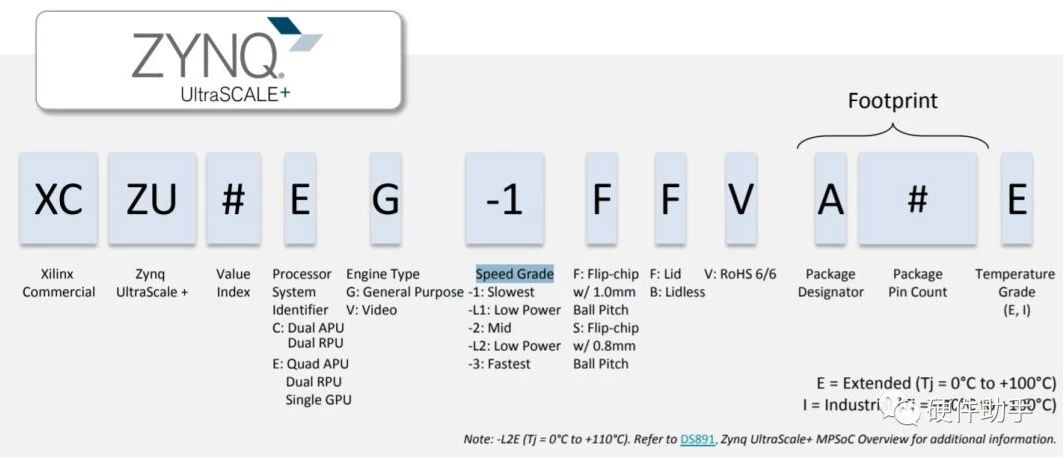

这是Xilinx FPGA的排序方法是“序号越高,速度等级也越高”。

芯片的速度等级决定于芯片内部的门延时和线延时,这两个因素又取决于晶体管的长度L和容值C,这两个数值的差异最终取决于芯片的生产工艺。

在芯片生产过程中,有一个阶段叫做speed binning。就是采用一定的方法、按照一组标准对生产出来的芯片进行筛选和分类,进而划分不同的速度等级。

速度等级的标定不仅仅取决于芯片本身的品质,还与芯片的市场定位有很大关系,返修概率和成本也是因素之一。

芯片的等级可以在测试后加以具体调整和改善,在存储器芯片的生产中这一技术应用很广泛。

芯片生产的过程是充满各种变数的,生产过程可以得到控制,但是控制不可能精确到一个分子、一个原子,产品质量只能是一个统计目标。同一个wafer上的芯片会有差异,即使是同一芯片的不同部分也是有差异的。速度等级是一个统计数字,反映了一批芯片的某些共同特性,不代表个别芯片的质量。而且由于某些芯片的测试是抽样进行的,也不排除个别芯片的个别性能会低于标定的速度等级。不过,FPGA的测试是极其严格的,很可能我们拿到手的芯片个个都经过了详尽的测试。这也是FPGA芯片价格高于普通芯片的原因。

同一等级的芯片中的绝大多数,其性能应该高于该速度等级的划分标准。这也是为什么在FPGA设计中,有少许时序分析违规的设计下载到芯片中仍然能够正常运行的原因(时序分析采用的模型参数是芯片的统计参数,是最保守也是最安全的)。不过,由于同一等级的芯片仍然存在性能差异,存在时序违规但是单次测试成功的FPGA设计不能确保在量产时不在个别芯片上出现问题(出了问题就要返修或现场调查,成本一下子就上去了)。所以,还是要把时序收敛了才能放心量产,这就是工程标准对产品质量的保证。

现实世界是模拟的,不是数字的。在考察现实问题时,数字工程师和软件工程师应该抛弃“一是一、〇是〇”的观念,用连续的眼光看待这个连续变化的真实世界。

芯片生产过程中的不确定性导致了芯片的性能差异,这一差异影响了芯片的价格,价格和性能的折中又影响了FPGA设计工程师在器件选型、设计方法上的决策,生产的产品的性价比决定了产品的销售,产品的销量又决定了芯片的采购量,采购量又影响了芯片的采购价格...。

器件速度等级的选型,一个基本原则是:在满足应用需求的情况下,尽量选用速度等级低的器件,主要有如下好处:

由于传输线效应,速度等级高的器件更容易产生信号反射,设计要在信号的完整性上花更多的精力;

速度等级高的器件一般用得比较少,价格经常会成倍增加,而且高速器件供货渠道一般比较少,器件订货周期一般比较长,会延长产品的研发周期,降低产品上市率。

来源:硬件助手