“FPGA 在金融科技领域的应用历史悠久,但直到赛灵思 Vivado HLS 和 Alveo 加速卡的出现,终于让金融行业可以尽情地享受自适应计算加速所带来的‘极速、稳定、低延时’的完美体验。”在本月初的XDF-亚洲站上,中泰证券 CIO 程龙由衷指出。是的,金融科技开发已经迎来了新时代!

本届XDF-亚洲站上,基于赛灵思FPGA众多合作伙伴展示了Fintech(金融科技)的应用产品和解决方案。比如,Meridian Technologies基于ALVEO平台打造了上证行情极速解码系统;中科驭数利用FPGA和相关软件系统,设计实现了金融交易中的风控规则处理、金融协议解析和网络协议解析的一体化加速解决方案。此外,高效能服务器和存储技术国家重点实验室受邀做主题报告,围绕“助力智慧金融加速FPGA元年”主题,对研究成果向国内外的与会代表进行展示交流......

在赛灵思和和生态合作伙伴的推动下下,金融科技正迎来新篇章!

什么是Fintech金融科技?

事实上Fintech 是一个合成词,为 Financial technology 的缩写,直译过来 Fintech 的中文就是“金融科技”。其本质是指用来提高金融服务效率的科技手段,比如大数据、云计算、智能投顾、区块链、移动支付等现代技术,它们的出现大大提高了传统金融服务的速度和效率。

在大数据和人工智能盛行的今天,金融科技领域数据日益密集和敏感。对于金融机构而言,现场可编程门阵列 (FPGA) 是一种理想的技术,能够满足其超大规模的计算需求,降低衍生品投资组合和风险管理相关的高运营成本,因而被广泛应用在高频交易、风险分析等金融场景中。

FPGA在Fintech领域之所以受青睐,归功于其内部拥有丰富且灵活的逻辑与计算单元,可以支持定制低延时、高吞吐率的设计,从而一方面能够为Fintech提供远超软件实现的性能优势,另一方面还可以为金融企业提供可以跟随最新科技演进而发展的灵活应变成本优势。

FPGA 技术的优势

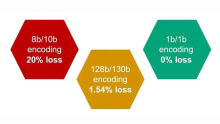

• 与 GPU 模式相比,显著提升性能

• 确定性时延有助于提供一致性能

• 通过降低能耗,大幅降低与 CPU 和 GPU 有关的运营成本

案例展示

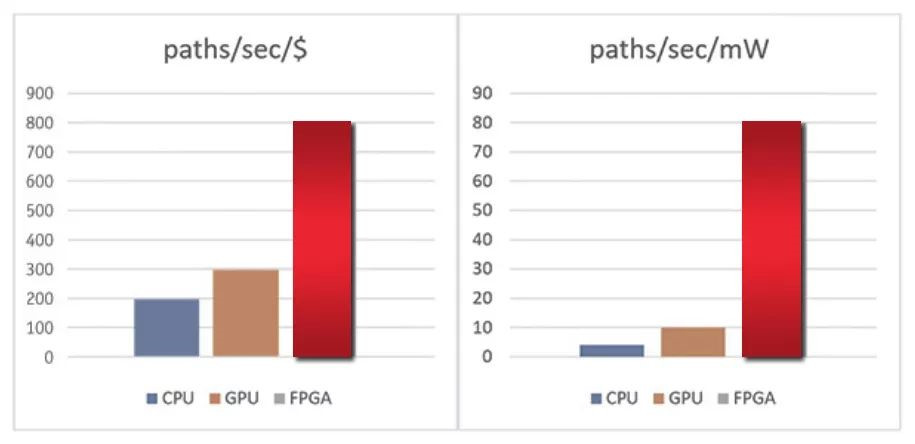

采用蒙特卡洛模拟为股票挂钩结构化票据估值

模型主要特性

• 关联性赫斯顿 (Heston) 随机波动过程

• 通过连续性校正实现连续障碍监控

• 可选赎回

主要性能指标

- 每货币单位 (USD) 性能(路径数/秒)与每功耗单位 (mW) 性能

- 基于建议客户价格(RCP,以美元计价)

- CPU/GPU 功耗估算基于热设计功耗 (TDP) 的 80%

- FPGA 功耗估算基于布局布线后分析。

- CPU:Intel Xeon E5-2673 v4 (Intel Parallel Studio XE 2019)

- GPU:Nvidia V100 16GB PCIe (CUDA 10.1)

- FPGA:赛灵思 Alveo U50

- 操作系统:Ubuntu 16.04 LTS

Fintech开发迎新时代

软件工具Vivado HLS+自适应加速器卡Alveo

不过FPGA此前也一直被一些用户诟病使用“门槛”太高。原因在于,开发人员在采用FPGA产品时必须在技能上“软硬兼备”,既要软件还要会硬件。而且,写RTL代码和验证耗时耗力,在分秒必争,时间就是金钱的金融行业,开发者们面对FPGA 是爱恨交织,如那句歌词“想说爱你并不是很容易的事,那需要太多的勇气”。

正当开发者们苦苦纠结时,赛灵思两款划时代“利器”横空出世,将FPGA的开发难度“从金字塔尖拉到了金字塔底”,大幅降低了软件和硬件程序员开发FPGA应用的难度。从此,软硬件程序员开发FPGA应用可以信手拈来,再也不必受那分配管脚、手写RTL的苦。那么,这两件利器是什么呢?它们分别是:赛灵思Vivado HLS高层次综合工具和Alveo自适应计算加速器板卡。

高层次综合工具:Vivado HLS

Vivado HLS是一款能将C/C++代码转化为RTL代码的自动转化工具,其自带验证、封装等功能。开发者只需将顶层C/C++程序配合C/C++验证代码,通过软件验证,而后就可以用Vivado HLS将其转化为RTL代码。其次,Vivado HLS可以利用原有C/C++验证代码协同生成RTL代码,进行仿真并验证功能正确性。最后,Vivado HLS支持一键封装并生成IP,供Vivado®工具或Vitis开发环境使用。

这么简单?性能从何而来? 那就是Vivado HLS设计套件强大的性能:它能利用指令流水线(pipeline)、任务级流水(dataflow)和操作展开(unroll)功能,实现所有操作在时间轴上片刻不停地运转,而这些只需轻点鼠标,插入几条指令(pragma)即可实现。

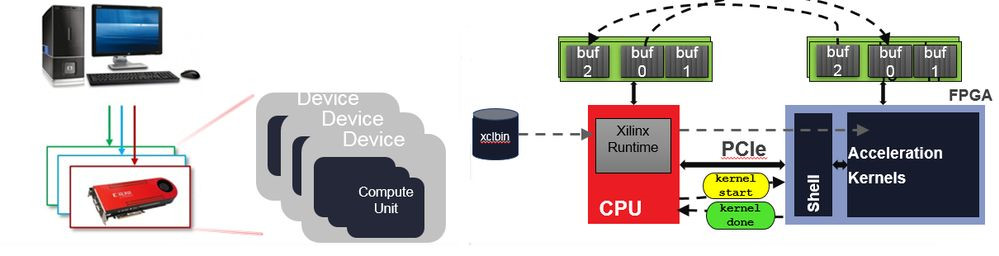

自适应加速器卡:Alveo

我们再来看看Alveo板卡能给我们带来什么,它又强大在哪里。Alveo赛灵思为适应灵活应变、万物智能的新时代而推出的自适应加速器卡系列,它配有标准PCIE、网口(可达100G),还提供了整套部署及开发的软件堆栈,使开发者可以通过安装软件包轻松部署。同时,Alveo还配备了壳(shell),可以将PCIE、DMA等功能固化,开发者只需开发最具创新性的、专有的内核(kernel),使用标准的AXI-4接口,即可自动将内核与壳相连,生成完整的平台硬件。在软件层面,开发者只需调用Open CL或赛灵思提供的API,即可完成所有板卡调度、数据传输等任务。

Alveo自适应加速器卡的适用领域非常广泛,如数据库、机器学习、图像处理、压缩及解压缩、加密及解密、金融计算等,每个领域里Alveo都有着出色的加速应用。尽管Alveo的加速倍数根据应用的不同而有所不同,但是在一些适合并行的领域,往往可以提供更加惊人的表现,例如,在不损失精度的情况下,欧式期权定价可以比CPU快3,000倍以上。下图展示的就是Alveo在赛灵思及合作伙伴的多个领域的应用。

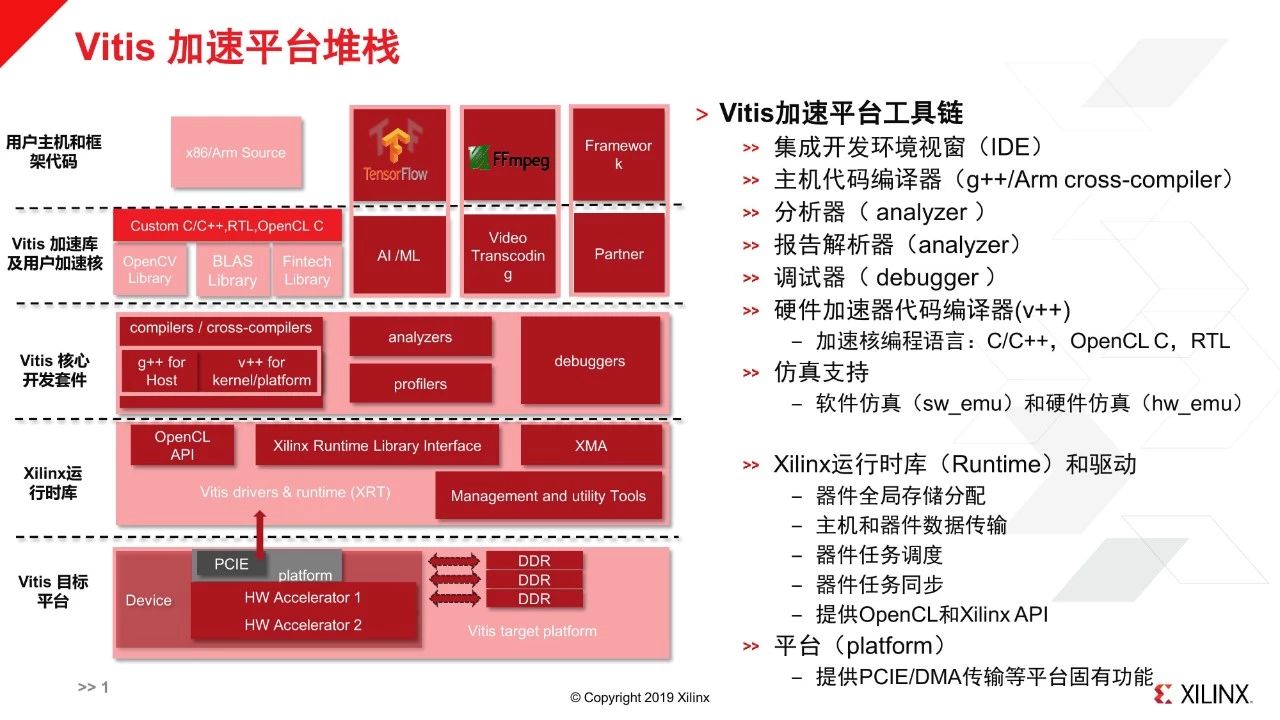

开启Fintech开发新时代

软件拥有Vitis开发环境及调度库(runtime),硬件拥有Alveo自适应加速器卡和壳,设计上拥有Vivado HLS来开发定制化需求,加之丰富的案例和开源的实际应用,赛灵思为金融科技领域的开发者开启了一个轻松上手FPGA加速的开发新时代。

此外,赛灵思还收购了在全球金融机构赫赫有名的Solarflare公司,大大增强赛灵思在Fintech领域的实力,可以为客户提供低延时网卡和各种金融领域定制化应用。

与此同时,赛灵思还打造了全方位的Fintech生态系统。公司不仅为开发者提供了一系列工具,还提供了多种IP,甚至一些金融领域的特殊需求,如TOE(TCP/UDP Offload Engine),也有相应开源HLS帮助实现。在HLS基础库中,涵盖了定点库、数学函数库、线性代数库等,而在更高层,赛灵思还实现了模块级及软件API级的HLS开源,如矩阵运算库等。

除自身提供全套工具及开源库,赛灵思还与独立软件提供商(ISV)共同提供各种解决方案。这些ISV往往拥有自己独特的解决方案,而赛灵思要做的就是对他们的应用提供支持,以满足众多领域的需求。

在Fintech领域,这些应用包含:

• 一键下单(Tic To Trade);

• 交易权风控;

• 解包及发包;

• 期权定价等等。

最快甚至可以实现纳秒(ns)级的下单。在中国市场,从以太网收到交易所包到解包再到计算完成,整个流程可以在百毫微秒级实现。

总之,赛灵思Vivado HLS和Alveo的到来,Fintech开发迎来了一个FPGA加速的新时代。开发人员无需在硬件平台搭建与基础支持工具上投入过多精力,而只需专注于自己的特长领域,借助Vivado HLS快速在Alveo™加速器卡实现定制化应用,不断突破低延时、高吞吐率的极限。

来源:一点灵 Xi