作者:付汉杰,hankf@xilinx.com,文章转载自:博客园

Xilinx的开发板ZCU102支持休眠到内存(suspend-to-ram)。休眠到内存时,DDR进入自刷新,MPSoC被关电,完全不耗电。唤醒时,MPSoC根据外部输入信号判断出不是上电启动而是休眠,就从DDR读出系统状态,恢复系统。

MPSoC启动时,它的DDR控制器会驱动DDR的复位信号,有可能破坏DDR里的数据。为了避免这种情况,需要对DDR复位信号进行特殊设计。

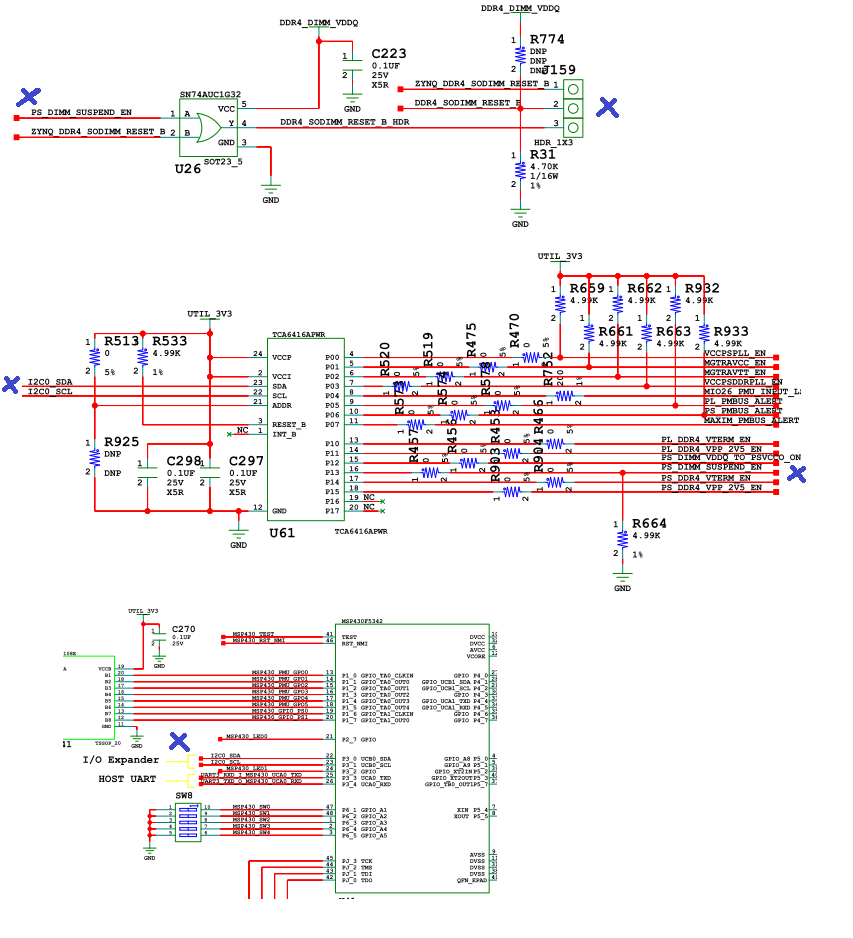

在开发板ZCU102上,DDR复位信号由外部单片机MSP430和MPSoC联合控制,两个的控制信号经过SN74AUC1G32(2输入或)再连接到DDR内存条。MSP430的信号有下拉,缺省情况下只由MPSoC控制DDR复位信号。如果需要支持休眠到内存(suspend-to-ram),MSP430控制I2C芯片输出高,相当于屏蔽了DDR复位功能,使DDR内存条一直不被复位。

下面是相关的原理图。DDR4_SODIMM_RESET_B信号连接到DDR内存条。ZYNQ_DDR4_SODIMM_RESET_B是从MPSoC来的信号。PS_DIMM_SUSPEND_EN来自于MSP430控制的I2C芯片TCA6416APWR。