示波器的需求急速成长,同时新的研究和测试应用也需要更多、更快、更复杂的讯号。 这会需要更具智能功能的测试设备,才能准确侦测特定的讯号状况并避免空滞时间、在采集期间处理资料以缩短测试时间,或者是快速产生反馈讯号以控制待测装置 (DUT)。 过去十年来,强大 PC 软件和模块化 I/O 的紧密整合,不仅缩短了测试时间,同时也降低了整体测试成本。 软件设计仪器属于全新的产品类别,能够把用户算法扩充至仪器本身,藉此把这个概念提升到新的境界。 这样一来即可设计高度优化的测量系统,进一步实时分析每个样本,避免耗时的后续处理作业。 最后不但能够缩短测试时间,还可以更快地探索科学与研究应用。

内容

什么是「软件设计的示波器」?

透过软件来设计示波器 FPGA 的程序

示波器搭配用户可定义的 FPGA 所提供的测试优势

示波器搭配用户可定义的 FPGA 所提供的科学应用优势

结论

什么是「软件设计的示波器」?

示波器等仪器通常采用多个软件层,有些是用户较容易存取的软件,有些则否。 PC 上的软件可控制测试系统的整体运作,仪器驱动程序可提供示波器的通讯功能,嵌入仪器本身的软件则控制了数据采集和提供给用户的方式。 传统仪器会通过仪器驱动程序提供固定的测量功能;模块化仪器则运用了开放式的 PC 软件和现代 CPU 的处理性能,可以在 PC (而非仪器内部) 执行讯号分析。 这样一来,用户即可迅速定制针对采集到的数据执行数据分析的方式,以此满足个人的特殊需求,例如缩短测试时间或提高测量分辨率。

软件设计仪器进一步运用这个概念,可供用户修改或甚至彻底替换仪器 FPGA 上所执行的嵌入式软件。 因为每个采集到的数据点都可以实时在仪器 FPGA 上完成分析,所以用户可实现定制的实时分析和复杂的触发,并且避免空滞时间 (错失讯号)。 简而言之,软件设计仪器能够让用户存取所有的软件层,从主机 PC 到仪器数据转换器的针脚全都包含在内,进一步实现定制的修改内容,满足特定的应用需求。

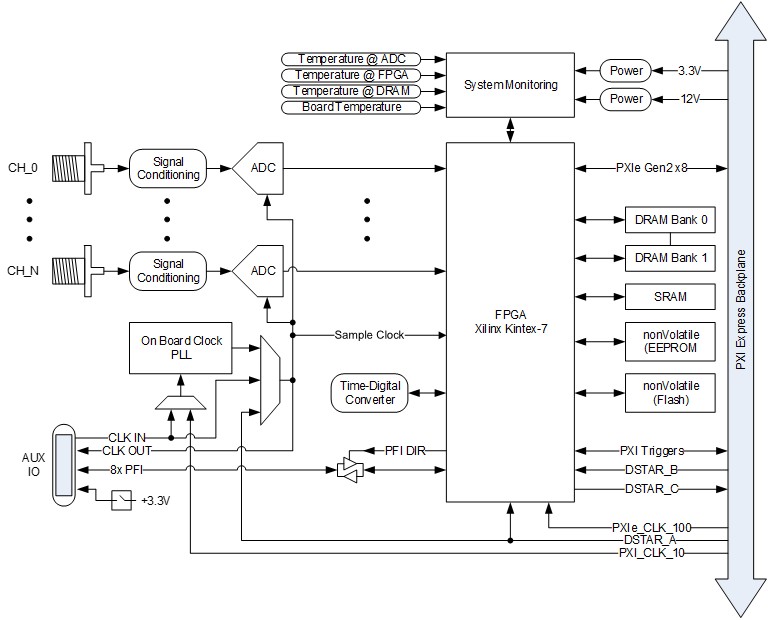

全新 NI PXIe-5171R 示波器是一种软件设计仪器,配备 8 个输入通道、300 MHz 模拟带宽、250 MS/s 取样率、14 位分辨率,以及用户可设定的 Xilinx Kintex-7 FPGA。

图 1: 用户可定义的 FPGA 作为软件设计仪器 (PXIe-5171R 示波器) 程序框图的核心组件。

透过软件来设计示波器 FPGA 的程序

LabVIEW FPGA Module 能够把 LabVIEW 系统设计软件扩充至 NI 可重设 I/O (RIO) 硬件上的 FPGA;而这类硬件则包含了 PXIe-5171R 和 PXIe-5624R 示波器、数字序列仪器、RF 向量讯号分析器,以及在 2012 年发表「软件设计仪器」概念的向量讯号收发器 (VST)。

LabVIEW 本身即具有平行机制,而且数据流概念和 FPGA 的数据流也很像,因此非常适合用来设计 FPGA 程序。 LabVIEW 能够抽象化系统内不同操作部分所执行的处理和数据迁移作业 (例如仪器内的 FPGA 和 PC 内的微处理器),因此工程师和科学家不需要 Verilog 或 VHDL 之类的 FPGA 程序设计、运算架构或数据串流等方面的深入知识,即可充分发挥软件设计仪器的性能。

LabVIEW 本身即具有平行机制,而且数据流概念和 FPGA 的数据流也很像,因此非常适合用来设计 FPGA 程序。 LabVIEW 能够抽象化系统内不同操作部分所执行的处理和数据迁移作业 (例如仪器内的 FPGA 和 PC 内的微处理器),因此工程师和科学家不需要 Verilog 或 VHDL 之类的 FPGA 程序设计、运算架构或数据串流等方面的深入知识,即可充分发挥软件设计仪器的性能。

图 2 为软件设计仪器的软件架构 (目前以示波器为例)。 此架构包含了实现 FPGA 的例程,可用于实际采集和实时处理,以及主机 PC 上对应的软件模块,能够和 FPGA 上的对应部分互动,进一步设定/控制测量作业、处理 PXI Express 总线的数据传输,并且呈现数据给用户。

图 2: 就软件设计仪器的架构而言,主 VI 会和 FPGA 上的对应部分互动,以此设定硬件并执行测量。

主机 PC 的组件和仪器驱动程序很类似,FPGA 程序代码则是和传统的示波器硬件比较像。 不同于传统示波器,这些组件可用来建置定制示波器 IP,同时也因为开放式特性,可供用户根据特定需求而修改或扩充

示波器搭配用户可定义的 FPGA 所提供的测试优势

测试应用的终极目标之一就是缩短整体的测试时间。 时间通常是提高大量制造成本的主要原因之一,弹性和可重复使用率对高度混合或高度维护测试系统而言则是非常重要。 下列三个范例说明了示波器搭配用户可定义的 FPGA 如何节省时间和成本。

在线处理和 DUT 控制,加快测量速度

许多应用必须透过通过数字滤波、信道化、快速傅立叶变换 (FFT) 或解调等措施来处理所采集的数据。 虽然现代的多核心 CPU 可提供无与伦比的处理性能给桌面计算机,但通常无法实时处理多核心示波器所产生的数据,所以也没办法快速执行测量作业。 结果就是 CPU 会成为测试速度的关键。 有了 FPGA 和固有的平行机制,即可轻松持续执行复杂的分析作业,例如实时并行计算多个通道的功率频谱。

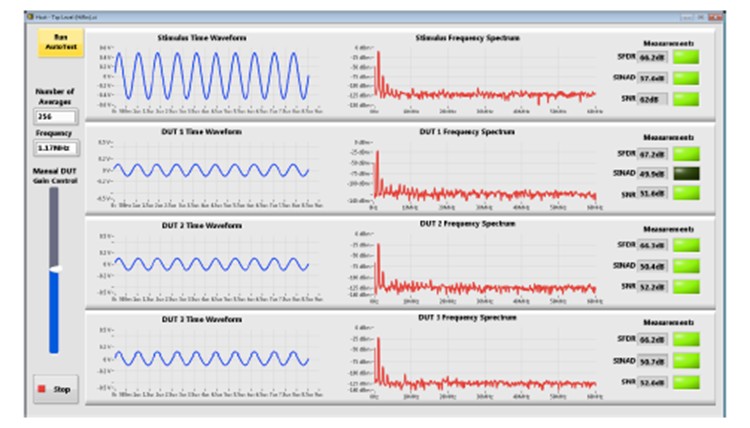

图 3 为用户可定义的 FPGA 如何用于 PXIe-5171R 示波器,只要一次就能采集并测量一个 DUT (RF 切换器) 内多个通道的串音。 4 个示波器通道会平行采集 DUT 所有 4 个信道的输出讯号,计算所有 4 个通道的功率频谱,并且针对违反情况执行屏蔽测试。

图 3: PXIe-5171R 示波器搭配用户可定义的 FPGA,可执行平行的频谱测量,进而缩短测试时间。

另一个在线处理的例子就是透过 DUT 关闭循环。 示波器本身可控制 DUT 并缩短测试时间,而非由主机 PC 来控制测试系统内的 DUT 和示波器 (这样会带来通讯时间的运作成本)。 示波器的 I/O 通道可做为分离式 I/O 使用,也可当作 SPI 之类的序列总线,以便和 DUT 通讯。

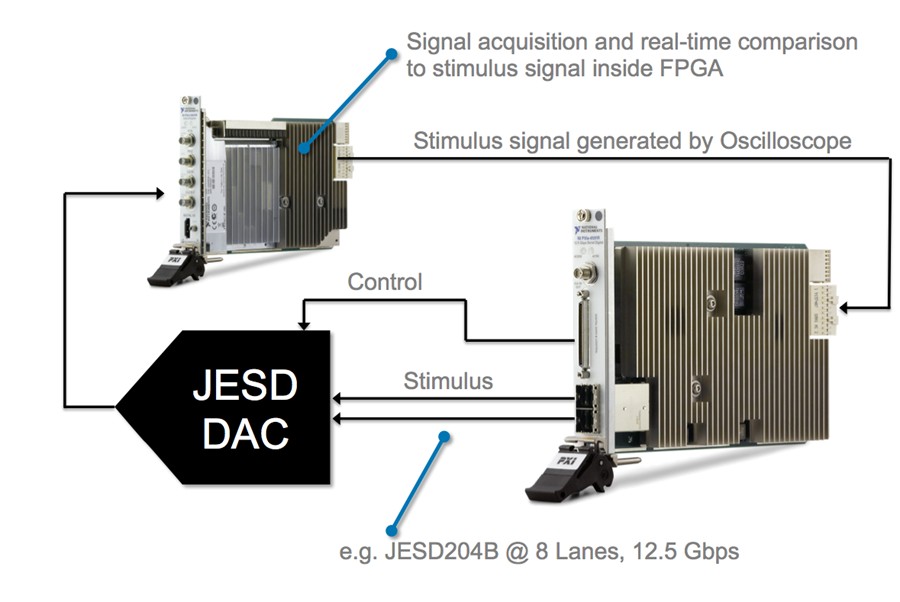

图 4: 测试高速数字转模拟转换器 (DAC) 的刺激反应系统。

透过点对点数据流技术,示波器即可结合其他仪器,打造出闭循环测试系统 (图 4)。 示波器内部的 FPGA 会产生测试讯号,并且传送至数字序列仪器,以此驱动 DAC 输入。 示波器会采集频谱,并且自动比较采集到的讯号和预期的讯号 (也就是之前产生的讯号)。

透过自定义触发和协议解碼缩短测试时间

对许多测量作业而言,侦测特定的讯号状况以启动采集作业是相当重要的功能。 传统的示波器可以精确采集一些触发状况 (例如某个讯号超过临界值),但因为仪器处理已采集的资料而带来的空滞时间,所以无法每次都侦测到更复杂的事件,例如脉宽。

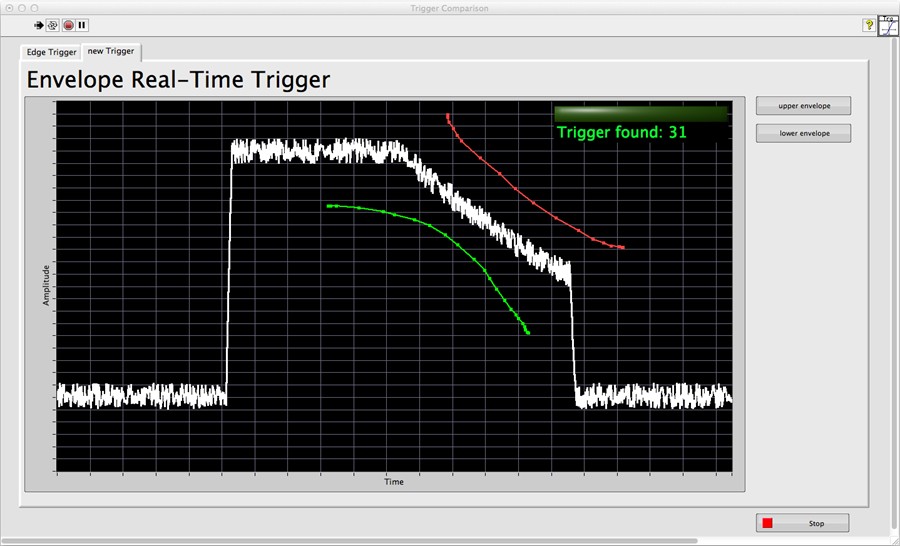

用户可设定的 FPGA 可做为讯号链不可或缺的一部分,并且针对用户定义的状况实时分析每个讯号。 这样一来即可以精确稳定的方式,侦测简易 (准位和磁滞) 和复杂触发,例如讯号抖动或脉宽、特定上升时间,或甚至特定的讯号形状。 图 5 的触发状况运用了一个讯号封包,以此触发采集作业。 诸如此类的触发情境可用于设计和测试项目,以便侦测单边缘触发器难以侦测到的异常行为。

图 5: 特定讯号形状引发的触发。 在此范例中,讯号必须介于红色和绿色曲线之间,才能够触发采集作业。

此外,也可以组合多个触发器,进而侦测复合状况,例如可以在不同通道上看到特定频谱内容的数字样式,或者是一连串的事件,通常称为 A-B 触发器。

有个相关功能就是可根据序列通讯接口上的特定数据字词或错误,侦测并触发采集作业。 有了用户可定义的 FPGA,即可测试讯号的完整性 (根据规格测试讯号的模拟波形),同时平行译码输入数据,以此验证数据内容。 这样一来,用户不但可以测试讯号,也能够建立可做为最终系统组件并快速制作原型的测试设定,有效运用单一仪器同时完成两项工作。

仿真旧设备以减缓产品汰换问题

军事或航天应用领域内许多维护测试系统都有使用寿命的需求,可延长至 10 年以上。 通常会根据特定的仪器特性而撰写测试程序代码 (无论是否刻意),因此很难在避免大幅变动的情况下替换仪器,而且重新认证测试程序代码也需要高额的成本。

用户可定义的 FPGA 可供程序设计,藉此修改仪器并仿真遭替换设备的行为,有助于避免上述问题。 运用 FPGA 逻辑即可轻松复制触发行为或时序组合等特性,此外只要透过数字方式实作所需的滤波器,甚至可以模拟更复杂的方面,例如示波器的滤波特性。

示波器搭配用户可定义的 FPGA 所提供的科学应用优势

就高能物理等科学应用而言,仪器的性能与弹性都是很重要的特色。 一般来说,这类应用大部分的讯号处理和控制作业都会采用模拟电子和相对较慢的 ADC,以此采集预先处理过的讯号。 现在,快速的高分辨率 ADC (14 位和 250 MS/s 以上) 可直接从传感器采集讯号样本。 只要仪器搭载用户可设定的 FPGA,即可在采集期间同时执行讯号处理作业,不必通过 PC 完成后续处理。 这样不但可以更快取得结果,也能够提高科学实验控制的弹性和效率。

有效实时反馈系统的在线处理

许多科学实验都必须仰赖控制系统,确保所有设定项目都维持在明确定义的状态。 举例来说,DIII-D Tokamak 等融合研究系统会透过 RF 功率来加热等离子体,这会需要测量复杂的 RF 反射系数,并且根据测量结果衍生出合适的控制参数。

使用粒子加速器和同步加速器时,必须持续监控粒子光束的轨迹,才能满足磁铁的正确控制输入需求。 示波器搭配用户可定义的 FPGA,提供了固有的快速平行处理性能,能够同时分析讯号和频域,以及极高速的控制循环,因此有助于解决 DIII-D Tokamak 等应用问题。 只要客制化 FPGA,即可监测重要的安全参数,以便在系统处于非理想状态时触发关机作业。

示波器可透过高速 PXI Express 总线,搭配输出模块以产生实验所需的控制讯号,或是以每个仪器超过 3 GB/s 的速度连续把数据串流至储存媒介。 用户可定义的 FPGA 还有另一个优点,那就是可以快速修改处理和控制算法。 可以把已编译过的位串流加载 FPGA,只要不到一秒的时间,即可改变示波器的行为。

实时事件侦测和数据减量,有助于加速探索

判断重点事件通常相当困难。 常见的作法就是等到实际数据采集作业结束之后,在后续处理期间寻找事件,不过这么做很花时间,而且必须储存大量的数据。

另外有一个更有效的方式,就是在采集期间决定要保留和舍弃的讯号,以此把数据量降到最低。 通常唯一的重点参数就是时戳和能量脉冲的计算结果,所以就储存观点而言,从仪器回传这些参数会更有效率,而且因为采集到的结果可轻松卸除至主机 PC,所以还可以延长测量时间。

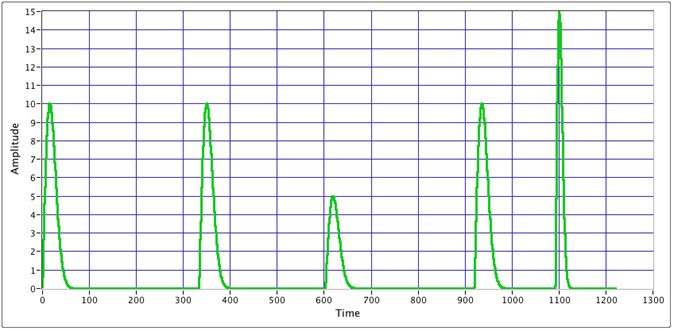

举例来说,飞行时间 (ToF) 应用会持续绘制粒子和能量。 如图 5 所示,较快的粒子位于左边 (飞行时间较短),较慢的粒子则位于右边。

图 5: 标准的 ToF 图和侦测到的脉冲,这些脉冲会传输至主机 PC。

测量系统的功用在于采集、时戳、测量能量脉冲,并且排除时间 (采集到的数据),中间完全没有脉冲,通常称为零点抑制。 透过 FPGA 即可轻松实作,因为可以实时计算每个样本。 如图 5 所示,侦测事件的一般架构可能会是脉冲 (例如某个临界值) 侦测器,接着是符合已侦测脉冲上参考脉冲 (例如高斯形状) 的算法,以便估计最大值。 侦测峰值和对应时戳并加以储存之后,即可舍弃所采集到的脉冲,也可传送至另一个缓冲区,以便进一步分析或于 PC 显示。

LabVIEW FPGA 提供一些工具给用户,能够把必要的讯号处理阶段实作于示波器上,藉此执行脉冲过滤和整形、计算出现次数并加上时戳、测量高度和上升时间、直接在仪器内重新建构基线,并且把压缩过的结果回传至 PC,以便提高研究人员的工作效率。

结论

传统示波器的原理是基于对信号进行快照的模式,然后在采样的后端将采到的信号对齐现实给客户波形测量。这样的方式会丢掉两次快照之间的数据,如果我们需要寻找一个信号中很小概率的细节,那传统仪器无疑会增加很多的测试时间。并且,基于FPGA将所有信号无缝采集,可以进行实时的信号处理,比如找出特定的信号波形,将其触发。与传统的示波器只能基于电平的触发方式不同,全新的可重配置示波器可帮助用户透过定制化触发,更快侦测事件,并且实时处理数据,直接透过仪器把数据转换成结果,进一步提高测量质量与速度。

文章来源:NI官网