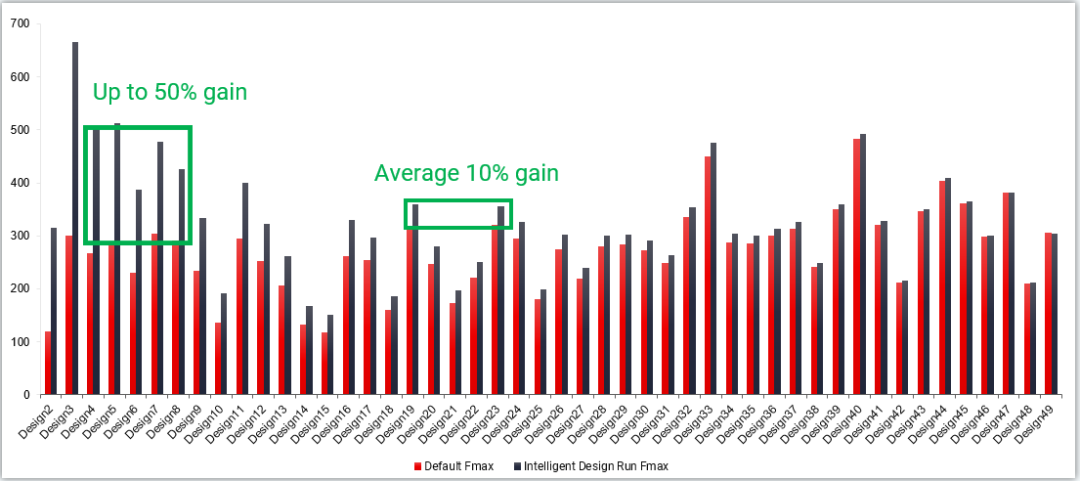

赛灵思近日宣布推出 Vivado® ML 版,这是业内首个基于机器学习(ML )优化算法以及先进的面向团队协作的设计流程打造的 FPGA EDA 工具套件,可以显著节省设计时间与成本,与目前的 Vivado HLx 版本相比,Vivado ML 版将复杂设计的编译时间缩短了 5 倍,同时还提供了突破性的平均达 10% 的结果质量( QoR )提升。

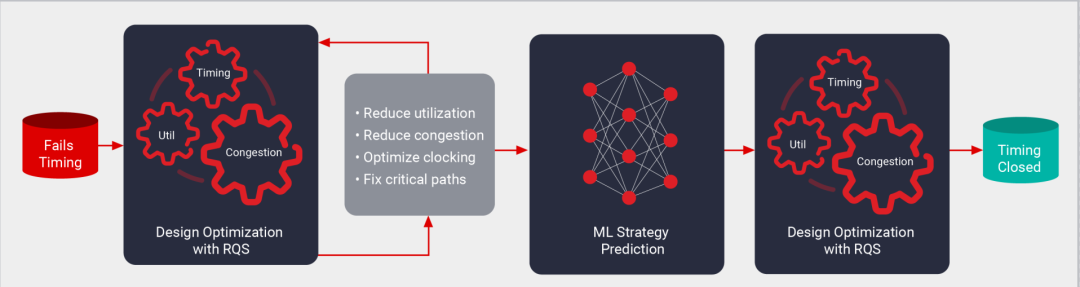

1. 基于 ML 的设计优化

加速设计收敛

2. 协同设计环境

提升生产力

3. 全新高级 DFX 功能

编译时间减少

功能介绍

1. 高层次设计

Vivado IP Integrator 可提供基于 Tcl、设计期正确的图形化设计开发流程。设计团队在接口层面上工作,能快速组装复杂系统,充分利用 Vitis™ HLS、Vitis Model Composer、Xilinx IP、联盟成员 IP 和自己的 IP。通过利用全新提升的 Vivado IPI 和 HLS 的完美组合,客户能将开发成本相对于采用 RTL 方式而言节约高达 15 倍。

2. 验证

应对当前复杂器件的验证挑战,需要在各种设计层面上应用大量工具及技术。Vivado® 设计套件在紧密结合的环境中提供这些工具和技术,从而可加速模块及芯片级设计的验证。

3. 实现

具有高级机器学习算法的 Vivado ML 设计套件提供了在运行时和性能方面具有显着优势的最佳实现工具。凭借用于综合、布局、布线和物理优化的一流编译工具以及 Xilinx 编译方法建议,设计者可以加快设计周期的实现阶段。

平台版本

Vivado 自助资源区

1. 视频库

Xilinx 致力于提升设计团队的生产力。通过观看一系列视频,可以帮助 Vivado 用户专注于缩短上市时间并实现设计成功。这些视频由 Vivado 开发及专家团队创建,可提供点播内容以及实用方法与技巧,只需动动手指头,就能轻松获取。

2. 培训课程

通过广泛的培训产品,充分利用您对 Xilinx Vivado ML 的投资。这些培训课程不仅面向不熟悉 FPGA 技术的工程师,还针对那些开发复杂连接功能、数字信号处理或嵌入式解决方案的有经验的工程师。

3. 开发者计划

免费加入我们的开发者计划,您将可以使用最新的 Xilinx 开发工具来加速您在各个领域的应用。通过参加 Xilinx 开发者活动,您可获取免费培训、折扣、演示和示例设计,以及开发者技术课程的精彩回放。您还可以与 Xilinx 社区分享您的技术见解和项目!

点击即可快速上手Vivado:https://china.xilinx.com/products/design-tools/vivado/vivado-ml.html