过去 20 年里,金融交易领域风起云涌:电子交易、算法、智能订单路由器持续演进;高频交易( HFT )兴起;为追求增强收益而寻找更复杂搜索策略。伴随这些趋势,金融交易指令也经历了重大变化。

交易时延角逐

无论使用或编写哪种算法,在降低时延、保持性能的同时提升算法精密度和准确度,总是不变的需求。毕竟,竞争永无休止。

最严峻的挑战之一是需要达到更低的时延,以确保用户算法能率先完成交易、实现最高利润和最小化延误。这场有关时延的角逐已经持续了数年时间。根据策略的不同,当进行跨时区交易时,简单的套利交易用时几纳秒,而高度复杂的策略则需要数十毫秒。无论使用或编写哪种算法,在降低时延、保持性能的同时提升算法精密度和准确度,总是不变的需求。毕竟,竞争永无休止。

在大多数行业中,新技术都是先由少数用户测试至极限,而后才逐渐流入更广泛的市场。以汽车为例:F1 赛车推动了汽车市场的锐意创新,超级跑车或高端电动汽车的制造商也是如此。这些利基推动汽车向未来发展,最终惠及主体汽车市场。

金融交易同样适用于这个规律。高频交易市场引领技术角逐,大力投资于尖端应用,同时承担新投资、新策略的预期风险。出于风险控制和追求增强受益的目的,众多大型银行也在投资尖端技术。

FPGA在未来交易中的地位

FPGA 可以提供高度可确定、高度并行且低时延的平台,用于实现交易策略(以及最近的 AI),确保系统交易速度最快。

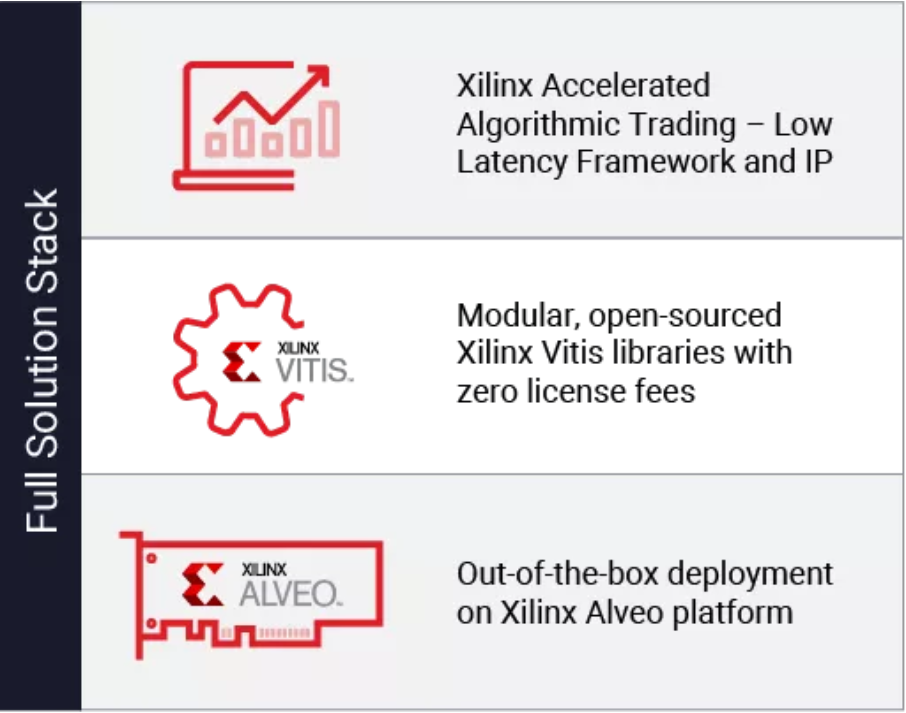

赛灵思在 36 年前发明了 FPGA,并始终居于 FPGA 技术的前沿。现在,赛灵思已经开发出了加速算法交易( AAT )平台,这个完整的参考架构有助于在大众市场普及 FPGA 技术。AAT 基于高层次综合(HLS,一种 C/C++ 风格的编程语言,旨在实现 FPGA 的广泛普及)构建,并由赛灵思 Alveo 加速器卡提供支持,Alveo 是业界首款企业级 FPGA 卡。赛灵思正以较低入门成本实现基于业界领先技术的新一代交易平台。AAT 的出现,将使得电子交易软件开发群体以前所未有的方式从 FPGA 中获益。

图:赛灵思 AAT 完整解决方案堆栈

交易普及化详解

赛灵思致力于让 FPGA 的优势惠及更广阔的软件开发者群体,AAT 就是例证。实现这一愿景的基石就是 Vitis 统一软件平台。

Vitis 为开发者提供了极大的灵活性,以便开发者在 FPGA 上无缝构建加速应用。作为 Vitis 统一软件环境的组成部分,赛灵思提供了 Vitis 库。这是一种使用 C、C++ 或 Python 编写的开源性能优化库,提供了开箱即用的加速功能,只需对现有应用进行最少修改,甚至零修改。

赛灵思 Vitis 库的集成为量化交易员提供了一个新平台,通过加速库(其中大量库可从 Python 运行)来加速其交易策略。

AAT 参考设计支持 CME 市场数据平台( MDP )的分价格档位行情( MBP )交易数据,还能用于为经纪商、交易所、市场数据厂商、卖方厂商以及自营交易员开发丰富多样的低时延算法交易应用,同时最大限度地避免高频交易损失。

展望未来

赛灵思还正助力用户为未来 AI 角逐做好准备。FPGA 可提供最快速的 AI 推断,同时具备高度并行的处理能力和较低的网络时延。随着 AI 成为交易策略的主要组成部分,赛灵思 Alveo 交易解决方案不必大量追加硬件,也无需定制硬件开发,就能轻松地扩展用于 AI。

视频:【用加速算法交易突破微秒交易壁垒】