作者:Max Cheng,Ingdan FPGA微信公众号

1. DisplayPort 1.4

DisplayPort是由视频电子标准协会(VESA)标准化的数字式视频接口标准,该接口免认证、免授权金,主要用于视频源与显示器等设备的连接。其中DP1.4可以支持的最高分辨率为8K@60fps。用FPGA实现最高的分辨率,则需要能够提供高达32.4Gb/s的带宽,也就是4lane,每lane达到8.1Gb/s。在Xilinx的DisplayPort 1.4 IP的文档中,提到支持的器件为Ultrascale/Ultrascale+/Versal系列,但很多的客户基于成本的考量希望能在7系列的器件中实现DP1.4。

2. 7系列FPGA GTX transceiver性能

如果只看GTX高速收发器支持的最小线速率0.5Gb/s和最大线速率12.5Gb/s,似乎是可以满足DP1.4的需求的,但为什么文档中支持的器件中没有7系列。仔细研究GTX高速收发器的性能参数会发现在8.0Gb/s~9.8Gb/s这个范围存在缺口,是无法支持到的。而DP 1.4需要支持的线速率8.1Gb/s,刚好在缺失的频率范围之中。如下表所示:

想要找到办法绕过这个缺陷,需要先了解Serdes的线速率是如何被确定的。

3. Serdes的线速率

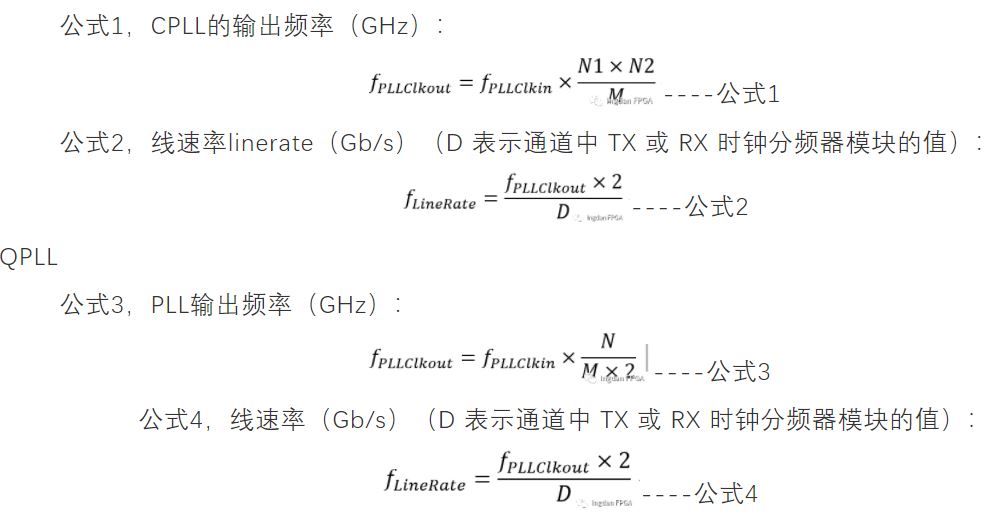

Channel PLL

综上,不论是使用CPLL还是QPLL,最终得到的线速率(LineRate)都是由PLL的输入时钟频率和分频系数确定的。

4. 解决方案

由此Xilinx的I/O专家Antony Gu提供了一种办法来解决线速率存在的缺陷。当我们在IP设置中选定了线速率和参考时钟之后,PLL内部的分频系数就被固定了下来,那么只需要调整外部输入时钟的实际频率来使得最终的线速率达到我们的需求。

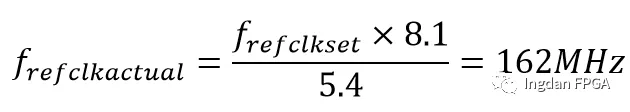

在DP1.4这个应用中,首先将线速率设置为5.4Gb/s,对应的参考时钟选择为108MHz。由于分频系数固定,想要得到8.1Gb/s的线速率,参考时钟的实际频率应该为:

5. 测试结果

Quad PLL:

QPLL能够支持更高速率,有着更好的性能。但是实际测试下来发现,使用这种办法QPLL始终不能lock,说明QPLL本身的特性决定了无法支持到8.1G。

CPLL:

虽然文档中标明CPLL最大只能支持到6.6Gb/s,但是实际测试下来发现,使用这种办法超频到8.1Gb/s,CPLL也可以稳定lock住。而且通过后续的测试,输出的DisplayPort 1.4信号可以正常点亮显示屏并稳定工作。

6. 参考文档

DS182,UG476。

如果你在Displayport接口方面有问题,欢迎联系:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn