作者: Simon Yang,文章来源: Comtech FPGA微信公众号

一.什么是IBERT

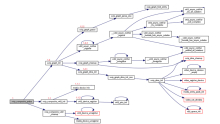

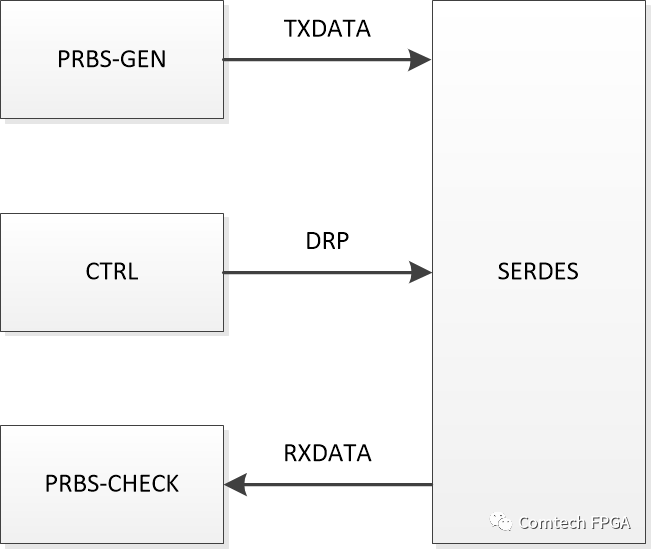

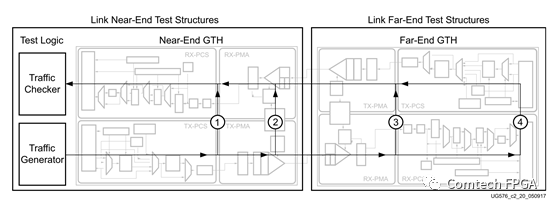

Integrated Bit Error RatioTester(IBERT)是Xilinx提供的用于测试transceiver的免费IP。IBERT的example design是一个集transceiver、logic、ILA、VIO、Pattern Generator and Checker、DRP于一体的参考设计,方便用户在不写代码的情况下测试当前硬件条件下transceiver能否工作在用户需要的线速率。IBERT的功能框图如下:

我们一直推荐用户在FPGA板卡硬件调试中使用IBERT测试transceiver,以便于排除电源、参考时钟和连接介质的问题,确保transceiver可以正常进行用户需要的高速串行设计调试。

关于IBERT IP GUI中的选项和配置项的具体解释,example design中的设计和使用方法,此文中不做阐述,用户可以参考Xilinx官方文档,如PG173、PG196、PG246等。此处强调和实际使用相关联的几点细节:

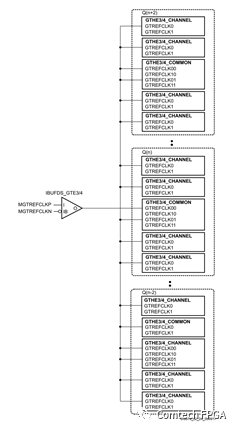

1. 在Refclk Selection中选择参考时钟时,Refclk的驱动能力范围请参考具体器件系列的transceiver文档,比如UG476描述的7系列器件参考时钟驱动的GTQuad为本Quad和上下相邻的两个Quad,共计3个GT Quad;比如UG576中描述的Ultrascale和Ultrascale+系列器件的参考时钟驱动的GT Quad为本Quad和上相邻的两个Quad、下相邻的两个Quad,共计5个Quad;

2. 在system clock的选项中,默认source是external,此处系统时钟用于IBERT里测量线速率、TX/USRCLK频率,以及DRP端口访问的时钟,建议使用一个独立于参考钟的FREE-RUNNING时钟,并正确填写其频率,这会影响运行IBERT时的显示;

3. IBERT的example design顶层代码可见,用户可以在设计中添加逻辑,比如光模块的使能信号控制等;

4. IBERT中的Eye Scan功能并不是只有在IBERT中可以用,我们在其他高速串行协议中如果使能了transceiver的Eye Scan功能,一样可以在链路工作的同时来扫描眼图,比如xapp1198中就提供了在PCIE链路工作情况下使用Eye Scan功能扫描眼图的参考设计;

5. IBERT中可配置的环回模式就是transceiver内部的环回模式,如下图所示:1所示的数据通路为Near-end PCS环回;2所示的通数据路为Near-end PMA环回;3所示的数据通路为Far-end PMA环回;4所示的数据通路为Far-end PCS环回;

二.PL IBERT测试中的常见问题

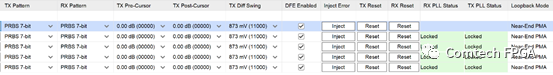

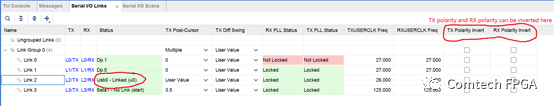

在我们把一个PL transceiver的IBERT测试工程bitstream通过JTAG下载到FPGA芯片中后,点击Auto detect links或者create links,就可以创建link链接,配置link中的一些参数,如pattern、loopbackmode、TX diff-swing、TX Pre-Emphasis等,如下图所示:

1. 其他的参数调整在哪里设置和修改?

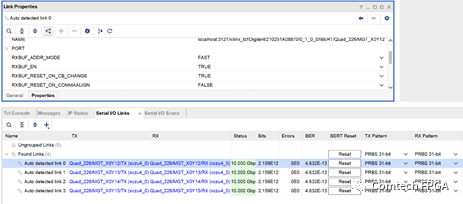

在我们点中某个link链路时,link properties---properties里面会有更详细的可以修改、配置和操作的寄存器、端口和属性,IBERT通过VIO和DRP的手段做好了这个界面;其中DRP、PORT、LOGIC可以展开折叠的部分以看到更多的寄存器、端口和属性。

2. Pattern建议使用哪种?

系统默认使用PRBS7,同时还提供了PRBS9、PRBS15、PRBS23、PRBS31、fast clock、slowclock的数据类型供选择,主要是他们的游程(Run Length)不同,因此Pattern Dependent Jitter(PDJ)不同。对于8B10B应用,其本身游程为5, 测试的时候用PRBS7就够了; 对于64B66B应用, 则要用PRBS31测试。

3. BER结果为多少可以说明链路测试OK?

这个没有官方说明,BER是一个概率论反推数值,BER一般的规范都在10-12,但这个测试的时间会比较长, 特别对于低速率的情况。所以如果在几分钟内看不到误码(error count =0), 就可以进行扫眼以判断眼图裕量。

4. 如果对端器件不是FPGA,而是其他芯片,如何使用IBERT测试含有完整传输链路的性能?

在对端芯片不是FPGA而是其他芯片时,如DSP、专用芯片、Switch等时,我们可以查阅对端芯片的资料,看对端芯片是否支持类似Far-end PMA的环回模式,如果支持,FPGA这一侧我们loopback mode设置为none、对端芯片设置为类似Far-end PMA的模式,就可以测试完整链路;如果对端芯片不支持这样的环回模式,我们可以想办法在硬件环境上做环回,如接插件、耦合电容等位置。

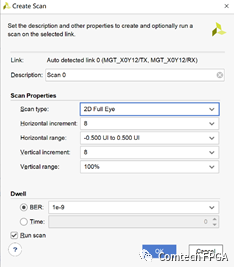

5. 2D Eye Scan和1D Bathtub如何使用?

在我们点中某个link链路时,右键选择Create Scan,会弹出如下画面,在scan type中可以选择2D Full Eye和1D Bathtub,此处选择的BER越低,扫描时间会越长。扫眼的目标BER应该是10-9,这样兼顾扫眼时间和可靠度。XILINX提供的眼图模板也都是基于这个误码率下的, 但同时把模板扩大, 使得在10-9下满足模板, 可适用于用满足10-12的误码率要求。

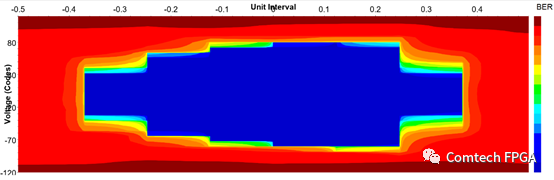

以10Gbps线速率、Near-end PMA loopback、BER为10-9为例,我扫描的一个眼图如下图所示:

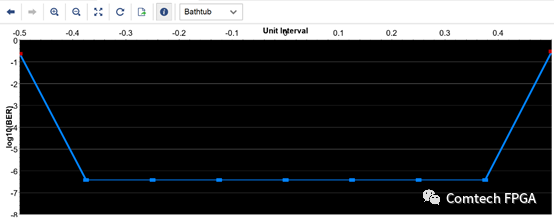

使用1D Bathtub的意义在于组合不同的参数,来扫描较优化的参数设置,下图是我以10Gbps线速率、Near-end PMA loopback、BER为10-5为例,扫描的bathtub曲线,因为数据链路信号插损很小,因此与链路信号完整性差的真实场景bathtub曲线在形状轮廓上会有差异。

6. 当遇到IBERT测试不通过,甚至于Near-end环回测试都不通过的时候怎么办?

首先需要用户测试测量的就是时钟质量和电源质量,关于时钟和电源的要求在每个系列的transceiver文档和data and switching文档上都有描述,以Kintex Ultrascale+为例,需要查阅的文档是UG576和DS922。

电源测试时一定要注意如下几点:1. 选择尽量靠近FPGA芯片的测试点;2. MGTAVCC、MGTAVTT、MGTVCCAUX、VCCINT四种电源都有可能影响到IBERT的测试结果,需要在下载程序后测试真实负载下的电源;3. 手册上要求的电源最大电压值和最小电压值,是需要考虑上纹波和噪声的影响,以Kintex Ultrascale+的MGTAVCC为例,手册上给出的最大值和最小值分别为0.927V和0.873V,假如纹波有20mV,实际测量MGTAVCC的平均值为0.88V,那么MGTAVCC的电压是可能低于最低电压值的要求的;4. 手册上要求的纹波10mV,实际设计中很难做到,常见的客户设计会控制在20mV左右,对于线速率10Gbps左右的应用没有影响。

三.ZU+ MPSoC中的PS IBERT GTR

在ZYNQ Ultrascale+ MPSoC中PS侧集成了GTR,可以配置为PCIE2.0、USB3.0、Displayport TX、SATA或者GEM Ethernet,PSGTR也可以使用IBERT来进行测试,但是不需要使用PL的IBERT IP,具体操作流程本文不做详细描述,请参考UG936文档中的Lab10。

此处仅强调PS IBERT GTR和PL IBERT的区别之处:

1. PS IBERT GTR在测试时不需要下载bitstream文件,只需要配置好PS GTR,并使用对应的FSBL文件来进行加载,就可以create links;

2. PS IBERT GTR比PL IBERT减少了几个功能:BER、patterngenerator和pattern checker、参数配置和调整;

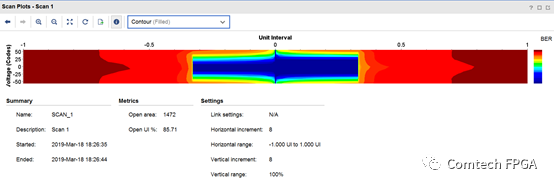

3. PS IBERT GTR同样具备Eye Scan和Bathtub Scan功能,我在一块板卡上插入USB3.0的U盘,设置BER为10-9,测试扫描结果如下图所示:

特别感谢Xilinx专家Antony Gu对本文初稿的指正和修改建议。

如果您在transceiver方面和IBERT测试方面有问题,欢迎联系:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn