# Implementing SMPTE SDI Interfaces with Zynq-7000 AP SoC GTX Transceivers

Author: John Snow

# Summary

The Society of Motion Picture and Television Engineers (SMPTE) serial digital interface (SDI) family of standards is widely used in professional broadcast video equipment. These interfaces are used in broadcast studios and video production centers to carry uncompressed digital video, along with embedded ancillary data such as multiple audio channels.

The Xilinx® SMPTE SD/HD/3G-SDI LogiCORE™ IP is a generic SDI receive/transmit datapath that does not have any device-specific control functions. This application note provides a module containing control logic to couple the SMPTE SDI LogiCORE IP with the Zynq®-7000 All Programmable SoC GTX transceivers to form a complete SDI interface. This application note also provides several example SD/HD/3G-SDI designs that run on the Xilinx Zynq-7000 AP SoC ZC706 evaluation board.

Terms used in this document are explained in the Glossary, page 53. Titles of SMPTE reports and standards are listed in References, page 56, and referred to by SMPTE document number in text.

# Introduction

The Xilinx SMPTE SD/HD/3G-SDI LogiCORE IP (called the *SDI core* in the rest of this document) can be connected to a Zynq-7000 SoC GTX transceiver to implement an SDI interface capable of supporting the SMPTE SD-SDI, HD-SDI, and 3G-SDI standards. The SDI core and GTX transceiver must be supplemented with some additional logic to connect them together to implement a fully functional SDI interface. This application note describes this additional control and interface logic and provides the necessary control and interface modules in both Verilog and VHDL source code.

The primary functions of the device-specific control logic are:

- Reset logic for the GTX transceiver

- Dynamic switching of the GTX RX and TX serial clock dividers to support the three SDI standards

- Dynamic TX reference clock switching to support the two different bit rates in each of the HD-SDI and 3G-SDI standards:

- HD-SDI mode: 1.485 Gb/s and 1.485/1.001 Gb/s

- 3G-SDI mode: 2.97 Gb/s and 2.97/1.001 Gb/s

- Data recovery unit for recovering data in SD-SDI mode

- RX bit rate detection used to determine if the RX is receiving a 1/1 or 1/1.001 bit rate signal

Also supplied with this application note is a wrapper file that contains an instance of the control module for the GTX transceiver and an instance of the SMPTE SDI core with the necessary connections between them. This file simplifies the process of creating an SDI interface.

The following terms are used in this document:

The SDI core refers to the SMPTE SD/HD/3G-SDI core generated by the CORE Generator™ tool or the Vivado™ IP catalog.

© Copyright 2013 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Vivado, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

- The *control module* is a module that implements the various device-specific functions required when using the GTX transceiver to implement an SDI interface using the SMPTE SDI core. The control module is supplied in source code form with this application note.

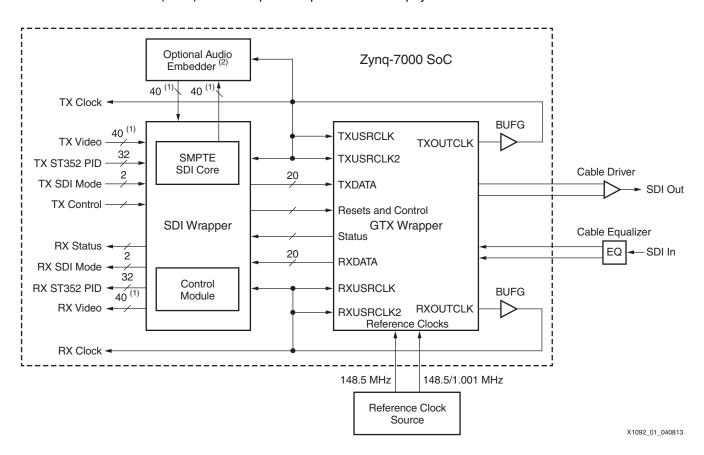

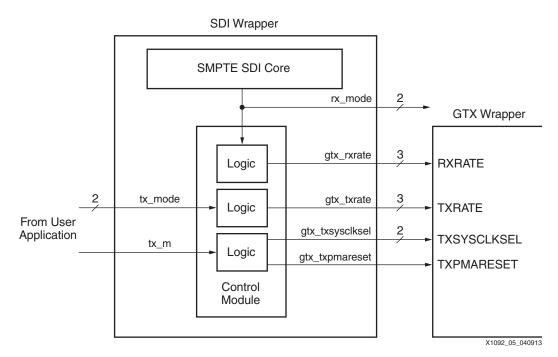

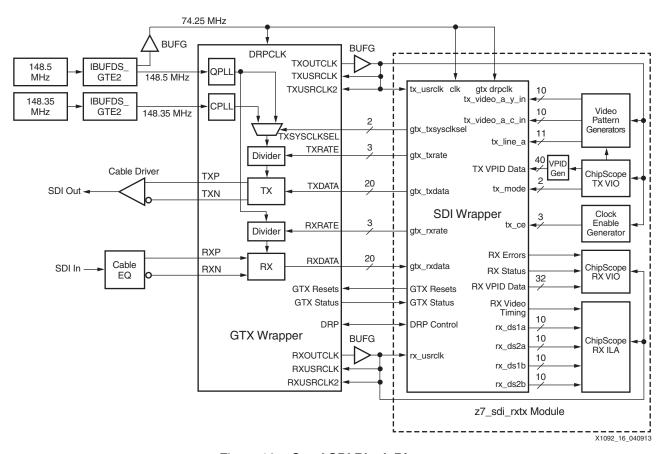

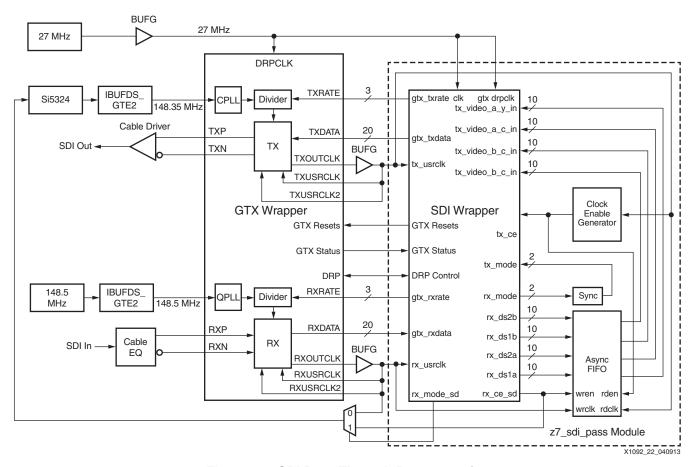

- The SDI wrapper is a wrapper module that instances and interconnects the SMPTE SDI core and the control module. The SDI wrapper is supplied in source code form with this application note. Figure 1 is a simplified block diagram of how the various pieces fit together to form an SDI interface.

- The *GTX wrapper* is a wrapper file for GTX transceivers generated by the 7 Series FPGAs Transceivers Wizard that is available in the CORE Generator and IP Catalog tools.

The SDI wrapper includes one instance of a control module and one instance of an SDI core. The SDI core includes both an SDI RX and an SDI TX datapath. The wrapper module is usually connected to the GTX RX and TX units in the same GTX transceiver, but this does not have to be the case. The RX and TX units of different GTX transceivers can be connected to the same SDI wrapper. If only an SDI RX or only an SDI TX is required, the unused portions of the control module and the SDI core are optimized away during synthesis.

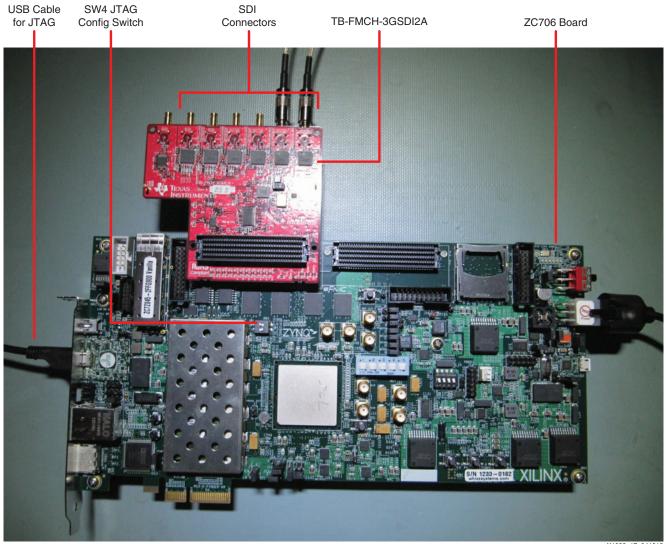

This application note includes two example demonstration applications using the SDI core. These applications run on the ZC706 evaluation board. An inrevium SDI FPGA mezzanine card (FMC) is also required to provide the SDI physical interfaces.

Figure 1: Block Diagram of Complete SDI RX/TX Interface

Notes relevant to Figure 1:

These 40-bit buses are actually four buses, each of which is 10 bits wide, and each carrying

a different SDI data stream. The number of active data streams, and therefore buses,

varies depending on the SDI mode. For example, in SD-SDI mode, only one 10-bit data

stream is active and in HD-SDI mode, two 10-bit data streams are active.

2. The optional audio embedder is a separate core and is not included with the SMPTE SDI core or with this application note.

# Using Zynq-7000 SoC GTX Transceivers for SDI Interfaces

The information in this section is intended to supplement, not replace, the information in *7 Series FPGAs GTX/GTH Transceivers User Guide* (UG476). This information highlights features of the GTX transceivers that are of particular importance for SDI applications.

In this document, the naming convention used in the *7 Series FPGAs GTX/GTH Transceivers User Guide* for the GTX transceiver ports is followed. This convention is to use only the base name of a port. When the 7 Series FPGAs Transceivers Wizard is used to create a GTX wrapper, the port names on the wrapper add a prefix to the base port name with *GTO\_* for the first transceiver in the wrapper, *GT1\_* for the second transceiver in the wrapper, and so on. Additionally, all input ports have a suffix of *\_IN* and all outputs have a suffix of *\_OUT*. For example, when a port named TXRATE is discussed in this document, the actual name of that port in the GTX wrapper would be GT0\_TXRATE\_IN for the TXRATE port of the first GTX wrapper, GT1\_TXRATE\_IN for the second GTX wrapper, and so on.

There are a variety of clocks in applications using GTX transceivers. The SDI protocol, which does not allow for clock correction by stuffing and removing extra data in the data stream, requires careful attention to how these clocks are generated and used in the application. GTX transceivers require reference clocks to operate. The reference clocks are used by phase-locked loops (PLLs) in the GTX Quad to generate serial clocks for the receiver and transmitter sections of each transceiver. As described in more detail in GTX Reference Clocks, page 4, the serial bit rate of the GTX transmitter is an exact multiple of the reference clock frequency it is using. Furthermore, the data rate of the video provided to the input of the SDI transmitter datapath must also exactly match (or be a specific multiple of) the frequency of the reference clock used by the GTX transmitter. Consequently, the designer must determine how to generate the transmitter reference clock so that it is frequency-locked exactly with the data rate of the video stream to be transmitted.

The GTX transmitter outputs a clock on its TXOUTCLK at a frequency that is exactly equal to the word rate of the data that must enter the TXDATA port of the GTX transmitter. The TXOUTCLK is generated in the GTX transmitter by dividing the serial clock from the PLL down to the word rate. In most applications, the TXOUTCLK from the GTX transmitter is buffered by a global or regional clock buffer and then used to clock the SDI transmitter datapath and the TXUSRCLK and TXUSRCLK2 clock inputs of the GTX transmitter. It is possible to use a different clock to clock the SDI transmitter datapath and the TXUSRCLK and TXUSRCLK2 ports of the GTX transmitter. A shallow TX buffer in the GTX transmitter does allow for phase differences between the data entering the TXDATA port and the internal clocking of the GTX transmitter. However, any frequency difference between the incoming data and the internal clock frequency of the GTX transmitter (as represented by TXOUTCLK) quickly causes the TX buffer to under- or overflow resulting in errors in the serial bit stream generated by the GTX transmitter. Consequently, the data rate of the stream entering the TXDATA port of the GTX transmitter (represented by the frequency of the TXUSRCLK and TXUSRCLK2 clocks) and the internal data rate of the GTX transmitter (as set by the transmitter reference clock and represented by the frequency of TXOUTCLK) must match exactly.

The GTX receiver reference clock, however, does not need an exact relationship with the bit rate of the incoming SDI signal. This is because the clock and data recovery (CDR) unit in the GTX receiver has a fairly wide range of bit rates that it can receive. That range is centered on the frequency of the reference clock, but there is not an exact frequency relationship required as there is with the transmitter. Not having an exact relationship allows the receiver reference clock to be generated by a local oscillator that has no exact frequency relationship to the incoming SDI signal. The GTX receiver generates a recovered clock that is frequency-locked to the incoming SDI bit rate. This clock is output on the RXOUTCLK port of the GTX transceiver. As is described in more detail later, RXOUTCLK is a true recovered clock when receiving HD-SDI and 3G-SDI signals, but not when receiving SD-SDI signals. Typically, RXOUTCLK is

buffered by a global or regional clock buffer and then applied to the RXUSRCLK and RXUSRCLK2 ports of the GTX receiver and used as the clock for the SDI receiver datapath.

One additional clock is required for SDI applications. This is a free-running, fixed-frequency clock that is used as the clock for the dynamic reconfiguration port (DRP) of the GTX transceiver. This same clock is also usually supplied to the control logic in the SDI wrapper where it is used for timing purposes. This clock can be any frequency up to the maximum GTX transceiver DRP clock frequency for the device being used. Xilinx recommends that the frequency of this clock be at least 10 MHz. The frequency of this clock does not require a relationship with any of the other clocks or data rates of the SDI application. This clock must not change frequencies when the SDI mode changes. It must remain exactly the same frequency at all times. It also must never stop. This clock can be used for all SDI interfaces in the device.

#### **GTX Reference Clocks**

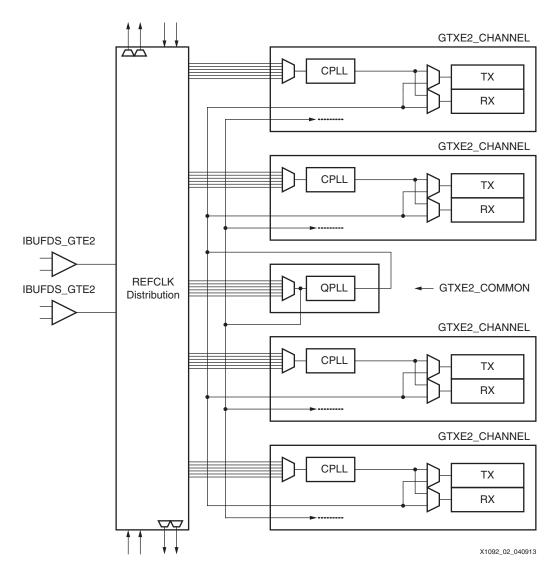

Zynq-7000 SoC GTX transceivers are grouped into Quads. Each Quad contains four GTXE2\_CHANNEL transceiver primitives and one GTXE2\_COMMON primitive containing a Quad PLL (QPLL) as shown in Figure 2. The clock generated by the QPLL is distributed to all four transceivers in the Quad. Each GTXE2\_CHANNEL has its own PLL called the channel PLL (CPLL), which can provide a clock to the RX and TX of that transceiver only. Each RX and TX unit in the Quad can be individually configured to use either the QPLL or the CPLL as its clock source. Furthermore, any RX or TX unit can dynamically switch its clock source between the QPLL and the CPLL. This configuration and the dynamic switching capability are particularly useful for SDI applications.

Typical SDI applications require GTX transceivers to support five different bit rates:

- 270 Mb/s for SD-SDI

- 1.485 Gb/s for HD-SDI

- 1.485/1.001 Gb/s (~1.4835 Gb/s) for HD-SDI

- 2.97 Gb/s for 3G-SDI

- 2.97/1.001 Gb/s (~2.967 Gb/s) for 3G-SDI

The CDR unit in the RX section of the GTX transceiver can support receiving bit rates that are up to  $\pm 1250$  ppm from the reference frequency. This makes it possible to receive all five of the SDI bit rates using a single reference clock frequency.

The TX section of the GTX transceiver, however, requires two different reference frequencies to support all five SDI bit rates. This is because the transmitters, in general, can only transmit at an exact integer multiple of the supplied reference clock frequency<sup>(1)</sup>. Therefore, most SDI applications provide two separate reference clocks to the GTX Quad. One of those clocks is used as the RX reference clock, and both of them are used as TX reference clocks. Usually, the supplied reference frequency pair are 148.5 MHz and 148.5/1.001 MHz or 74.25 MHz and 74.25/1.001 MHz.

The source of the GTX reference clocks is very application specific. The receiver reference clock can be a local oscillator because it does not need to match the incoming SDI bit rate exactly. However, because the GTX transmitter always runs at an exact multiple of the reference clock frequency, the frequency of the transmitter reference clock must be exactly related to the data rate of the transmitted data (unless the PICXO technique is used). Most often, the transmitter reference clocks are generated by genlock PLLs, thereby deriving the GTX transmitter bit rate from the studio video reference signal. In some cases, such as the SDI

-

<sup>1.</sup> Using a technique called phase interpolator controlled oscillator (PICXO), the bit rate of a GTX TX can be "pulled" by plus or minus a few hundred ppm from an exact integer multiple of the reference clock frequency. However, the pull range of the GTX TX using the PICXO technique is not sufficient to span both HD-SDI bit rates or both 3G-SDI bit rates using a single reference clock frequency.

pass-through demonstration included with this application note, the transmitter bit rate is derived from the recovered clock of a GTX receiver that is receiving an SDI signal. In such cases, an external PLL is required to reduce the jitter on the recovered clock before using it as the transmitter reference clock.

Figure 2: Zynq-7000 SoC GTX Transceiver Quad Configuration

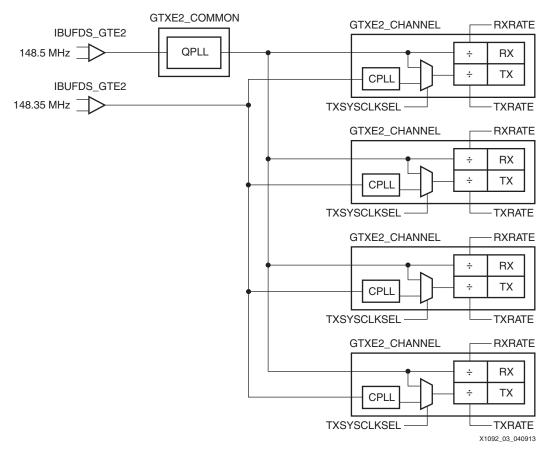

In a typical SDI application, one of these reference clocks is connected to the QPLL and the other is connected to all the CPLLs in the Quad. It does not matter which one is used for the QPLL reference clock and which is used for the CPLL reference clock. The RX units of each transceiver in the Quad are configured to always use the clock from the QPLL. The TX units can dynamically switch between the QPLL clock and the local CPLL clock, depending on the bit rate that is required at the moment. The GTX TXSYSCLKSEL port is used to select the TX unit's clock source between the QPLL and the CPLL. This common configuration for SDI applications is shown in Figure 3. In this figure, MUXes that are not used dynamically in the implementation have been replaced with wires and the reference clock routing between Quads is not shown.

Figure 3: Typical GTX Reference Clock Implementation for SDI

Additionally, each GTX RX and TX unit has a serial clock divider that divides the selected clock (QPLL or CPLL) by several selectable integer powers of two. This allows, for example, all of the RX units in the Quad to use the same clock frequency from the QPLL but operate at different line rates by using different serial clock divider values. This is very useful for SDI interfaces because the 3G-SDI bit rates are exactly twice as fast the HD-SDI bit rates. For 270 Mb/s SD-SDI, the GTX transceiver runs at the 3G-SDI line rate using 11X oversampling techniques. Thus, by using two divisors that differ by a value of two locally in each RX unit, reception of all the SDI bit rates is supported by a single RX clock frequency from the QPLL. The ability of the TX units to also locally divide the clock source by two divisors that differ by a factor of two is also important, allowing transmission of all SDI bit rates using just two reference clock frequencies. The serial clock divider value of each RX and TX unit can be changed dynamically using the RXRATE and TXRATE ports of each GTX transceiver.

The configuration shown in Figure 3 is an optimal solution for most SDI applications for several reasons:

- The receivers can receive all SDI bit rates from one fixed reference clock frequency, and the QPLL provides that reference clock to all receivers in the Quad.

- The transmitters have the flexibility to dynamically switch between the QPLL and the CPLL to get both reference clocks they need to transmit all supported SDI bit rates.

- All four receivers and all four transmitters in the Quad are fully independent. They can

each be running at different SDI bit rates and can dynamically switch between bit rates

without disrupting the other RX or TX units.

- For genlocked applications, modern genlock PLLs usually can simultaneously provide both required reference clock frequencies from the synchronization reference input signal.

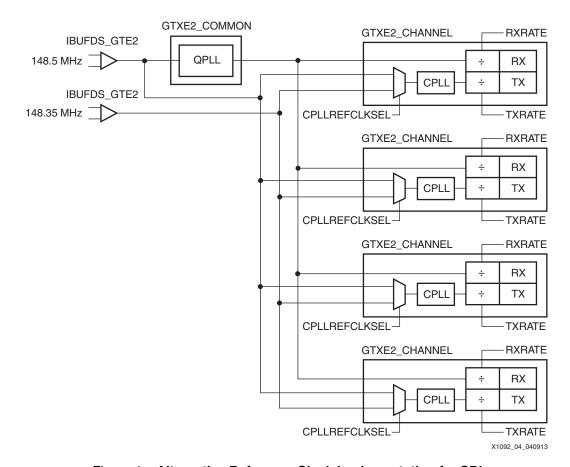

The flexibility of the reference clock routing structure in the GTX Quad does allow other PLL clocking configurations. For example, as shown in Figure 4, it would also be possible to provide both reference clocks to the clock selection MUX at the input of each CPLL. The CPLL could then dynamically switch its clock source between the two reference clock frequencies rather than switching TX between the CPLL and the QPLL. This configuration, however, has the disadvantage of requiring a reset of the CPLL and the resulting re-lock time of the CPLL each time the CPLL's reference clock frequency is switched. Thus, the configuration shown in Figure 3 has a faster switching time between TX bit rates and is the configuration supported by the control module supplied with this application note. While the configuration shown in Figure 4 is not directly supported by the supplied control module, it is an allowed and viable configuration and can be implemented if desired.

Figure 4: Alternative Reference Clock Implementation for SDI

In some applications, it might be necessary for SDI transmitters in the same Quad to be running at slightly different bit rates even though they are transmitting at the same nominal bit rate. This is often the case with SDI routers where the bit rate of each TX must exactly match the bit rate of the SDI signal received by the SDI RX to which the TX is currently connected. In these cases, two transmitters that are transmitting at the same nominal bit rate, in fact, have bit rates that differ by a few ppm. Supporting such applications is possible with the Zynq-7000 SoC GTX Quad architecture because each TX unit has exclusive use of its own CPLL. But to accomplish this, each CPLL must be provided with its own individual reference clock frequency, and the number of GTX reference clock inputs are limited. There are two reference clock inputs per Quad. A Quad can use reference clocks from the Quads above and below. Thus, it is possible to provide some GTX Quads in the device with five different reference clock frequencies (one for the RX and four for the four TX units), but overall, there are not enough reference clock inputs to allow every GTX TX in the device to have its own reference clock. The PICXO technique can be very useful in these cases because it allows a GTX TX to be pulled by a few

hundred ppm away from the frequency of its reference clock. Thus, applications where the bit rate of each SDI TX needs to be individually locked to the bit rate of a received SDI signal can be implemented by using common reference clocks as in Figure 3 and then using the PICXO technique with each GTX TX to set the exact bit rate of each SDI TX individually. This application note does not cover the PICXO technique. For further information about using PICXO, contact Xilinx technical support.

#### Resets

Refer to 7 Series FPGAs GTX/GTH Transceivers User Guide (<u>UG476</u>) for complete information about the various resets available on the GTX transceiver. The GTX transceiver resets can be divided into two basic categories: PLL resets and transceiver resets.

#### **PLL Resets**

The QPLL and the active CPLLs in each Quad each have their own reset input ports on the GTX wrapper. The control logic supplied by this application note does not generate PLL resets because these resets are very application specific. Each PLL must be reset after FPGA configuration after the reference clock source to the PLL is stable. Interruptions or changes in the reference clock to a PLL also require the PLL to be reset after the clock is once again stable. It is recommended that these PLLs not be reset until at least 500 ns after configuration of the programmable logic (PL) portion of the SoC.

#### **Transceiver Resets**

The GTX transceiver has two reset modes called sequential mode and single mode. Sequential mode is the easiest to use and is the mode supported by the control module supplied with this application note. In sequential mode, when any reset input is asserted, the reset state machine in the transceiver automatically asserts all other required transceiver resets in sequential order.

The control module generates three reset signals for the GTX transceiver: GTTXRESET, GTRXRESET, and TXPMARESET. GTTXRESET resets all portions of the transceiver's TX unit. Likewise, GTRXRESET resets all portions of the RX unit. A complete reset of the TX and RX units using these two resets must be done once after configuration. These resets must be initiated after the PLLs have been reset and are locked to their reference clocks. Separate but identical state machines in the control module monitor the PLL reset and PLL locked signals for the RX and the TX. These state machines assert the GTTXRESET or GTRXRESET signals when they detect that the PLL that supplies the clock to the TX or RX unit has been reset. The state machine then waits for the PLL to assert its locked signal while observing a minimum assertion period for the reset signal. This minimum assertion period is controlled by the PLLLOCKDLY parameter/generic. After the PLL indicates it is locked, the GTTXRESET or GTRXRESET is negated. The recommended minimum period of these resets is one cycle of the reference clock supplied to that unit. By default, these resets are asserted for 16 cycles of the fixed frequency clock applied to the clk port of the SDI wrapper. The PLLLOCKDLY parameter/generic specifies the width of a binary counter. Thus, the minimum assertion period of the these resets is given by Equation 1.

Minimum GT[R/T]XRESET period =

$$\frac{2^{PLLLOCKDLY}}{\text{clk frequency}}$$

Equation 1

The GTX TXPMARESET port resets the PMA portion of the TX unit. In SDI applications, when the TXSYSCLKSEL port is changed dynamically to switch the TX unit's clock between the CPLL and the QPLL, TXPMARESET must be asserted during the time that TXSYSCLKSEL changes. TXPMARESET must be asserted before changing TXSYSCLKSEL and must remain asserted until after TXSYSCLKSEL has changed values. The control module contains the necessary logic to sequence the TXPMARESET and TXSYSCLKSEL signals whenever such a dynamic clock change is requested by a change on the SDI wrapper's tx\_m port.

The SDI control module also briefly asserts TXPMARESET for a given period of time after the txplllock input to the SDI wrapper becomes asserted. This is useful in cases where a PLL is used to generate the TX reference clock and the output frequency of the PLL might continue to

fluctuate for some time even after it indicates that it is locked. For example, in the pass-through example application included with this application note, a Si5324 digital PLL is used to reduce jitter on the clock recovered by the GTX RX to provide a clean reference clock to the GTX TX. The recovered clock changes frequencies whenever the bit rate of the input SDI signal changes, and the Si5324 might take some time to re-lock after the clock changes frequencies. The TXPMARESET helps ensure that the GTX TX returns to normal operation when the reference clock to the QPLL or CPLL changes in such a manner. The delay between when the txplllock input to the SDI wrapper is asserted until the control module pulses its gtx\_txpmareset output is controlled by a parameter/generic to the SDI wrapper named TXPMARESETDLY\_MSB. This delay is related to the frequency of the fixed frequency clock on the clk port of the SDI wrapper, as given in Equation 2.

TXPMARESETdelay =

$$\frac{2^{\text{TXPMARESETDLY\_MSB} + 1}}{\text{clk frequency}}$$

Equation 2

Some applications might have additional cases where GTTXRESET, GTRXRESET, or TXPMARESET need to be asserted. The reset outputs of the control module can usually simply be ORed with the application's reset conditions before being connected to the reset input ports of the GTX wrapper.

Depending on the application's requirements, other GTX resets might be required. One such reset is the TXPCSRESET. It is recommended that TXPCSRESET be asserted to reset the TX buffer whenever the TX buffer underflows or overflows, as indicated by bit 1 of the GTX TXBUFSTATUS output port. In the example SDI applications provided with this application note, bit 1 of TXBUFSTATUS is always wired directly to the TXPCSRESET input port of the GTX for this reason.

The GTX transceiver has two inputs called RXUSERRDY and TXUSERRDY. These inputs are used by the transceiver's internal reset state machine to determine when to reset the PCS sections of the RX and TX. The control module supplied with this application note does not generate the RXUSERRDY and TXUSERRDY signals. However, the SDI wrapper module, which includes the control module and an instance of the SDI core, does include some simple example logic for generating these signals. The logic in the wrapper that generates the TXUSERRDY signal is just a 5-bit shift register that keeps TXUSERRDY Low until the fifth TXUSRCLK signal occurs. The logic for RXUSERRDY is identical and keeps RXUSERRDY Low until the fifth RXUSRCLK occurs. This is the minimum recommended logic for generating these signals and has proven to be sufficient for most SDI applications. However, users should always refer to the requirements for RXUSERRDY and TXUSERRDY as described in 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476) and include logic to control these signals appropriately if the example logic in the wrapper is not sufficient for a particular application.

#### **SDI Core Resets**

The SDI wrapper has reset inputs for the RX section (rx\_rst) and the TX section (tx\_rst). The rx\_rst input is a synchronous reset in the rx\_usrclk clock domain. To fully reset the RX section of the SDI core, both the rx\_ce\_sd and the rx\_din\_rdy\_3G inputs of the SDI wrapper must be High while rx\_rst is High. Asserting rx\_rst under these conditions fully resets the RX section of the SDI core. This includes the state machine that controls the SDI mode search algorithm that sequences the GTX RX and SDI RX through the various SDI modes until lock is achieved. Thus, care must be taken when using rx\_rst that it not be asserted indiscriminately when not needed. Otherwise, the SDI RX might never lock or might lock much more slowly than it otherwise could.

Most applications do not even need to assert the rx\_rst signal. The SDI RX section comes out of FPGA configuration in a working state. If the illegal state recovery logic of the various finite state machines in the SDI RX section are not optimized away during synthesis, the SDI RX is very robust at recovering from almost any sort of abnormal condition. Different synthesizers have their own unique ways of specifying whether or not the illegal state recovery of finite state machines is left intact or optimized away. For the ISE® Design Suite, setting the XST setting

SAFE\_IMPLEMENTATION to TRUE ensures that illegal state recovery is included with the state machines. It is recommended that SAFE\_IMPLEMENTATION or its equivalent be enabled in all applications using the SDI core. The default for the ISE tools is for SAFE\_IMPLEMENTATION to be set to FALSE, so this should be changed when processing an SDI application. The example SDI applications included with this application note hardwire rx\_rst Low. The BIT files for these example applications were generated in the ISE tools with SAFE\_IMPLEMENTATION set to TRUE. These applications are very robust, showing that, in most cases, rx\_rst can simply be hardwired Low.

The tx\_rst input is a synchronous reset in the tx\_usrclk clock domain. To fully reset the TX section of the SDI core, both tx\_ce and tx\_din\_rdy inputs of the SDI wrapper must be High while tx\_rst is High. As with the RX section described in the previous paragraph, the TX section of the SDI core emerges from FPGA configuration in working condition and, as long as the illegal state recovery of the finite state machines is not optimized out, the TX section is very robust. The tx\_usrclk is generally driven by the GTX TXOUTCLK through a global clock buffer. TXOUTCLK can have erratic timing whenever TXSYSCLKSEL is dynamically changed to switch the TX clock source between the QPLL and the CPLL and when TXRATE is dynamically changed to change the serial clock divider. While the SDI core's TX section can automatically recover from these abnormal timing conditions on tx\_usrclk, often the portions of the application that are clocked by this same clock might not be so robust. This is true of both of the SDI demonstration applications and they both take great care to protect logic clocked by TXOUTCLK when it is known that TXSYSCLKSEL and TXRATE are changing.

In both example SDI applications, there is an 11-bit shift register that is initialized with a pattern of 00000100001. This shift register is part of the application, not part of the SDI wrapper or SDI core, and it generates the SD-SDI TX clock enable with a 5/6/5/6 clock cycle cadence as required by the TX section of the SDI core when transmitting SD-SDI with the Zynq-7000 SoC GTX transceivers. The shift register shifts right by one bit every tx\_usrclk clock cycle, and the LSB of the shift register is wrapped around to the MSB input of the shift register so that this pattern continuously circulates in the shift register. The pattern in the shift register often becomes corrupted when the TXOUTCLK is abnormal because the TXSYSCLKSEL or TXRATE inputs to the GTX are dynamically changed. Thus, whenever either TXSYSCLKSEL or TXRATE are changed, the application code, not the SDI wrapper or SDI core, resets this shift register, restoring the correct pattern required for TX clock enable generation. To be safe, the tx\_rst port of the SDI wrapper is also asserted when the shift register is reset, only to ensure that all state machines in the SDI core's TX go to their initial conditions.

# **Dynamic Bit Rate Switching**

Two types of dynamic switching are required to support the various SDI bit rates: switching the serial clock divider and switching the serial clock source. For the SDI RX, only the serial clock divider needs to switch dynamically. For the SDI TX, both types of dynamic switching are used.

Figure 5 is a block diagram view of the signal connections associated with dynamic rate switching.

Figure 5: Signal Connections for Dynamic Rate Switching

## **Dynamically Switching the Serial Clock Dividers**

Dynamically switching the serial clock dividers changes the line rate of the RX or TX between 3G-SDI operation (~3 Gb/s) and HD-SDI operation (~1.5 Gb/s). For SD-SDI, the GTX RX and TX are configured for the 3G-SDI line rate, and 11X oversampling is used. Each RX and TX unit in a GTX Quad has its own serial clock divider and control port. The serial clock divider of the RX unit is controlled by its RXRATE port. The serial clock divider of a TX unit is controlled by its TXRATE port.

The control module contains logic to control the RXRATE and TXRATE ports of a GTX transceiver through the SDI wrapper's gtx\_rxrate and gtx\_txrate output ports. The gtx\_txrate output port changes in response to a change on the tx\_mode input port of the control module. The gtx\_rxrate output port changes in response to a change on the rx\_mode input port of the control module. In the SDI wrapper, the rx\_mode port of the control module is connected internally to the source of the rx\_mode signal, the SMPTE SDI core.

In the following discussion, all frequencies are given assuming the GTX is operating at line rates of 1.485 Gb/s or 2.97 Gb/s. When the PLL is locked to a 148.5/1.001 MHz or 74.25/1.001 MHz reference clock, all frequencies would be divided by 1.001.

The frequency of the serial clock out of the PLL divider must be half the line rate. For HD-SDI, the serial clock frequency must be 742.5 MHz. For SD-SDI and 3G-SDI, the serial clock frequency must be 1.485 GHz.

The operating range of the CPLL in the Zynq-7000 SoC GTX transceiver is 1.6 GHz to 3.3 GHz. For SDI applications, the CPLL must operate at 2.97 GHz. So, for HD-SDI bit rates, the serial clock divider must be set to divide by 4, resulting in a serial clock frequency of 742.5 MHz. For SD-SDI and 3G-SDI bit rates, the serial clock divider must be set to divide by 2, resulting in a serial clock frequency of 1.485 GHz.

The QPLL in the Zynq-7000 SoC GTX Quad has two operating ranges. The lower range is from 5.93 GHz to 8 GHz or lower in some packages. The upper range is from 9.8 GHz to some upper limited determined by speed grade and package type. For SDI applications, the lower range should be used, and the QPLL should be operated at 5.94 GHz or 5.94/1.001 GHz, almost exactly at the 5.93 GHz lower limit of the lower range. In fact, this lower limit of the QPLL operating range is specifically set to support SDI applications. The clock from the QPLL is

always divided by two before leaving the QPLL block. Thus, when using the lower QPLL range, the clock into the serial clock divider of an RX or TX unit from the QPLL is actually 2.97 GHz, the same frequency as the clock from the CPLL. Thus, the same two serial clock divider values of 4 for HD-SDI and 2 for SD-SDI and 3G-SDI apply when the QPLL clock is used in its lower operating range. If the QPLL is operating in its upper range, the clock is twice as fast, so a serial clock divider value of 8 must be used in HD-SDI mode and 4 in SD-SDI and 3G-SDI mode.

For the control module to generate the correct RXRATE and TXRATE values, it must know what range the PLL is operating in. This information is supplied to the control module on its gtx\_rxpllrange and gtx\_txpllrange ports. When using the QPLL in its lower operating range or the CPLL, the gtx\_rxpllrange and gtx\_txpllrange ports can simply be set Low all of the time. This is the normal mode of operation for SDI applications using the Zynq-7000 SoC GTX transceivers.

If the QPLL is operating in its upper range, any unit using a clock from the PLL must have its corresponding control module range port (gtx\_rxpllrange or gtx\_txpllrange) set High. Furthermore, if a unit is dynamically switching between using the QPLL operating in the upper range and the CPLL, the value on the range port must change dynamically too. Using Figure 3 as an example and with the QPLL operating in its upper range at a frequency of 11.88 GHz, the gtx\_rxpllrange port of each transceiver's control module would be permanently wired High because the QPLL is always used as the clock source for the GTX RX. The GTX TX is switched dynamically between the QPLL and the CPLL. Thus, the gtx\_txpllrange port of each transceiver's control module must be dynamically switched. When the GTX TX is using the clock from the QPLL, the gtx\_txpllrange port must be High. When the GTX TX is using the clock from the CPLL, the gtx\_txpllrange port must be Low. This only applies when using the QPLL in its upper operating range. Normally, for SDI applications, the QPLL operates in its lower range and the gtx\_rxpllrange and gtx\_txpllrange input ports of the control module (and the SDI wrapper) must be Low all of the time.

### **Dynamically Switching the TX Clock Source**

In applications where the GTX clock sources are configured as shown in Figure 3, the GTX TX units must dynamically switch their clock source between the QPLL and the CPLL to support all of the SD bit rates. In Figure 3, a TX unit uses the QPLL clock to transmit HD-SDI at 1.485 Gb/s, 3G-SDI at 2.97 Gb/s, and SD-SDI at 270 Mb/s. The TX unit uses the CPLL clock to transmit HD-SDI at 1.485/1.001 Gb/s and 3G-SDI at 2.97/1.001 Gb/s.

The GTX TXSYSCLKSEL port controls the clock MUX that selects between the QPLL and the CPLL. This is actually a two-bit port, and the two bits of the port control different MUXes. But, for SDI applications, both bits of the TXSYSCLKSEL port should always be the same and should switch together.

To ensure reliable recovery of the GTX TX after dynamically switching its clock source, the GTX TXPMARESET signal must be asserted before the TXSYSCLKSEL port is changed and must remain asserted for a short period of time after the TXSYSCLKSEL port is changed. The control module contains the necessary logic to control the TXSYSCLKSEL and TXPMARESET ports of the GTX for dynamic switching of the TX clock source. The SDI wrapper's gtx\_txsysclksel output port should be connected to the TXSYSCLKSEL port of the GTX wrapper. The SDI wrapper's gtx\_txpmareset output port should be connected to the TXPMARESET port of the GTX wrapper. The control module properly sequences the TXPMARESET and TXSYSCLKSEL ports to dynamically switch the clock source between the QPLL and the CPLL in response to a change in value on the SDI wrapper's tx\_m port. The values driven to the TXSYSCLKSEL port of the GTX for each value of tx\_m are controlled by two parameters/generics to the SDI wrapper called TXSYSCLKSEL M 0 and TXSYSCLKSEL\_M\_1. A value of 00 on TXSYSCLKSEL selects the CPLL, and a value of 11 selects the QPLL. Traditionally, Xilinx has used a Low on tx m to select the 148.5 MHz reference and High on tx\_m to select the 148.5/1.001 MHz reference. So, in an application configured as shown in Figure 3 where the QPLL is referenced to 148.5 MHz and the CPLL is referenced to 148.5/1.001 MHz, the SDI wrapper's TXSYSCLKSEL\_M\_0 parameter/generic

would be assigned a value of **11** to select the QPLL when tx\_m is Low and the TXSYSCLKSEL\_M\_1 parameter/generic would be assigned a value of **00** to select the CPLL when tx\_m is High. In fact, the default value of TXSYSCLKSEL\_M\_0 is **11** and the default value of TXSYSCLKSEL M\_1 is **00**.

Of course, not all applications require dynamic switching of the TX clock source between the QPLL and the CPLL. In those cases, the tx\_m port and the two parameters/generics can be assigned to appropriate values to permanently select either the QPLL or the CPLL as the clock source for the GTX TX. Or, the TXSYSCLKSEL port of the GTX wrapper can be hardwired to **00** to select the CPLL or **11** to select the QPLL, and the gtx\_txsysclksel output port of the SDI wrapper can be left disconnected.

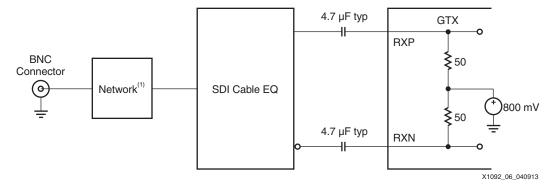

#### **SDI Electrical Interface**

External SDI cable equalizers and cable drivers are required to convert the serial signals into and out of the GTX transceivers to SDI electrical standards.

An external SDI cable equalizer must be used to convert the single-ended  $75\Omega$  SDI signal to a  $50\Omega$  differential signal compatible with the receiver input signal requirements of the GTX transceiver. Appropriate SDI cable equalizers are available from several manufacturers. The differential outputs of these cable equalizers usually must be AC-coupled to the GTX receiver input signals. An example of interfacing a typical SDI cable equalizer to a GTX receiver is shown in Figure 6. Capacitance values of the coupling capacitors must be large enough to pass the SDI pathological signals without significant signal droop. Typical values used are between 1  $\mu$ F and 4.7  $\mu$ F.

The differential inputs of the GTX RX have built-in differential termination. As described in 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476), RX Termination Use Mode 3 is the recommended termination mode for the GTX RX inputs in SDI applications. The GTX internal programmable termination voltage should be set to 800 mV for SDI applications.

Figure 6: Interfacing an SDI Cable Equalizer to the GTX Receiver Inputs

Notes relevant to Figure 6:

Consult the SDI cable EQ manufacturer's information for the network between the SDI cable EQ and the BNC connector.

Similarly, the differential serial outputs of the GTX transmitter are connected to the inputs of an SDI cable driver, usually with AC coupling as shown in Figure 7. The cable driver converts the differential signal from the GTX transmitter into a single-ended signal with electrical characteristics meeting the SDI standards. SDI cable drivers typically have a slew rate control input that sets the slew rate of the cable driver. The slew rate requirements for SD-SDI are significantly different than the slew rate requirements for HD-SDI and 3G-SDI. The slew rate control input of the SDI cable driver is typically controlled by the FPGA. The control module supplied with this application note generates a slew rate control signal for use with the external SDI cable driver.

Figure 7: Interfacing an SDI Cable Driver to the GTX Transmitter Outputs

Notes relevant to Figure 7:

1. Consult the SDI cable driver manufacturer's information for the network between the SDI cable driver and the BNC connector.

#### **SD-SDI Considerations**

# **Receiving SD-SDI**

The 270 Mb/s bit rate of SD-SDI is below the minimum line rate supported by the GTX RX. To receive 270 Mb/s SD-SDI, the GTX RX is used as an asynchronous oversampler to sample the SD-SDI bit stream at 11 times 270 Mb/s (2.97 gigasamples per second (GSPS)) without regard to where bit transitions occur. The CDR unit in the GTX RX is locked to the reference clock by asserting the GTX RXCDRHOLD input port High. This prevents the CDR from trying to lock to the slow SD-SDI signal and results in more uniform oversampling of the SD-SDI signal.

A data recovery unit (DRU), implemented in the programmable logic of the FPGA, examines the oversampled SD-SDI data from the GTX RX, determines the best sample to use for each bit, and outputs the recovered data. This DRU is not part of the SDI core, but is provided as part of this applications note's control module.

The DRU provided with this application note is a version of the DRU described in *Dynamically Programmable DRU for High-Speed Serial I/O* (XAPP875) that has been optimized for recovering 270 Mb/s SD-SDI bit streams from 11X oversampled data. The general-purpose DRU described in *Dynamically Programmable DRU for High-Speed Serial I/O* can recover data using many different oversampling factors and, as a result, is larger and uses more FPGA resources than the optimized version provided here for use with the SDI core.

The SD-SDI standard SMPTE ST 259 [Ref 4] specifies several other bit rates besides 270 Mb/s. The optimized DRU supplied with this application note only supports 270 Mb/s because the vast majority of SDI interfaces only need to support the 270 Mb/s SD-SDI bit rate. However, if other SD-SDI bit rates need to be supported by the application, the optimized DRU can be replaced with the DRU from *Dynamically Programmable DRU for High-Speed Serial I/O*. Because that DRU supports fractional oversampling factors, it is possible to receive the other SD-SDI bit rates without requiring any additional RX reference clock frequencies. The 540 Mb/s SD-SDI bit rate specified by SMPTE ST 344 [Ref 5] is within the supported line rate range of the GTX transceiver, and thus the GTX RX does not need to use the DRU to receive it. However, receiving the 540 Mb/s bit rate without the DRU requires a different reference clock frequency than is used for the other SDI bit rates. Thus, it is usually more convenient to use the DRU from *Dynamically Programmable DRU for High-Speed Serial I/O* to receive the 540 Mb/s ST 344 signal using 5.5X oversampling so that the standard SDI reference clock frequency can be used.

Receiving the additional SD-SDI bit rates also requires modifications to the SDI RX rate detector that controls the locking of the SDI RX by searching sequentially through all SDI bit

rates until the receiver locks. The rate detection algorithm is implemented in the triple\_sdi\_rx\_autorate.v or triple\_sdi\_rx\_autorate.vhd file supplied with the SMPTE SDI core. Xilinx does not provide an equivalent module that supports the additional SD-SDI bit rates.

The DRU does not recover a clock and, because the CDR unit in the GTX RX is locked to its reference clock, the RXOUTCLK is not locked to the incoming bit rate in SD-SDI mode. The DRU does produce a data strobe indicating when a 10-bit data word is ready on its output. This data strobe is used by the SDI core to generate a clock enable that is asserted at a 27 MHz rate, typically with a 5/6/5/6 cadence relative to the RXOUTCLK clock from the GTX. The rx\_ce\_sd output of the SDI wrapper is derived from the DRU data strobe and has the same cadence. Occasionally the cadence of the DRU data strobe and the rx\_ce\_sd signal varies from the typical 5/6/5/6 cadence. This occurs when the DRU needs to make up for the slight difference between the actual SD-SDI bit rate and the frequency of the local reference clock provided to the GTX RX.

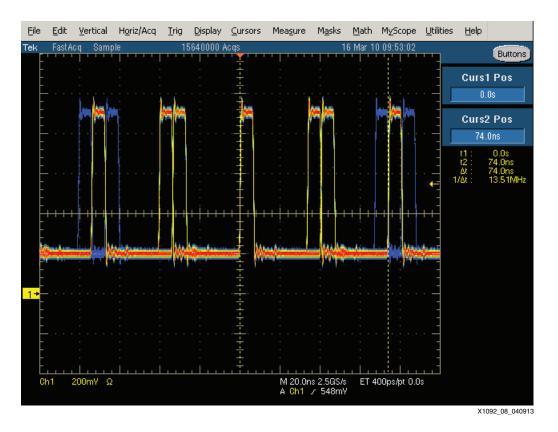

Figure 8 is a screen capture from an oscilloscope showing the 27 MHz rx\_ce\_sd signal. The scope is triggered on the rising edge of rx\_ce\_sd at the center of the screen. The scope is in infinite persistence mode and the waveform was allowed to accumulate for several minutes. The waveform is temperature-coded from red (indicating the most common position of the signal) to blue (indicating the least common position). The incoming SD-SDI signal that was used to create this screen capture was asynchronous to the local reference clock used by the GTX receiver. The rx\_ce\_sd pulses on either side of the center pulse are always 5 or 6 clock cycles away from the center pulse because of the 5/6/5/6 cadence of the rx\_ce\_sd signal.

Figure 8: Oscilloscope Capture of SD-SDI Clock Enable

The two pulses at the far right and far left of the trace are nominally 11 clock cycles from the center pulse because of the 5/6/5/6 cadence. The nominal position is marked by the yellow and red pulse. For the far right pulse, the dashed yellow vertical cursor marks the position that is 11 clock cycles from the rising edge of the center pulse. The nominal locations of the central

yellow/red pulses are surrounded on either side by blue pulses indicating that the DRU occasionally needs to make the period of the rx\_ce\_sd cycle either 10 clock cycles or 12 clock cycles long to compensate for the frequency differences between the local reference clock and the incoming SD-SDI signal.

The SD-SDI DRU is supplied with this application note as an encrypted, pre-generated file called <code>dru.ngc</code>. It is not possible to do any simulation of a design using the <code>dru.ngc</code> file because of its encryption. However, the files <code>dru\_sim.v</code> and <code>dru\_sim.vhd</code> included with this application note provide simplified simulation models of the DRU. Either of these files can be used during simulation to replace the <code>dru.ngc</code> file. However, these simulation models should not be used in a design intended for use in the actual FPGA because the models do not support any variation in frequency between the GTX RX reference clock and the SD-SDI bit stream.

#### **Transmitting SD-SDI**

As with reception of SD-SDI, transmission of the slow 270 Mb/s SD-SDI bit rate is not directly supported by the GTX TX. To transmit the SD-SDI signal, the GTX TX is configured for a line rate of 2.97 Gb/s. The SDI core replicates each bit to be transmitted 11 times so that the data out of the SDI core and into the TXDATA port of the GTX TX contains 11 consecutive copies of each bit. The resulting signal output by the GTX TX is a valid 270 Mb/s SD-SDI signal.

#### **Generating an SD-SDI Recovered Clock**

In SD-SDI mode, the RXOUTCLK of the GTX RX is not really a recovered clock because the CDR unit is locked to the frequency of the reference clock, not to the SD-SDI bit stream. The only signal available that actually indicates the data rate of the incoming SD-SDI bit stream is the 27 MHz rx\_ce\_sd output of the SDI wrapper.

For some video applications, particularly those that do not need to retransmit the recovered video over an SDI interface, the rx\_ce\_sd signal might be sufficient as a recovered clock. Typically, this signal is used as a clock enable to downstream modules that are clocked with the RXOUTCLK from the GTX receiver. This is how the SDI datapath in the SDI core works – using the rx\_ce\_sd signal as a clock enable.

If the received video data is to be retransmitted as an SD-SDI signal using a GTX TX, a low-jitter recovered clock is required. The recovered clock must have low enough jitter that it can be used as a reference clock for the GTX transmitter PMA PLL. Furthermore, the frequency of the recovered clock must be 74.25 MHz or 148.5 MHz so that the GTX transmitter can use 11X oversampling to transmit the 270 Mb/s SD-SDI data. This requires the use of an external, low-bandwidth PLL or use of the PICXO technique. (The PICXO technique is not covered in this application note. Contact Xilinx technical support for inquiries about the PICXO technique and SDI.) The bandwidth of the mixed-mode clock manager (MMCM) in the Zyng-7000 SoC is too high to adequately filter out the large amounts of low-frequency jitter present on the rx\_ce\_sd signal from the SDI receiver. The National Semiconductor LMH1983 and the Silicon Labs Si5324 PLLs can both perform this function. Both of these devices can take in the rx ce sd signal as a 27 MHz reference and multiply it up to either 74.25 MHz or 148.5 MHz while also filtering out the jitter. The resulting clock is suitable for use as a reference clock for the GTX TX. The pass-through demonstration included with this application note uses an Si5324 to generate a 148.5 MHz reference clock for the GTX TX from the 27 MHz rx\_ce\_sd signal in exactly this manner in SD-SDI mode. When retransmitting either HD-SDI or 3G-SDI, the same Si5324 is reprogrammed to filter jitter from the RXOUTCLK output of the GTX RX, doubling its frequency in the case of HD-SDI, thereby producing a low-jitter 148.5 MHz reference clock for the GTX TX.

Another alternative is to use an external genlock PLL and lock it to the video sync signals from the recovered video. The output of the genlock PLL is an SD-SDI recovered clock.

Sometimes a recovered clock is required to drive external video application-specific standard product (ASSP) devices. In SD-SDI mode, such a clock probably needs to have a frequency of 27 MHz and have lower jitter than is present on the rx\_ce\_sd signal, but does not need to have very low jitter as is the case when producing a GTX TX reference clock. The techniques

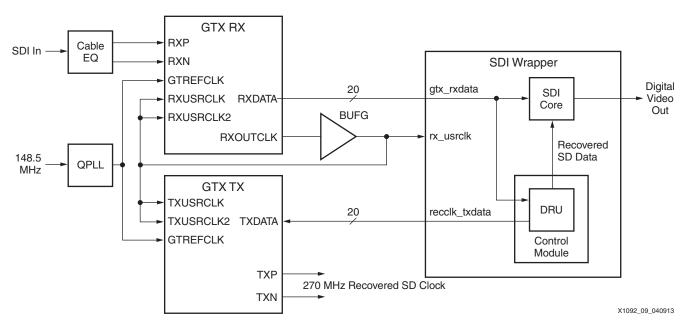

mentioned previously can be used, but it might be preferable to generate such a recovered clock entirely in the SoC without requiring external components. Unfortunately, the jitter on the rx\_ce\_sd signal is too high to allow it to be used directly as a reference clock input to the MMCM. But, there is a way to generate a recovered SD-SDI clock using a spare GTX transmitter, as shown in Figure 9.

Figure 9: Using a GTX TX to Generate an SD-SDI Recovered Clock

The control module's recclk\_txdata port can be connected to the TXDATA port of a spare GTX transmitter. The GTX TX must use the same reference clock as the GTX RX that is receiving the SDI input signal. The TXUSRCLK and TXUSRCLK2 ports of the GTX TX must be connected to the same clock that is driving the RXUSRCLK and RXUSRCLK2 ports of the GTX TX and the rx\_usrclk port of the SDI wrapper. The GTX TX must be configured for a line rate of 2.97 Gb/s with no encoding and with a 20-bit TXDATA port.

When configured in this manner, the serial output of the GTX transmitter is a 270 MHz clock that is frequency-locked to the incoming SD-SDI signal. In other words, it is a true recovered clock for SD-SDI. The GTX transmitter serial output pins can be connected to a global or regional clock LVDS input of the Zynq-7000 SoC, with appropriate care to properly terminate the GTX transceiver TX outputs and translate them to LVDS. The 270 MHz clock can then be used in whatever manner is required in the SoC. For example, it can be divided by 10 to get a 27 MHz recovered clock to drive internal or external video datapaths. The signal has low enough jitter that it can be used as a reference clock to an MMCM.

The recclk\_txdata port of the DRU is not wired from the control module to an output port in the SDI wrapper supplied with this application note. However, if an application needs to use this feature, it is a simple matter to edit the SDI wrapper to add this output port.

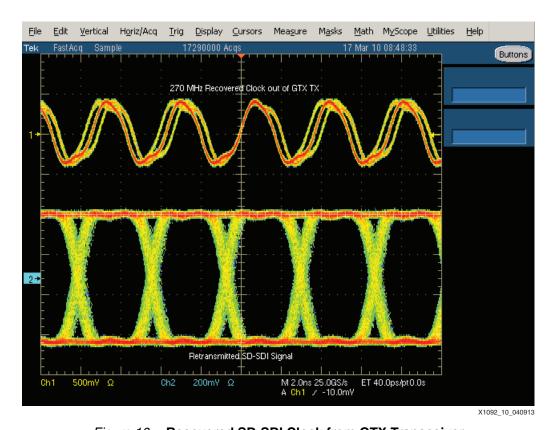

The GTX TX that is used to generate the recovered SD-SDI clock does not have to be configured for SDI. It only needs to be configured to always run at 2.97 Gb/s with no encoding. The data supplied to the TXDATA port of the GTX from the recclk\_txdata port of the control module creates a 270 MHz clock on the GTX TX serial output pins. The edges of the generated clock move around by plus or minus one bit time of the 2.97 Gb/s line rate to modify the frequency of the output signal so as to exactly match with the bit rate of the input SD-SDI signal. Thus, the cycle-to-cycle jitter on the 270 MHz clock generated by the GTX TX is ±337 ps plus whatever jitter is inherent in the GTX TX output signal (1 bit time at 2.97 Gb/s is 337 ps). This can be seen in Figure 10. The top trace is the 270 MHz clock generated by the GTX TX. The scope was triggered on the rising edge of the recovered clock at the center of the screen.

Looking at the rising edges of the cycles on either side of the trigger point, the ±337 ps cycle-to-cycle jitter is clearly seen because these rising edges each have three discrete rising points. The bottom trace in Figure 10 is the SD-SDI that is being retransmitted by another GTX TX.

Figure 10: Recovered SD-SDI Clock from GTX Transceiver

The recclk\_txdata port is not output from the SDI wrapper. This is because this port is not used by most SDI applications. If needed, the SDI wrapper can be edited to add a new port and connect it to the recclk\_txdata port of the control module.

#### **RX Bit Rate Detection**

The SDI core can automatically determine the SDI mode (SD-SDI, HD-SDI, or 3G-SDI) of the SDI signal coming into the GTX RX. When it is not locked to the current SDI input signal, the SDI core sequences the GTX RX through the three different SDI modes until it detects recognizably good SDI data on the RXDATA output port of the GTX. At that point, the SDI core indicates that it is locked to the SDI signal by asserting its rx\_mode\_locked output. It also indicates which SDI mode the RX is locked to on its sdi\_mode output port.

However, when the SDI core is in HD-SDI mode, it has no way of determining if the bit rate of the input SDI signal is 1.485 Gb/s or 1.485/1.001 Gb/s. Likewise, in 3G-SDI mode, the SDI core cannot determine whether the bit rate of the input SDI signal is 2.97 Gb/s or 2.97/1.001 Gb/s. The control module supplied with this application note, however, contains a bit rate detector that can distinguish between 1.485 Gb/s and 1.485/1.001 Gb/s, and between 2.97 Gb/s and 2.97/1.001 Gb/s. The SDI wrapper output port rx\_bit\_rate is Low when the input SDI signal's bit rate is either 1.485 Gb/s or 2.97 Gb/s. The rx\_bit\_rate is High when the input SDI signal's bit rate is either 1.485/1.001 Gb/s or 2.97/1.001 Gb/s.

For the bit rate detection feature to work, the SDI wrapper must be supplied with a fixed-frequency clock on its clk input port. It is recommended that the frequency of this clock be at least 10 MHz. If the frequency is over 150 MHz, it might be difficult to meet timing in the bit

rate detection logic. The SDI wrapper has a parameter/generic called FXDCLK\_FREQ that must be used to specify the frequency of the clock connected to the clk port. The value of FXDCLK\_FREQ must be set equal to the frequency of the fixed-frequency clock in Hz.

The SDI wrapper uses the fixed-frequency clock for other purposes besides RX bit rate detection. Thus, even if the bit rate detection feature is not used in a particular application, a fixed-frequency clock must be supplied to the clk port of the SDI wrapper.

# Implementing an SDI Interface in a Zynq-7000 SoC

There are several steps required to implement an SDI interface in a Zynq-7000 SoC design. Those steps are:

- 1. Generate a GTX wrapper using the 7 Series FPGAs Transceivers Wizard.

- Generate the SMPTE SDI LogiCORE IP using the CORE Generator tool or the Vivado IP catalog.

- 3. Instance the GTX wrapper and the SDI wrapper from this application note into the application.

- 4. Put the dru.ngc file from this application note into the ISE tools project directory or add it to the Vivado tools project (see the readme.txt file in xapp1092.zip for more information).

- 5. Apply proper timing constraints for the SDI wrapper.

# **Generating the GTX Wrapper**

Use the 7 Series FPGAs Transceivers Wizard, called the *Wizard* for the rest of this document, to generate a GTX wrapper. With previous generations of Xilinx GT transceivers, it was possible to create a GT wrapper using the Wizard that contained a single GT transceiver and then instance that wrapper multiple times even if the transceivers were in the same GT tile. With the 7 series GTX transceiver, this is no longer possible. The user must generate a GTX wrapper that contains exactly the number of transceivers that the application uses in the GTX Quad tile or multiple Quad tiles. This is because the Wizard always instances a GTXE2\_COMMON in the GTX transceiver, and there is only one GTXE2\_COMMON block per GTX Quad. Thus, if the user tries to place two GTX wrappers (each with a GTXE2\_COMMON block in them) in the same GTX Quad, the tools flag this as an error.

For those transceivers that are used to implement SDI interfaces, select the **hd sdi** protocol template. This chooses the correct GTX port set and the attributes needed to support SDI. It is highly recommended that GTX wrappers used for SDI applications be generated with the hd sdi protocol template and not with the 3g sdi or sd sdi protocol templates.

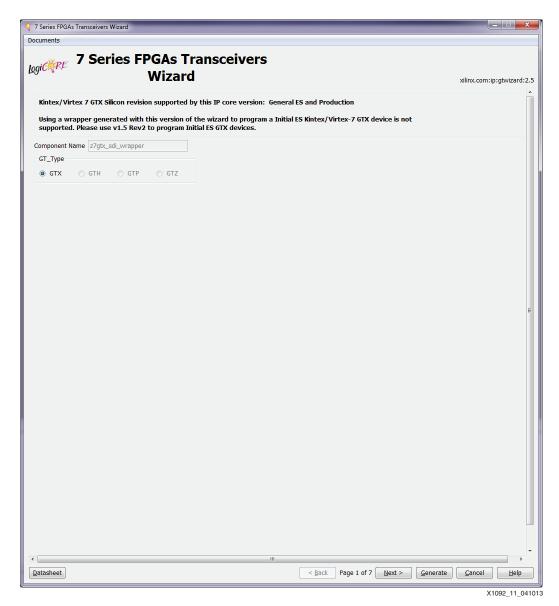

The following information details exactly the steps required to generate the GTX wrapper using the Wizard version 2.4. This example creates a GTX wrapper that includes all four GTX transceivers in one GTX Quad all configured for SDI.

The 7 Series FPGAs Transceivers Wizard is found in the **IO Interfaces** folder in the top-level **FPGA Features and Design** folder.

Figure 11 shows the first page of the Wizard. On this page, select **hd sdi** from the **Protocol template** drop-down menu. This sets the line rate to 1.485 Gb/s, and the reference clock frequencies default to 148.5 MHz. If a different reference clock frequency such as 74.25 MHz is required, the reference clock drop-down menus for the TX and RX show the only reference clock frequencies that are supported. Even when one of the reference clocks is actually 148.5/1.001 MHz, both reference clock frequencies should be set to 148.5 MHz and both line rates set to 1.485 Gb/s. The control module takes care of dynamically changing the line rate to 2.97 Gb/s for 3G-SDI and HD-SDI modes. Thus, the line rate should always be set to 1.485 Gb/s in the Wizard.

Figure 11: 7 Series FPGAs Transceivers Wizard - Page 1

When implementing only an SDI receiver or only an SDI transmitter, the **TX off** or **RX off** check boxes on this page can be used to disable the unneeded portion of the transceiver. The ports for the unused portion of the transceiver do not appear on the GTX wrapper and that portion of the transceiver is powered down. However, the **TX off** and **RX off** selections apply to all transceivers included in the GTX wrapper. Thus, if some transceivers need both RX and TX and others need only the RX or only the TX, the **TX off** and **RX off** check boxes cannot be used. In these cases, the GTX wrapper must be created with the RX and TX sections of all transceivers enabled. The RX and TX units that are not needed can be individually powered down by selecting the **RXPOWERDOWN** and **TXPOWERDOWN** ports from the **Optional Ports** list on page 5 of the Wizard (Figure 15). This adds the ports that enable the power down mode for the RX and TX to each transceiver in the wrapper.

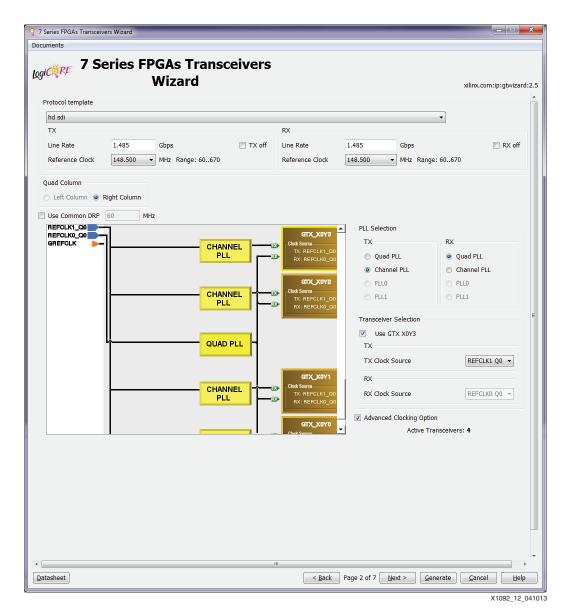

Move to page 2 of the Wizard by clicking the **Next** > button at the bottom of the page. Page 2 of the Wizard allows the user to select which transceivers are included in the GTX wrapper (see Figure 12).

Figure 12: 7 Series FPGA Transceivers Wizard - Page 2

Usually, the Common DRP (the DRP for the GTXE2\_COMMON block containing the QPLL) is not required for SDI applications, so the **Use Common DRP** check box can be unchecked.

Select the GTX transceivers to be included in the GTX wrapper. Also select the PLL for the RX and TX portions of each transceiver. Typically, QPLL is used for all receivers and CPLLs are used for each transmitter. The reference clock source for each PLL can also be made here.

The PLL selection affects how the GTX wrapper is created. For the RX section, which typically has a static PLL selection in SDI applications, the attribute that specifies whether the clock comes from the QPLL or the CPLL is determined by the PLL selection made on this page for each transceiver. Typically, the QPLL is used as the clock source for all RX units in SDI applications. For the TX section, many SDI applications require dynamic switching between the QPLL and the CPLL as controlled by the TXSYSCLKSEL port. Thus, the PLL selection for the TX units does not really matter as far as the GTX wrapper is concerned. However, if an SDI application does not require dynamic switching between the QPLL and the CPLL, the PLL to be used for each TX unit should be specified correctly on this page, and the TXSYSCLKSEL port should be unselected on page 3 of the Wizard (Figure 13). When this is done, the PLL assignments made in the Wizard are statically implemented in the GTX wrapper.

The reference clock sources to the PLLs made on this page do not affect the way the GTX wrapper is created. They only affect the example design that is also created by the Wizard. If the example design is to be used as the starting point for the application, the reference clock sources should be set correctly. Otherwise, it does not matter.

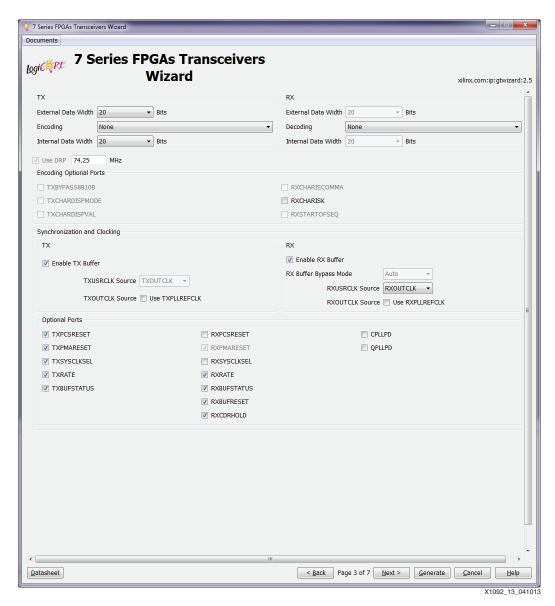

Move to page 3 of the Wizard by clicking the **Next** > button at the bottom of the page (Figure 13). The external and internal data widths are already correctly set to **20 Bits** and the encoding and decoding are already correctly set to **None**.

Figure 13: 7 Series FPGA Transceivers Wizard - Page 3

The control module does require a DRP port on each transceiver to dynamically change some of the transceiver's attributes when the transceiver is switched between SDI modes. Thus, the **Use DRP** check box must be selected, and the frequency of the DRPCLK must be correctly specified. In this example, the DRPCLK frequency is set to **74.25 MHz**. Any free-running clock available in the design can be used as the DRPCLK as long as it meets the frequency requirements as specified by FGTXDRPCLK in *Zynq-7000 All Programmable SoC (XC7Z030, XC7Z045, and XC7Z100): DC and AC Switching Characteristics* (DS191). The frequency of the clock source driving the DRPCLK should not change when the SDI mode changes. It should

remain at a constant, fixed frequency at all times, and that frequency must be specified here on Page 3 of the Wizard.

Xilinx recommends that the TX and RX buffers both be enabled. Bypassing these buffers is not supported by the control module included with this application note.

All optional ports selected on this page by default when the hd sdi protocol template was chosen are required for SDI applications with one possible exception. **TXSYSCLKSEL** is normally used to allow the TX unit to be dynamically switched between the QPLL and the CPLL. If this is not required, the **TXSYSCLKSEL** port can be unselected, and the PLL selection for the TX units in the wrapper are specified on page 2 of the Wizard (Figure 12).

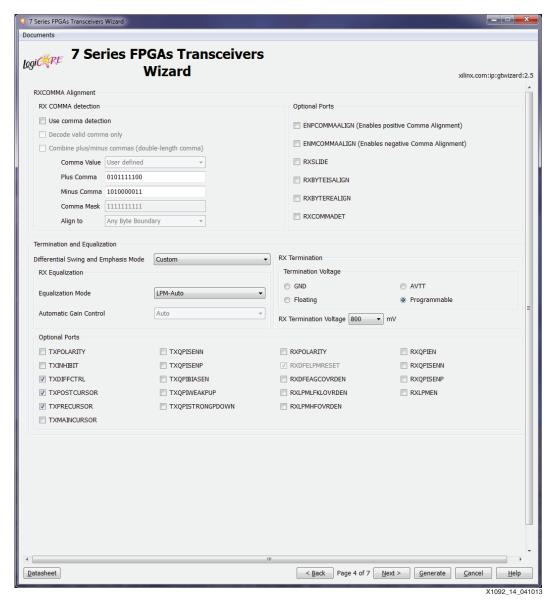

Move to page 4 of the Wizard by clicking the **Next** > button at the bottom of the page (Figure 14).

Figure 14: 7 Series FPGAs Transceivers Wizard - Page 4

Verify that all selections on this page are as shown in Figure 14. In particular, **Use comma detection** and the **RXSLIDE** port should not be selected. Some versions of the Wizard (including version 2.4) have a bug that causes the **Use comma detection** and **RXSLIDE** selections to be re-enabled when certain changes are made on other pages of the Wizard. So

always check that **Use comma detection** and **RXSLIDE** are not selected after making any changes to settings on other pages of the Wizard.

Xilinx recommends that **Equalization Mode** be set to **LPM-Auto** for SDI applications.

The **RX Termination** must use the **Programmable** termination voltage with **RX Termination Voltage** set to **800 mV**.

The **TXDIFFCTRL** optional port can be enabled if control of the differential swing at the output of the GTX TX is required. Likewise, **TXPOSTCURSOR** and **TXPRECURSOR** can be enabled if those ports are required to improve the signal quality between the GTX TX output and the input of the SDI cable driver.

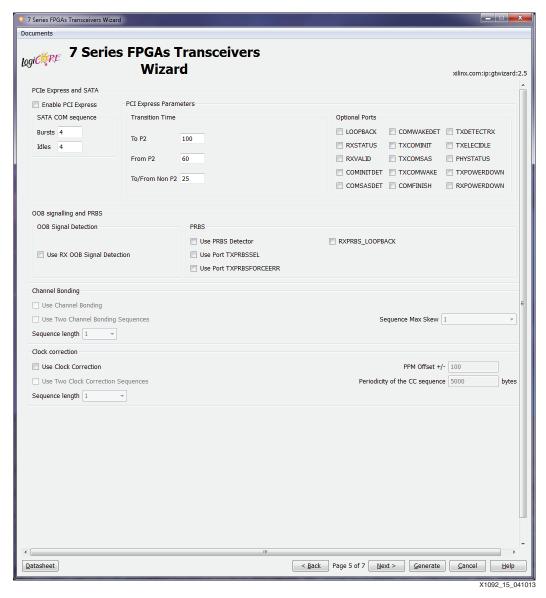

Move to page 5 of the Wizard by clicking the **Next** > button at the bottom of the page (Figure 15).

Figure 15: 7 Series FPGAs Transceivers Wizard - Page 5

If loopback testing of the transceivers is desired, the optional **LOOPBACK** port can be enabled. The **TXPOWERDOWN** and **RXPOWERDOWN** ports can be enabled if the applications need power-down control over each individual RX and TX unit. Otherwise, none of the optional ports should be selected.

At this point, all selections necessary for creating a GTX wrapper for SDI applications have been made. Page 6 of the Wizard does not apply to SDI, and page 7 is just a summary page. The user can either move through those pages using the **Next** > button or generate the GTX wrapper from this page using the **Generate** button at the bottom of the page.

The Wizard generates a number of files. The two important files are called <component\_name>.v/vhd and <component\_name>\_gt.v/vhd. In this example, the component name is z7gtx\_sdi\_wrapper, as can be seen near the top of page 1 of the Wizard in Figure 11. In this example, Verilog was set as the preferred language. Thus, the two important files created by the Wizard are named z7gtx\_sdi\_wrapper.v and z7gtx\_sdi\_wrapper\_gt.v.

The <component\_name> file is the top-level wrapper file, the one that must be instantiated into the SDI application. The <component\_name>\_gt file is a wrapper file for a single GTX transceiver. It is instantiated one or more times in the <component\_name>.v wrapper file depending on how many transceivers are included in the GTX wrapper.

**Note:** The example design generated by the Wizard is not particularly useful for SDI applications. The example designs provided by this application note are usually better starting points for an SDI application.

# Generating the SMPTE SD/HD/3G-SDI LogiCORE IP

Use the CORE Generator tool or the Vivado IP catalog to generate the SMPTE SD/HD/3G-SDI core. Do not use the older Triple-Rate SDI core, which is only for Virtex®-6 FPGAs. The SMPTE SD/HD/3G-SDI core is the generic SDI core that works with 7 series devices.

The SMPTE SD/HD/3G-SDI core is a source code core, not a precompiled core. When the CORE Generator tool generates the SMPTE SD/HD/3G-SDI core, it delivers a set of source code files in either Verilog or VHDL, depending on project's preferred language setting.

The only option available when generating the SMPTE SD/HD/3G-SDI core is whether or not to include the error detection and handling (EDH) processor for the RX section. Even if the RX EDH processor is not included, the SDI core has all RX EDH ports, but they are inactive.

The SMPTE SD/HD/3G-SDI core is instantiated in the SDI wrapper. Thus, if the SDI wrapper is used, the SMPTE SD/HD/3G-SDI core itself does not need to be directly instantiated in the application.

# Instancing the GTX and SDI Wrappers

The GTX and SDI wrappers need to be instantiated and interconnected in the user design. It is possible to implement the SDI interface without the SDI wrapper supplied with this application note, but the wrapper makes things easier because it interconnects the SDI control module and the SDI core. If the wrapper is not used, the user must make all of these connections. The SDI wrapper file is called  $x7gtx\_sdi\_rxtx\_wrapper.v$  (Verilog version) or  $x7gtx\_sdi\_rxtx\_wrapper.v$ hd (VHDL version). In addition to the SDI core, it also instances these files:

- x7gtx sdi control.v/vhd

- x7gtx\_reset\_control.v/vhd

- x7gtx\_sdi\_drp\_control.v/vhd

- sdi rate detect.v/vhd

- dru bshift10to10.v/vhd

- dru\_maskencoder.v/vhd

- dru\_control.v/vhd

- dru\_rot20.v/vhd

- dru.v (Verilog only)

# Add the dru.ngc File to the Project

The  $\mathtt{dru.v}$  file is an empty module which, in Verilog, specifies the ports on the precompiled  $\mathtt{dru.ngc}$  file. When using the  $\mathtt{x7gtx\_sdi\_rxtx\_wrapper.v}$  file, the  $\mathtt{dru.v}$  file must be included in the project. When using the  $\mathtt{x7gtx\_sdi\_rxtx\_wrapper.vhd}$  VHDL file, the component definition serves the same purpose as the  $\mathtt{dru.v}$  file, thus the  $\mathtt{dru.v}$  file is not required.

When using the ISE tools, the  $\mathtt{dru}.ngc$  file included with this application note must be moved into the ISE tools project directory where the tools can find and include it in the design. When using the Vivado tools, the  $\mathtt{dru}.ngc$  file must be added to the project as a source file just like adding any of the Verilog or VHDL files. The  $\mathtt{dru}.ngc$  file is the pre-generated and encrypted DRU module.

**Caution!** Do not use the dru\_sim.v or dru\_sim.vhd files that are included with this application note in a design intended to be used in the actual FPGA. These files are for simulation purposes only. Using them in an actual hardware implementation results in an SDI receiver that is not able to correctly receive SD-SDI signals. For simulation purposes, the dru\_sim.v/vhd files can be added to the design instead of the dru.v file and the dru.ngc file.

**IMPORTANT**: The SDI wrapper contains an instance of the SMPTE SD/HD/3G-SDI core. The SDI wrapper must be edited so that the name given to the SDI core (when it is generated using the CORE Generator tool or the Vivado IP catalog) is used where the core is instanced in the SDI wrapper. This can be avoided by using the component name *smpte\_sdi* when generating the SMPTE SDI core.

Table 1 describes all of the ports of the SDI wrapper. This port list is similar to the port list of the SDI core itself, but there are some differences. Also refer to the example SDI applications provided with this application note for examples of how to interconnect the GTX and SDI wrappers.

Some signals are described as being asserted for some number of video sample periods. A video sample period lasts for differing numbers of cycles of the appropriate clock (either tx\_usrclk or rx\_usrclk) depending on the SDI mode. In HD-SDI and 3G-SDI level A modes, a sample period lasts one clock cycle. In SD-SDI mode, a sample period is either 5 or 6 clock cycles long and begins and ends with the rising edge of the clock when the clock enable (either tx\_ce or rx\_ce\_sd) is asserted. In 3G-SDI level B mode, a sample period is two clock cycles long as controlled by the assertion of the 3G-SDI data ready signal (either tx\_din\_rdy or rx\_dout\_rdy\_3G).

Most of the RX and TX ports in this list are wired directly to the ports of the same name on the SDI core that is instantiated inside the SDI wrapper. Timing diagrams of the video and video timing signals can be found in *Society of Motion Picture and Television Engineers (SMPTE)* SD/HD/3G-SDI Product Guide [Ref 6].

Table 1: SDI Wrapper Port List

| Port Name | I/O | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cik       | In  | 1     | This input must be connected to a fixed-frequency free running clock. This clock is used by the SDI wrapper for various timing purposes. The frequency of this clock must be specified by the parameter/generic FXDCLK_FREQ. If the clock frequency does not closely match the frequency specified by FXDCLK_FREQ, the timing delays generated by the wrapper are not correct and the RX bit rate detection circuit might not function. |

Table 1: SDI Wrapper Port List (Cont'd)

| Port Name     | I/O | Width | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive Ports |     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| rx_rst        | In  | 1     | This synchronous reset input can normally be hardwired Low because a reset is not required. After FPGA configuration, the SMPTE SDI core is in a fully operational mode and does not require a reset.  Both rx_ce_sd and rx_din_rdy_3G must be High when rx_rst is High to completely reset the receiver.  Asserting rx_rst also resets the state machine that controls the automatic SDI mode lock detector. Do not assert rx_rst just because the SDI RX is not locked, otherwise the SDI RX never locks.                                                                                                                                                                                                                                                                                                                                            |

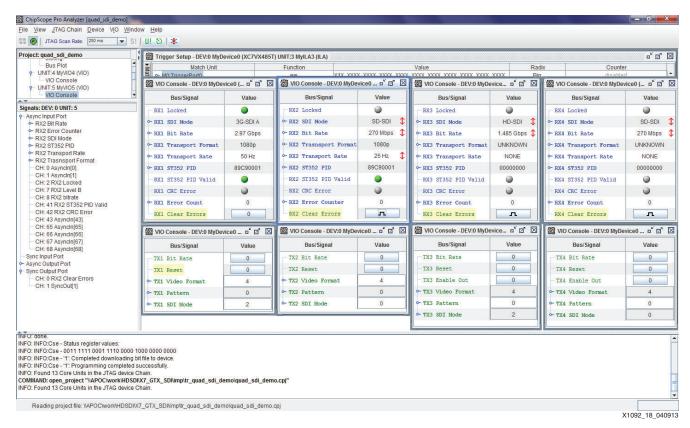

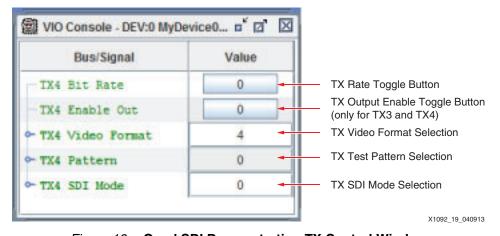

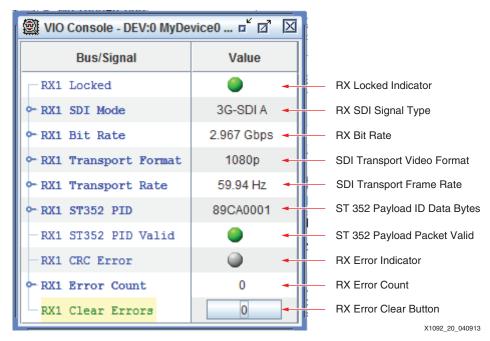

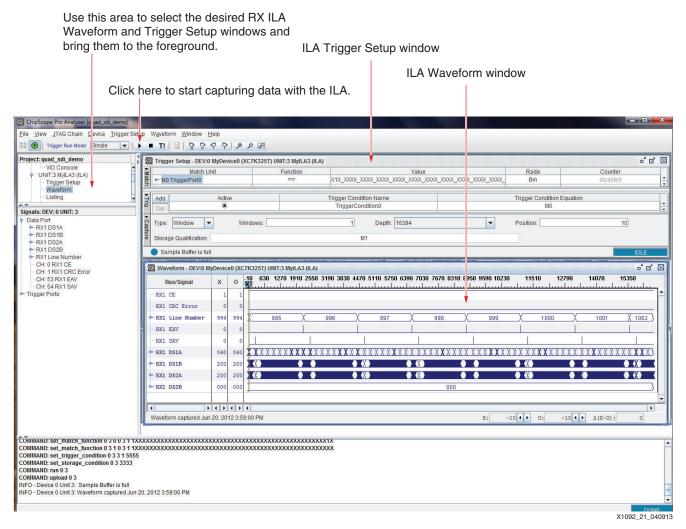

| rx_usrclk     | In  | 1     | This input connects to the recovered clock from the transceiver's RX unit: the RXOUTCLK output of the GTX transceiver buffered by a global clock buffer. The clock frequency must be 148.5 MHz (or 148.5/1.001 MHz) for 3G-SDI and SD-SDI modes. It must be 74.25 MHz (or 74.25/1.001 MHz) for HD-SDI mode. All input and outputs of the wrapper prefixed with <i>rx</i> _ are synchronous with this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                            |